(54) ПЕРЕСТРАИВАЕМОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

второго и первого коммутаторов, вторые входы первого и второго элементов И соединены соответственно с единичньоми выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первого регистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционные выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является операционным выходом устройства, адресные выходы первого и второго запоминающих блоков соединены соответственно с третьими входами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов.

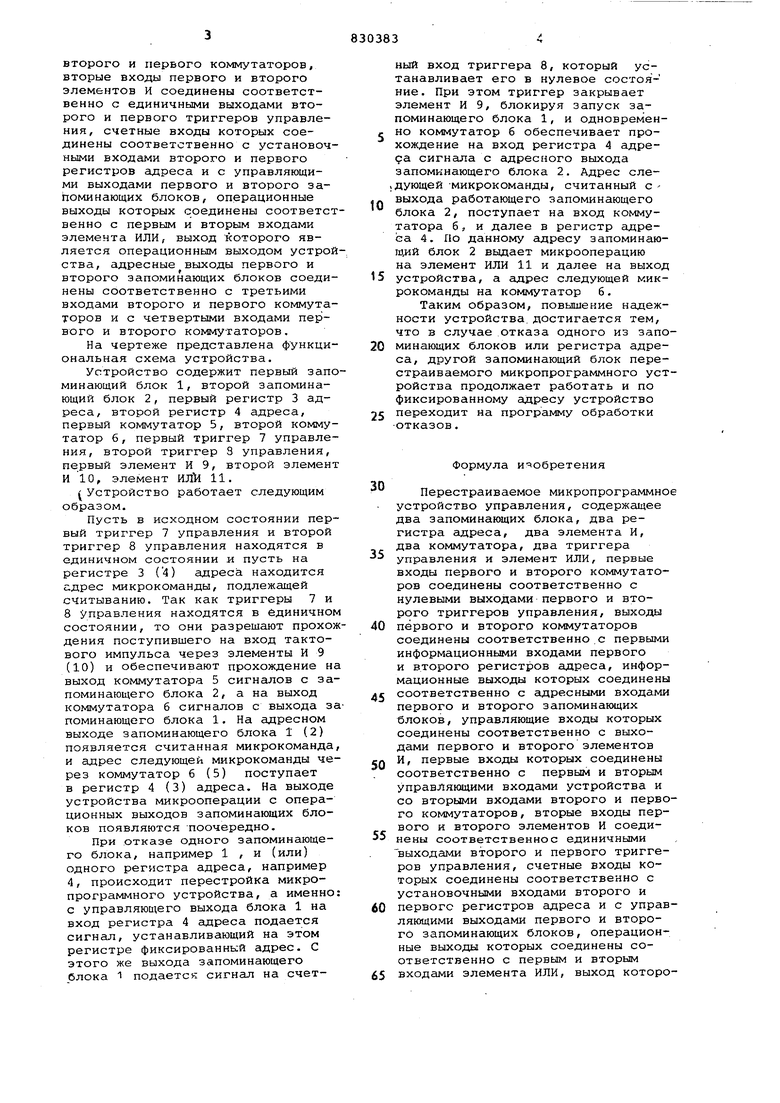

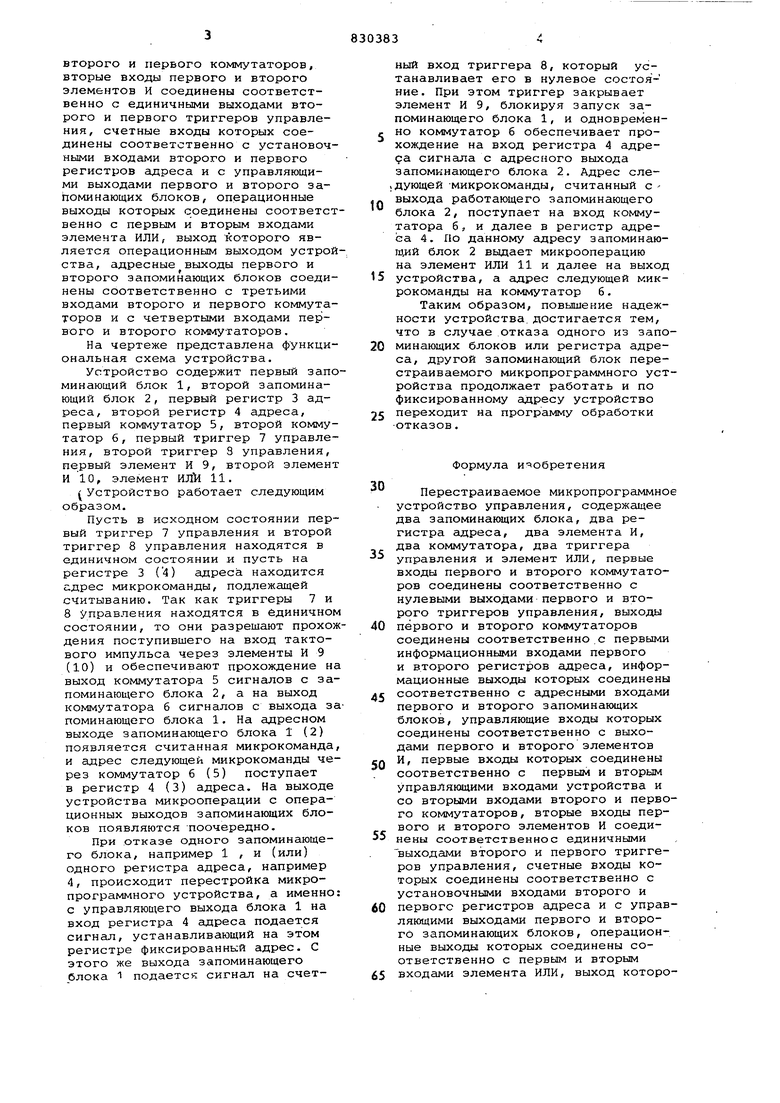

На чертеже представлена функциональная схема устройства.

Устройство содержит первый запоминающий блок 1, второй запоминающий блок 2, первый регистр 3 адреса, второй регистр 4 адреса, первый коммутатор 5, второй коммутатор 6, первый триггер 7 управления, второй триггер 3 управления, первый элемент И 9, второй элемент И 10, элемент ИЛИ 11.

Устройство работает следующим образом.

Пусть в исходном состоянии первый триггер 7 управления и второй триггер 8 управления находятся в единичном состоянии и пусть на регистре 3 (4) адреса находится адрес микрокоманды, подлежащей считыванию. Так как триггеры 7 и 8 управления находятся в единичном состоянии, то они разрешают прохождения поступившего на вход тактового импульса через элементы И 9 (10) и обеспечивают прохождение на выход коммутатора 5 сигналов с запоминающего блока 2, а на выход коммутатора б сигналов с выхода запоминающего блока 1. На адресном выходе запоминающего блока 1 (2) появляется считанная микрокоманда и адрес следующей микрокоманды через коммутатор б (5) поступает в регистр 4 (3) адреса. На выходе устройства микрооперации с операционных выходов запоминающих блоков появляются поочередно.

При отказе одного запоминающего блока, например 1 , и (или) одного регистра адреса, например 4, происходит перестройка микропрограммного устройства, а именно с управляющего выхода блока 1 на вход регистра 4 гщреса подается сигнал, устанавливающий на этом регистре фиксированный адрес. С этого же выхода запоминающего блока 1 подается сигнал на счетный вход триггера 8, который устанавливает его в нулевое состояние. При этом триггер закрывает элемент И 9, блокируя запуск запоминающего блока 1, и одновременно ко(«в лутатор б обеспечивает прохождение на вход регистра 4 адре а сигнала с адресного выхода запоминающего блока 2. Адрес сле;дующей -микрокоманды, считанный с выхода работающего запоминающего блока 2, поступает на вход коммутатора 6, и далее в регистр адреса 4. По данному адресу запоминающий блок 2 выдает микрооперацию на элемент ИЛИ 11 и далее на выход устройства, а адрес следующей микрокоманды на коммутатор б.

Таким образом, повышение надежности устройства, достигается тем, что в случае отказа одного из запоминающих блоков или регистра адреса, другой запоминающий блок перестраиваемого микропрограммного устройства продолжает работать и по фиксированному адресу устройство переходит на программу обработки отказов.

Формула изобретения

Перестраиваемое микропрограммно устройство управления, содержащее два запоминающих блока, два регистра адреса, два элемента И, два коммутатора, два триггера управления и элемент ИЛИ, первые входы первого и второго кo мyтaтoров соединены соответственно с нулевыми выходами первого и второго триггеров управления, выходы первого и второго коммутаторов соединены соответственно с первьлми информационными входами первого и второго регистров адреса, информационные выходы которых соединены соответственно с адресными входами первого и второго запоминающих блоков, управляющие входы которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым и вторым управляющими входами устройства и со вторыми входами второго и первого коммутаторов, вторые входы первого и второго элементов И соединены соответственное единичными выходами второго и первого триггеров управления, счетные входы которых соединены соответственно с установочными входами второго и первого регистров адреса и с управляющими выходами первого и второго запоминающих блоков, операционные выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является операционным выходом устройства, отличающееся тем, что, с целью повышения надеж.ности, адресные выходы первого и второго запоминающих 6jiOKOB соеди.нены соответственно с третьими входами второго и первого коммутаторов и с четвертыми входами первого и второго коммутаторов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 451080, кл. G 06 F 9/12, 1972.

2.Авторское свидетельство СССР 646333, «л. G 06 F 9/12, 1976 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

Bbixfff

Авторы

Даты

1981-05-15—Публикация

1979-06-13—Подача