(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1977 |

|

SU943727A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130866A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении ЦВМ сред него быстродействия.

Известна многопроцессорная цифровая вычислитепьная машина, содержащая устройство центрапизованного управления работой процессоров, которс5е посылает общие команды подмножеству общего множества процессора, регистр моды дня регистрации состошшй процессоров, анализируемых .устройствами дентрализованного управления, и регистр маски,, управляемый этим устройством и опредепяющий подмножество процессоров, выпопня1ощих общую команду l.

Наиболее близким по техническому решению к предложенному устройству является микропрограммное устройство управления, содержащее блок памяти микропрограмм, Л операционных блоков, ц, регистров микрокоманд н h регистров состояний, п ричем ционные выходы блока памятн микррпрограмм соединены с информационными I входами П регистров макрокоманд, информационные выходы каждого из которых подключены к .йнффмационным входам одноименного операционного блока, управляющий выход каждого регистра микpokoмaнд соединен с управляющим входом одноименного perncTfia состодагая, информационные входы каждого из.которых соединены с информационными выходами одноименного операционного блока, информационные выходы П регистров состояния соединены с информационными входами блока памгагти микропрограмм.

5

В известно. устройстве все параллельно работающие операционные блоки запускаются одновременно, общей микрокомандой.

0

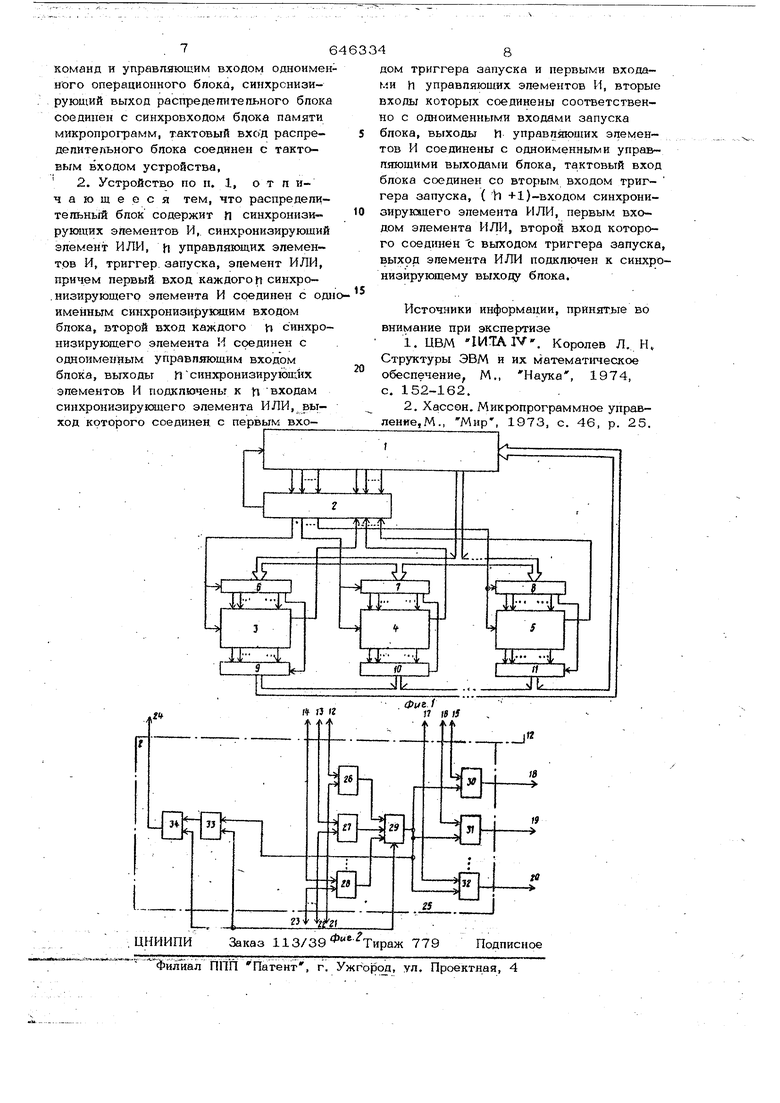

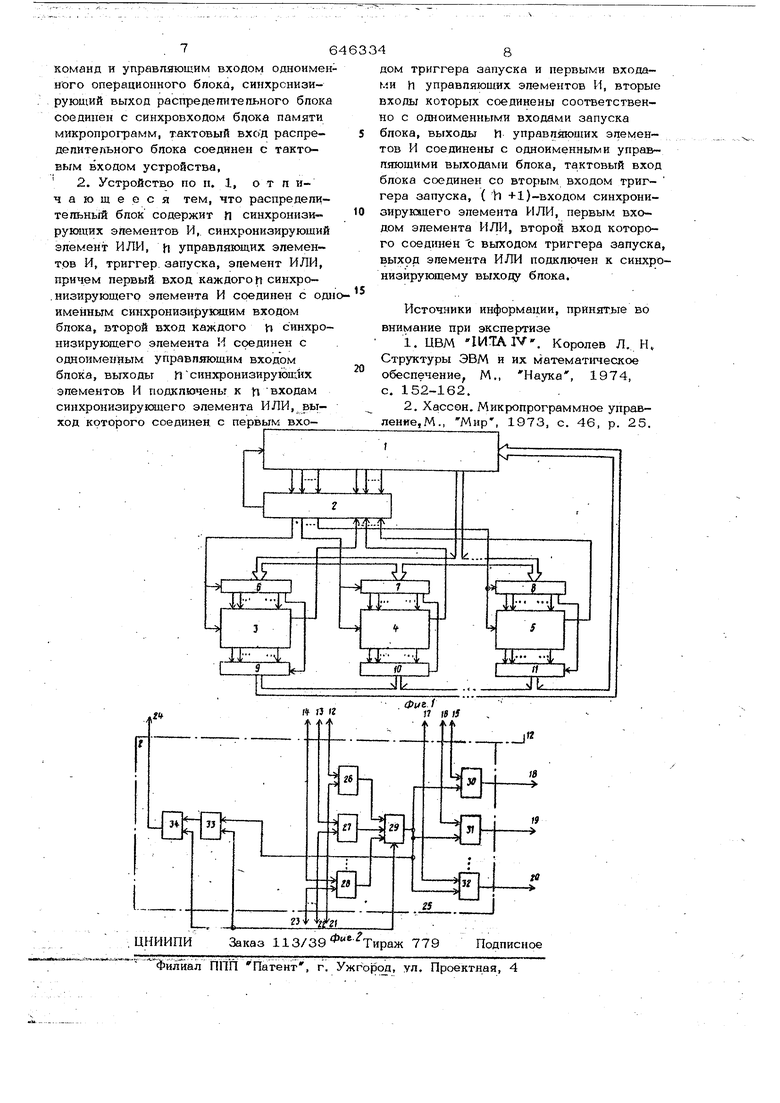

При этом общий формат микрокоманды шределяется суммарным числом микроприказов яяя всех запускаемых устройс гв. В ЦВМ со средним нпи мапым быстродействием допустимы режимы работы, когда возможна выдача одновременных микроприказов не всем уст ройствам, могущим работать одновременно, а лишь некоторой их части. Недостатком известного устройства в этих режимах явпяетс.я бопьшой объем памяти микропрограмм из-за неиспопьзования попей микрокоманды, предназначенных для управпения незапускаемых устройств. Цепь предлагаемого изобретения сокращение оборудования. Для этого в дфедпагаемое устройст введен распределительный бпок, синхоо ннзнрующи х входов которого подключено к синхронизирующим .выходам блока памяти микропрограмм, запускающие вьг«ходь которого соединены с И рходами эаг1 ска распределительного блока, YI . управляющих входов которого соединены соответственно с управляющими выходами операционных бликов, каждый из 1 управлхпощих выходов распределительног блока соединен с управлззющим входом одноименного регистра микрокоманд и управляющим входом одноименного операционного блока, синхронизирующий выход распределительного блока соединен: с синхровходом блока памяти микропрограмм, тактовый вход распределительного блока соединен с тактовы входом устройства, причем распределительный 6fiOK содержит 51 сийхронизиДующих элементов И, синхронизирующий элемент ИЛИ, п управляющих элементов И, триггер запуска, элемент ИЛИ, причём первый вход каждого Я сишфонизирующего элемента И соединен с одноименным синхронизирующим входом блока, второй вход каждого Ц синхронизирующего эпемента И соединен с. одноименным управляющим входом блока ВЫХОДЫ 11 синхронизирующих эле ментов И подключены к h входам синхронизирующего элемента ИЛИ, выход которого соедзшен с первым входом триггера запуска и первыми входами П управляющих элементов И, вторые входы которых соединены соответственно с одноименными входами запуска блока, выходы h управляйюшвк элементо И соединены с Одноименными управ шпо щими выходами блока, тактовый вход блока соединен со вторым входом триг гер;а запуска, ( И+1)-входом синхрониаирующего элемента ИЛИ, первым входом элемента ИЛИ, второй вход которо го с выходом триггера запуска, выход эпемента ИЛИ подключен к синхронизирующему выходу блока. Общая блок-схема предлагаемого устройства показана на,фиг, 1. На фиг. 2 приведена структурная схема распределительного блока 2. Блок схема содержит: блок 1 памяти микропрограмм, рас11ределительнь й блок 2, операционные блоки 3, 4, 5, регистры 6-8 микрокоманд, регистры 9-11 состояний. Структурная схема распредепительного блока 2 содержит синхронизирующие входы 12, 13, 14, входы запуска 15, 16, 17 управЛ5пощие выходы 18, 19, 2О, управляющие входы 21, 22, 23 синхронизирующий выход 24, тактовый вход 25 устройства, синхронизирующие 26, 27, 28 элементы И, синхронизирующий элемент ИЛИ 29, управляющие,30, 31, 32 элементы И, триггер запуска 33, элемент 34 ИЛИ. Рассмотрение работы устройства удобно начать с момента когда блоком 1 памяти микропрограмм выработана для исподаения очередная микрокоманда. Обозначим символами S,..- Sj, микроприказы синхронизации в поле микрокоманды, поступающие на синхронизирукнцие входы 12, 13, 14 распределительного блока, причем п - число операционных блоков: - О, если Данная микрокоманда должна исполняться после завершения работы 1-м операционным бло - 1, если момент включения данной микрокоманды на исполнение не зависит от состояния i-ro операционного блока. Символами f. I.. f, обозначим состояния управляющих выходов операционных блоков: -О, если. 1-й операционный блок занят выполнением ранее поданной микрокоманды (не обязательно дредыдушей)| . 1- 1-й операционный блок работу закончил. 2 Символами Rij... Р обоэаачим микро приказы, в поле запуска микрокоманды находятся запускающие выходы бпока памяти микропрограмм: ( О, если 1 -и операционный блок данную микрокоманду не исполняет 1- в противном случае Симвопами Y.,. . у, обозначим состояния управтшющих выходов распредетгатепънрго блока. Р предикат запуска в распредепитерном бпоке. PHS:,)A...( где V -операция дезъюнкдии; д -операция конъюнкции. Один иа операционных блоков будет вкш чен на исполнение данной микрокоманды еспи , ЛРийеет значение 1 для выработанной микрокоманды. Устройство микропрограммного управ (гения находится в состоянии ожидание до тех пор, пока Р не примет значение , Затем выбранная микрокоманда передается на исполнение операционным блокам, дпя которых Y. и блок 1 памяти микропрог замм запускается на выбор очереднЪй микрокоманды. Количество ( П ) синхро1низирующпх 26-28 элементов И и управ/1яющих ЗО32 элементов И определяется числом операционных блоков, синхронизирующий элемент .ИЛИ 29 селектируется тактовым входом 25 устройства, самым обеспечивается выдача сигнала запуска операдионным блокам именно в этот такт, . На выходе сиахронизирующего элемента 32 вырабатывается значение предиката Р распредепитепйного блока 2« На выходгэ х упраэпяаощих элементов 30-32 Шрабатываются значения Y - управляю щего сигнала запуска операционньЬс блоков. На триггере запуска 33 запомийается значение Р, выработанное элементом 29, В момент подачи такта Т вход 25 устройства в бпок 1 на синхро низирующий вход подается сигнал получения следующей микрокоманды, если в этот момент состояние триггера 33-1 (т. е. по предыдущей микрокоманде Указанные преимущества предлагаемого устройства микропрограммного , . управления достигаются за счет того, что в него введен распределительный блок, синхронизирувлций во времени работу операцио1шьгх блоков и блока памя ти микропрограмм, В формате микрокоманды имеется два специальных поля микроприказов: синхронизации н запуска Мйкроприказы в поле синхронизации определяют список операционных блоков, после завершения работы которых должна исполняться данная микрокоманда. Микроприказы в поле запуска определяют список операционных блоков, которым предназначается данная микрокоманда. Выходы синхронизации и запуска блока памяти микропрограмм подсоединены к соответствующим входам распределительного блока, имеющего, помимо этого, управляклцие входы окончания работы операционных блоков. Предлагаемое изобретение дает эко- . номический эффект, заключающийся в экономии оборудования цифровой вычислительной мащины, в частности, за счет, сокращения размера поля микрокоманды и уплотнения информации в блоке памяти микропрограмм. Формула йзобр. ете i. Устройство микропрограммного управления, содержащее блок микроПрограмм, И операционных блоков, и регистров микрокоманд и м регистров состояния, информационные выходы блока паМ5гги микропрограмм соединены с информационными входами ti регистров микроко «анд, информационные выходы каждого из которых подключены к информационным входам одноименного операционного блока, управляющий выход каждого регистра микрокоманд соединен с управляющим входом одноименного регистра состояния, информационные входы каждого из которых соед 1нены с информационными выходами одноименного операционного бпока, информационные выходь Л регистров состояния соединены с информационными входами блока памяти микропрограмм, отличающееся тем, что, с целью сокращения оборудования, в устройство введен распределительный блок h - сипхрогшаирующих входов которого подкггючено к синхронизирующим вь1ходамг блока памяти микропрограмм, запускающие выходы которого соединены с si входами запуска распределительного блока, И управляющих входов которого соединены соответственно с управляющими выходами операционных блоков, каждый КЗ И управляющих выходов распределительного блока соединен с управляющим входом одноименного регистра микрокоманд и управляющим входом одноиме ного операционного блока, синхронизирующий выход распредет1тепьного блок соединен с синхровходом бдока памяти микропрограмм, тактовый вход распредепитепьного бпока соединен с тактовым входом устройства, 2. Устройство по п. 1, о т п ичающееся тем, что распределите льный блок содержит п синхронизирующих элементов И, синхронизирующий элемент ИЛИ, h управляющих элементов И, триггер, запуска, элемент ИЛИ, причем первый вход каждого и синхро.низирующего элемента И соединен с од именным синхронизнрукяцим входом блока, второй вход каждого h синхро низирующего элемента И соединен с одноименным управляющим входом блока, выходы Цсинхронизирующих элементов И подключены к П входам синхронизирукянего элемента ИЛИ, выход которого соединен с первым вхо- дом триггера запуска и первыми входами И управляющих элементов И, вторые входы которых соединены соответственно с одноименными входами запуска блока, выходы И управляющих элементов И соединены с одноименными управляющими выходами блока, тактовый вход блока соединен со вторым входом триггера запуска, ( h +1)-входом синхронизирующего элемента ИЛИ, первым входом элемента ИЛИ, второй вход которого соединен с выходом триггера запуска, выход элемента ИЛИ подключен к синхронизирующему выходу блока. Источники информации, принягг.ые во внимание при экспертизе 1.ЦВМ IMIIAIV. Королев Л, Н. Структуры ЭВМ и их математ1гческое обеспечение, М,, Наука, 1974, с. 152-162. 2.Хассон. Микропрограммное управление.М., Мир, 1973, с. 46, р. 25.

Авторы

Даты

1979-02-05—Публикация

1976-06-21—Подача