вым входом блока элементов И, второй вход которого соединен с управляющим входом коммутатора микрокоманд и с выходом признака анализа логических условий регистра микрокоманд, выход блока элементов И соединен с информационным входом регистра логических условий.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

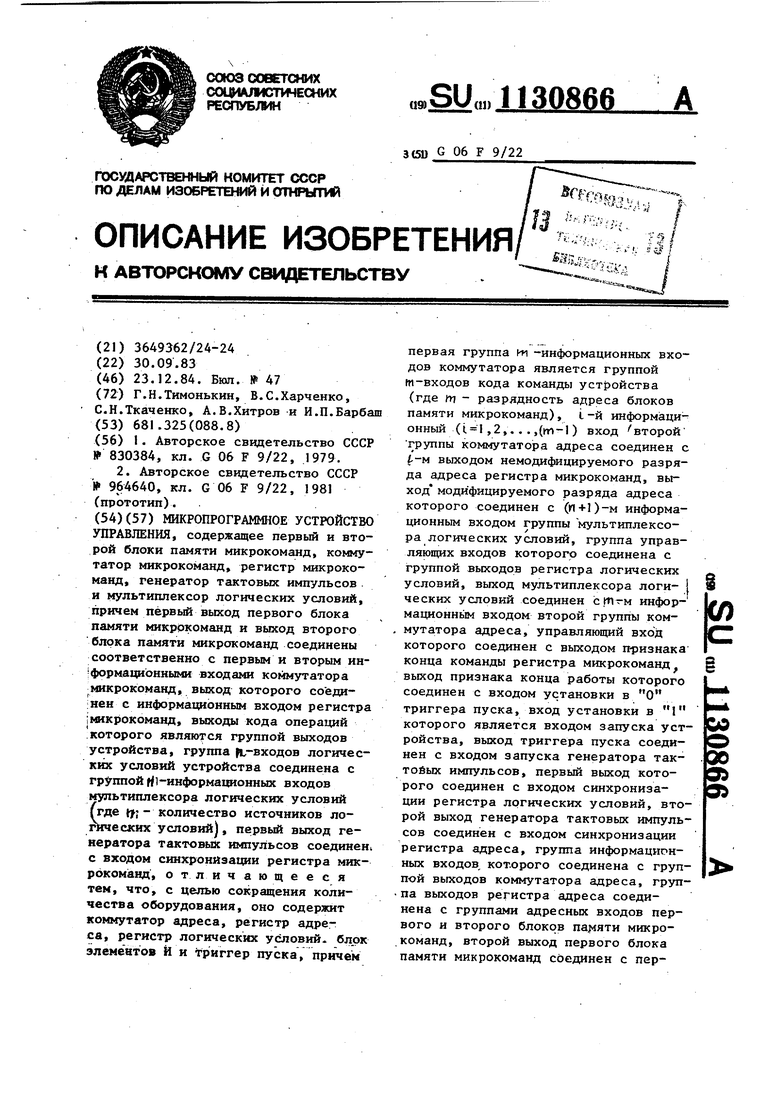

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, коммутатор микрокоманд, регистр микрокоманд, генератор тактовых импульсов . и мультиплексор логических условий, причем первый выход первого блока памяти микрокоманд и выход второго блока памяти микрокоманд соединены соответственно с первым и вторым ин|форма1Ц1онными входами коммутатора микрокоманд, выход которого соеди:нен с информахщонным входом регистра ;микрокоманд, выходы кода операций которого являются группой выходов устройства, группа fL-входов логических условий устройства соединена с группой Hi-информационных входов мультиплексора логических условий (где г - количество источников логических условий, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд, отличающееся тем, что, с целью сокращения количества оборудования, оно содержит коммутатор адреса, регистр адреса, регистр логических условий блок элементов И и триггер пуска, причем первая группа И1 -информационных входов коммутатора является группой m-входов кода команды устройства (где fn - разрядность адреса блоков памяти микрокоманд), L-и информационный ( ,2,. .. ,(in-l ) вход второй группы коммутатора адреса соединен с -м выходом немодифицируемого разряда адреса регистра микрокоманд, выход модифицируемого разряда адреса которого соединен с (л+1)-м информационным входом группы мультиплексора логических условий, группа управляющих входов которого соединена с группой выходов регистра логических условий, выход мультиплексора логических условий соединен ст-гм информацнонным входом второй группы коммутатора адреса, управляющий вход которого соединен с вьпсодом признака конца команды регистра микрокоманд выход признака конца работы которого соединен с входом установки в О триггера пуска, вход установки в 1 СО которого является входом запуска устО СХ) ройства, выход триггера пуска соединен с входом запуска генератора так9) 3d товых импульсов, первый выход которого соеданен с входом синхронизации регистра логических условий, второй выход генератора тактовьк импульсов соединен с входом синхронизации регистра адреса, группа информационных входов, которого соединена с группой выходов коммутатора адреса, группа выходов регистра адреса соединена с группами адресных входов первого и второго блоков па;4яти микрокоманд, второй выход первого блока памяти микрокоманд соединен с пер

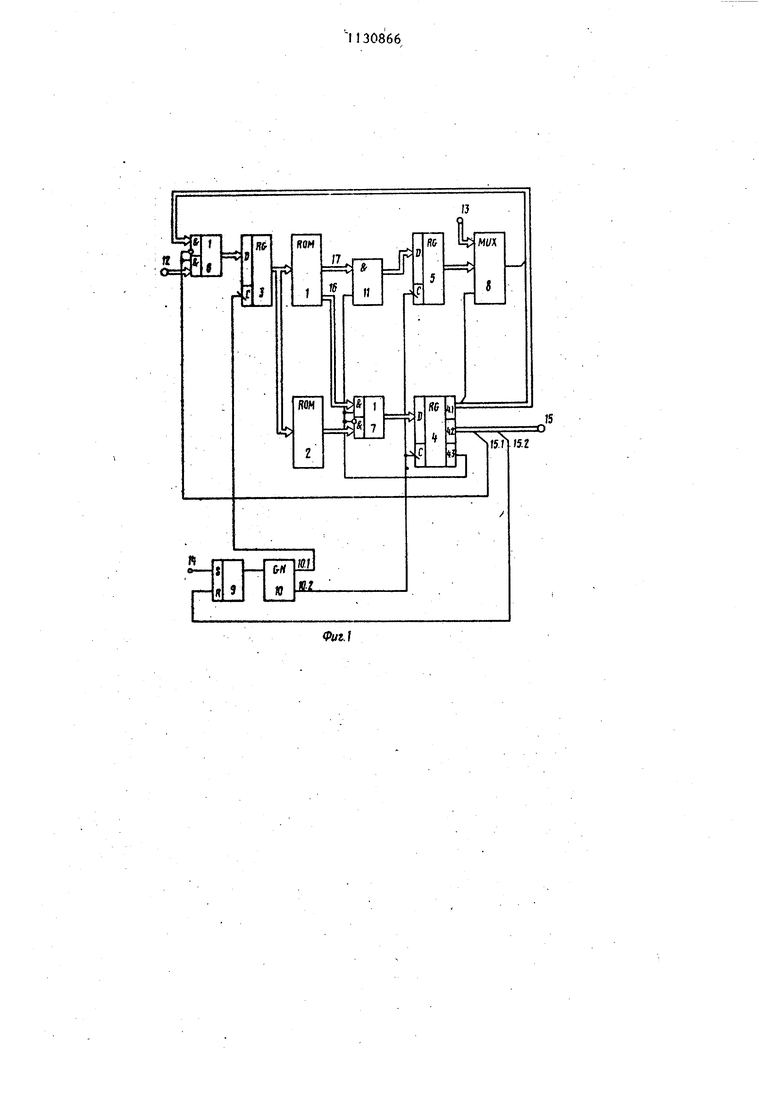

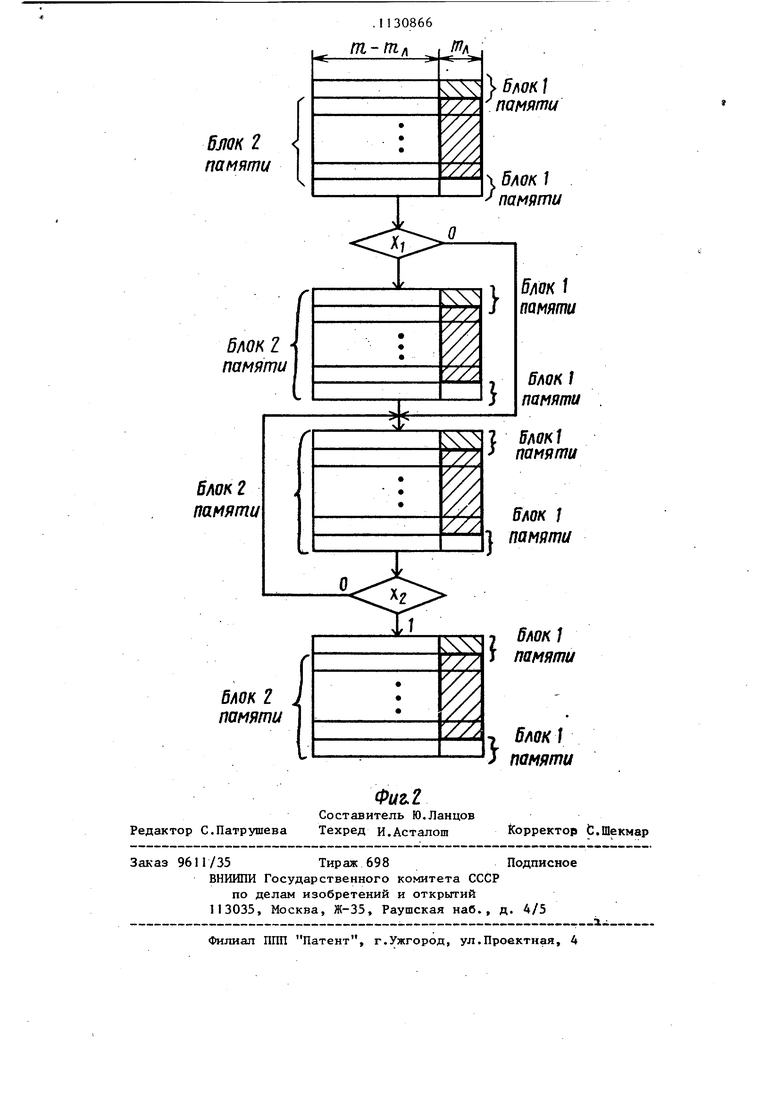

Изобретение относится к автома.тике и вычислительной технике и может быть использовано при построеЬши управляющих устройств ЭВМ и вычислительных систем с микропрограммным управлением. Известно, микропрограммное устройство управления, содержащее регистр адреса, первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, формирователь ад реса С 1 . Недостатком устройства является большой объем оборудования блока пам ти, обусловленный наличием свободных полей микрокоманд. Наиболее близким к предлагаемому изобретению по технической сущности и достигаемому эффекту является микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, коммутатор, регистр микрокоманд, мультиплексор. Причем вход логических условий .устройства и первьй выход регистра микрокоманд соединены соответственно с информационными и управляющими входами мультиплексора, первый и вто рой выходы которого соединены соответственно с первым и вторым управля ющими входами коммутатора, второй вы к ход регистра микрокоманд соединен с входами первого и второго блоков па мяти микрокоманд, выходы которых соединены с первым и вторым информационным входами коммутатора, выход коммутатора соединен с входом регистра микрокоманд, выход которого соединен с выходом устройства C2J. Недостатками известного устройст ва являются большой объем оборудования блоков памяти и низкий коэффи циент их использования. Эти недостатки обусловлены избыточностью.микрокоманд, которая вызвана тем, что поля логических условий микрокоманд в линейных последовательностях не заполнены полезной информацией. Коды логических условий записываются только в микрокомандах ветвления, во всех остальных микрокомандах блока памяти поле кода логических условийявляется свободным.. Суммарный объем избыточного оборудования блоков памяти, содержащего N микрокоманд, из которых Ng являются микрокомандами ветвления, оценивается выражением (м-%) где гПд - разрядность поля кода логических УСЛОВИЙ. Цель изобретения - сокращение количества оборудования. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащеепервый и второй блоки памяти микрокоманд, коммутатор микрокоманд, регистр микрокоманд, генератор тактовых импульсов и мультиплексор логических условий, причем первый выход первого блока памяти микрокоманд и выход второго блока памяти микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора микрокоманд, выход которо- , го соединен с информационным входом регистра микрокоманд, выходы кода операций которого являются группой выходов устройства, группа -входов логических условий устройства соединена с группой П-информационных входов мультиплексора логических условий (где h - количество источников логических условий, первый выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд, введены коммутатор адреса, регистр адреса, регистр логических условий, блок элеме тов И и триггер пуска, причем первая группа tyi)-информационных входов коммутатора является группой Ут -входов кода команды устройства (где In - раз рядность адреса блоков памяти микрокоманд ), ,i- -и информационный ( L 1 ,2,... , (т-1)) вход второй группы коммутатора адреса соединен с L-м вы ходом немодифицируемого разряда адре са регистра микрокоманд, выход модифицируемого разряда адреса которого соединен с(11+1)-м информационным входом группы мультиплексора логичес ких условий, группа управляющих BXQдов которого соединены с группой выходов регистра логических условий, выход мультиплексора логических усло вий соединен сщ-м информационным входом второй группы коммутатора адреса, управляющий вход которого соединен с выходомпризнака конца команды регистра микрокоманд, выход признака конца работы которого соеди нен с входом установки в О триггера пуска, вход установки в I которого является входом запуска устройства, выход триггера пуска соединен с входом запуска генератора тактовых импульсов, первый выход котоiporo соединен с входом синхронизащии регистра логических условий, jвторой выход генератора тактовых импульсов соединен с входом синхрони зации регистра адреса, группа инфор1мационных входов которого соеди;нена с группой выходов коммутатора адреса, группа выходов регистра адреса соединена с группами адресных вхрдов первого и второго блоков памяти микрокоманд, второй выход первого блока памяти микрокоманд соединен с первый входом блока элементов И, второй вход которого соединен с управляющим входом коммутатора микрокоманд и с выходом признака анализа логических условий регистра микрокоманд выход блока элементов И соединен с информационным входом регистра логических условий. Сущность изобретения состоит в уменьшении объема блоков памяти путем группирования внутренних и внешних микрокоманд линейных последовательностей и их раздельного хранеНИЯ;Под внешними понимаются микрокоманды, кoтopы m начинаются и заканчи ваются- линейные последовательности. Как правило, внешними микрокомандами являются микрокоманды условного и безусловного переходов, а также начальные микрокоманды микропрограмbfiii. Микрокоманды, содержащиеся в линейных последовательностях между их первой и последней внешними микрокомандами назьтаются внутренними. Для микропрограммы, описываемой следующей ЛСА , t , где Xi - логическое условие, А. . 43 внешними являются микрокоманды А , А, А, А, Aj,, авнутренними - микрокоманды А, А, А$ - А.,, А - При раздельном хранении таких микрокоманд обеспечивается уменьшение объема оборудования блоков памяти благодаря тому, что поле логических условий во внутренних микрокомандах может быть исключено. ; На фиг.1 представлена функциональ-. ная схема устройства; на фиг. 2 пример микропрограммы для сравнения эффективности предлагаемого и известного устройств. Микропрограммное устройство управ ления (фиг.1) содержит первый. 1 и второй 2 блоки памяти микрокоманд, регистр 3 адреса, регистр А юскрокоманд с полями адреса 4, микроопераций 42 и признака анализа логических условий 4з, регистр 5 логических условий, коммута:тор 6 адреса, коммутатор 7 микрокоманд, мультиплексор 8 логических условий, тригЬ гер 9 пуска, генератор 10 тактовых импульсов с вторьм 10j и первым 10 выходами, блок 11 элементов И, вход 12 кода команды, группу 13 входов логических условий, вход 14 пуска, группу выходов 15, вькход 15 признака конца команды и выход 15 признака конца работы регистра микрокоманд, первый 16 и второй 17 выходы первого блока памяти микрокоманд. На фиг. 2 символами Х, Xj, обозначеиы логические условия, w и т„-разрядность микрокоманд и разрядность поля кода логических условий соответственно. Густой штриховой покезаиа неинформативиая зона в известном устройстве, которая исключается в предлагаемом. Блок 1 памяти микрокоманд предназначен для хранения внешних микрокоманд линейных последовательностей. В блоке 2 памяти микрокоманд хранится информация о внутренних микрокомандах. Регистр 3 адреса пре назначен для хранения адреса очеред ной микрокоманды и вьщачи его в блоки 1 и 2 памяти. Регистр 4- микрокоманд предназначен для хранения кода очередной микрокоманды. В этот регистр считываются полные коды внутренних микрокоманд из блока 1 памяти и час ти кодов внешних микрокоманд за исключением кода логических условий из блока 2 памяти. В поле 4 записывается адресная часть микрокоманды, немодифицируемые разряды которой поступают через коммутатор 6 в регистр .3, а модифицируемой разряд подается на мультиплексор 8. В поле 4 заносится операционная часть. Микрооперация поступают на ;выход 15 устройства, а сигналы кон да.команды и конца работы с выходов 15, и 15i соответет.в«нно управляют занесением кода операции и вкл чением устройства. В поле 4з записывается 1 в мик .рокомандах, за которыми следуют вне ние микрокоманды, благодаря чему по следующему импульсу разрешается счн тьтание информации из блока 1 памят |В регистры 4 и 5. : Регистр 5 предназначен для запоминания кода логических условий и выдачи его на мультиплексор 8. Коммутаторы & и 7 предназначены для коммутации адресов и микроко:манд в зависимости от сигналовупра ления, подаваемых на их входы с выходов 15,, и соответственно. i Мультиплексор8 осуществляет мод , фикацию младлего; адресного разряiga в сортветствин с формулой fJ i:-}h- Xibib2...1н АгЦЬгЦ Jb, b 3i ib2b3...b«t.. , значение младшего адресного ;где а разряда, зиачения проверяемых логич ких условий; ,к , - значения j-ro разряда кода логических условий. 66 Триггер 9 предназначен для управления пуском и остановом устройства. Генератор 10 тактовых импульсов предназначен для формирования тактовых импульсов, синхронизирующих работу устройства. Блок 11 элементов И предназначен для управления выдачей кодов логических условий при считывании внешних микрокоманд- в регистр 5. Устройство работает следующим образом. В исходном состоянии регистр 3 адреса обнулен, ас выходов и 45. регистра 4 логические единицы поступают на управляющие входы коммутаторов адреса 6 и микрокоманд 7, а , j также на вход блока I1 элементов И. Работа устройства начинается с приходом на вход 12 кода команды и на вход 14 сигнала пуска. С входа 12 код команды поступает на вход коммутатора адреса микрокоманд далее на информационный вход регистра 3. Сигнал, поступающий на вход 14, переводит триггер 9 пуска в единичное состояние. Поступающий с единичного °« триггера 9 пуска сигнал запускает генератор 10 тактовых импульсов . По заднему фронту этого импульса поступающего на второй вход синхронизации регистра 3, происходит запись, в данный регистр адреса первой микро-. команды. Адрес этой микрокоманды с регистра 3 поступает на блоки 1 и 2 памяти. С блока 1 памяти информация поступает на блок 11 элементов И и коммутатор 7. Так как с выхода 4 регистра 4 первоначально снимается логическая 1, то информация с блока 2 памяти через коммутатор 7 микро- команд не проходит. Код логических условий внешней микрокоманды из блока 1 памяти с выхода 16 через блок II элементов Т/1. поступает на регистр 5, а адресная и операционные части микрокоманды с выхода 17 чере.з коммутатор 7 - на.регистр 4. По заднему фронту второго тактового импульса, поступившего с выхода 10 генератора 10, код внешней микрокоманды заносится в регистры 4 и 5. Если следующая микрокоманда является микрокомандой в1етвления, то с выхода 4з. регистра 4 логическая 1 подается на вход блока 11 элементов И и управ7n

яющий вход коммутатора 7 микрокоанд, запрещает прохождение инфорации с блока 2 памяти и разрешает : прохождение информации с блока 1 амяти в регистры 4 и 5 аналогично описанному.

Формирование адреса микрокоманды, следующей за ветвлением, происходит в зависимости от кода логических: условий. Мультиплексор 8 выбирает значение проверяемого логического условия и если оно равно О, то изменение младшего адресного разг ряда с О на 1 не происходит (в микрокомандах ветвления значение мпадшего адресного разряда всегда равно О). Если же значение проверяемого логического условия равно 1, то мпадший адресный разряд, поступающий с выхода 4 регистра 4

в мультиплексор 8,изменяется с О

. Сформированный таким образом адрес (его немодифицируемые и модифицируемый разряды) поступает на коммутатор 6. Поскольку сигнал на выходе 15 регистра 4 для всех микрокоманд, кроме последней в микропрограмме, равен О, то адрес следующей микрокоманды через коммутатор 6 записьюается в регистр 3.

Если очередная микрокоманда является внутренней, то с выхода 4г снимается нулевой сигнал, запрещающий прохождение информации с блока 1 памяти микрокоманд и разрешающий подачу кода с блока 2 памяти микро-, команд через коммутатор 7 микрокоманд в регистр 4. С этого регистра адрес следующей микрокоманды через коммутатор 6 заносится в регистр. При формировании адреса данной микокоманды модификации младшего адресного разряда не происходит, поскольку в регистре 5 записан нулевой код. После выполнения всех микрокоманд данной микропрограммы с выхода }5 регистра 4 снимается логическая I,

08668

разрешающая прив кода следующей операции.

После выполнения последней микропрограммы с выхода. IS. регистра-4 5 на вход установки в О триггера 9

пуска поступает логическая 1, устанавливающая триггер в нулевое состояние. Генератор 10 тактовых импульсов останавливается и устрой 10 ство прекращает свою работу.

Выигрьш в объеме оборудования блоков памяти, получаемый при использовании предлагаемого устройства, оценивается выражением

AW mN-mN4-Cmtii)Ni,

где m - разрядность микрокоманд

|iJ(N- количество внешних (рнутреннихр микрокоманд.

20 Поскольку N;, + N, N, то справедливо ,, , . . AW hiAN2

Относительная величина выигрьша оценивается выражением

6w - -ioo%

Поскольку ,2m, а N, ;iO,6N, &Tfl 12%.

Величины абсолютного и относи тельного выигрьш1ей в коэффициенте

использования оборудования могут быть определены по формулам:

Мг( - Уг.«1-тл)+А/1т .

iNhi-(N-N6/m A 1 Nhi

KK Nm100 Уо.

° .-(

С учетом принятых допущений ДК 0,04, К 5-6%.

Таким образом, предложенное устройство существенно превосходит известное и базовый объект по экономичности и коэффициенту использования оборудования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU830384A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-30—Подача