(54) ПРЕОБРАЗОВАТЕЛЬ КОДА С ПОСТОЯННЫМ ВЕСОМ В ДВОИЧНЫЙ КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Преобразователь двоичного кода в перестановочный код | 1977 |

|

SU656053A1 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Преобразователь двоичного кода в частоту следования импульсов | 1981 |

|

SU1023653A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2254676C2 |

Изобретение относится к цифровой вычислительной технике и может быть использовано нри построении систем передачи данНЬ1Х.

Известно устройство для преобразования кода постоянного веса в двоичный код 1, содержащее счетчик, дешифратор кодовых комбинаций, выходной регистр и шифратор.

Недостатки известного устройства - сложность и относительно невысокое быстродействие.

Наиболее близким техническим решением данной задачи является устройство 2, содержащее шины входного кода, дешифратор кодовых групп, блок элементов ИЛИ и шины выходного кода.

Недостатком этого устройства является ограниченность функциональных возможностей, заключающееся в возможности преобразования кодов с постоянным весом, упорядоченных только как двоичные числа. Другим недостатком известного устройства является относительно низкое быстродействие.

Целью изобретения является повыщение быстродействия и расщирение класса преобразуемых кодов.

Цель изобретения достигается тем, что устройство содержит анализатор кодовых

комбинаций, входы которого соединены с шинами k- п входного кода (где k - число разрядов двоичного кода, п - число разрядов входного кода), первый и второй коммутаторы, выходы которых подключены к соответствующим входам блока элементов ИЛИ, первые входы первого и второго коммутаторов соединены с ()-oй шинами входного кода, вторые входы первого и второго коммутаторов соединены с выходами дешифратора кодовых групп, а третий вход первого коммутатора соединен с первым выходом анализатора кодовых комбинаций, первые входы дещиф|ратора кодовых групп соединены с (1 -rk)-OK шинами входного кода, а вторые входы соединены со вторыми выходами анализатора кодовых комбинаций, и тем, что в нем анализатор кодовых комбинаций содержит р (п - k -f 1) элементов И, р - входовой элемент ИЛИ, входы которого соединены с выходами элементов И и элементов И.

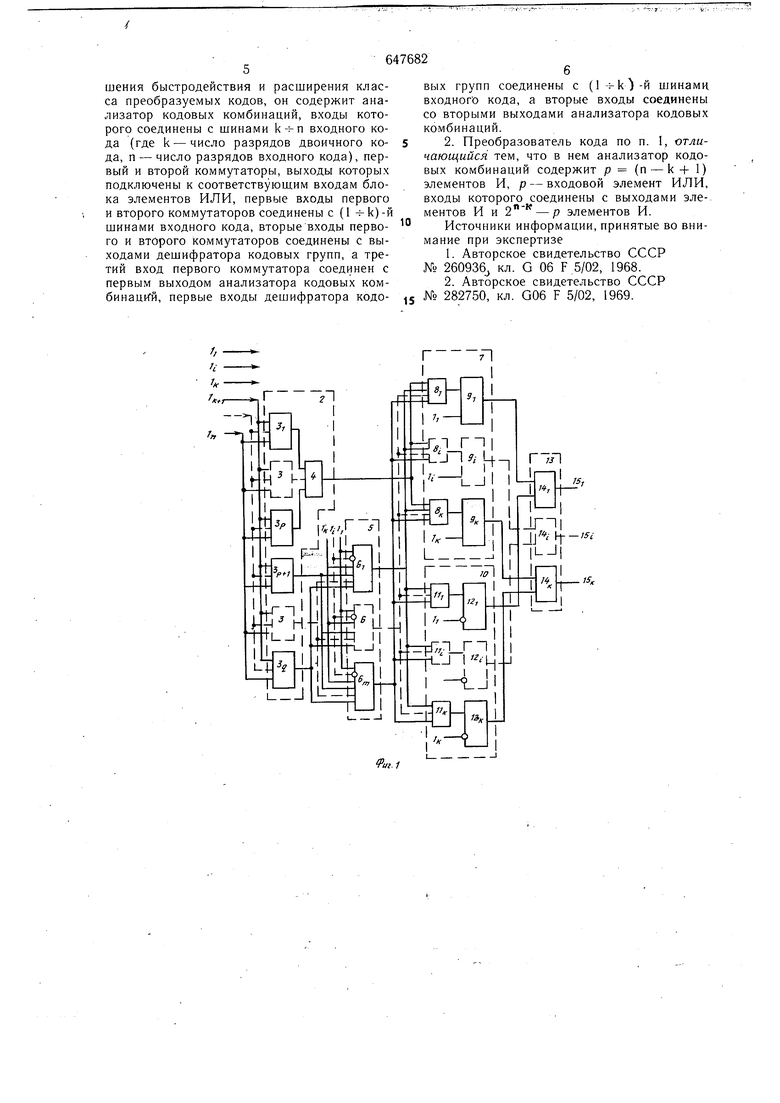

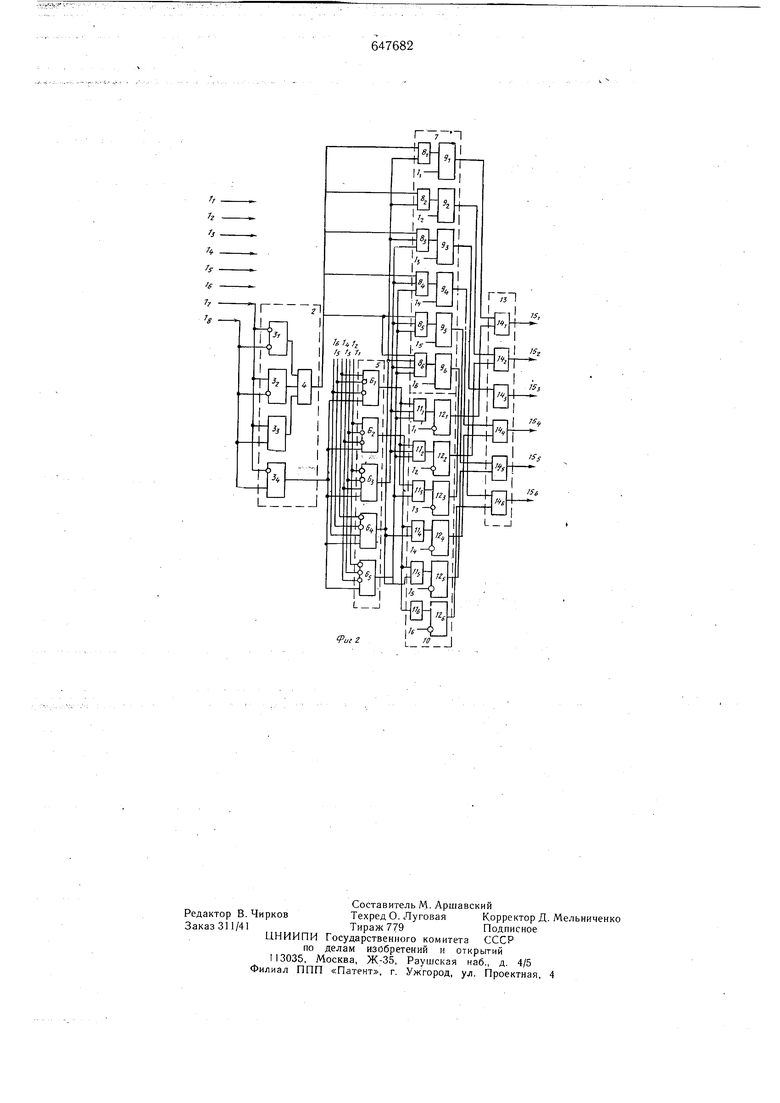

На фиг. 1, 2 приведены варианты блоксхемы предложенного устройства.

В блок-схему включены: Ц1инь 1 входного кода, анализатор кодовых комбинаций 2, элементы И анализатора кодовых комбинаций, элемент ИЛИ 4 анализатора кодовы.х комбинаций, дешифратор кодовых групп 5, элементы И 6| -бт дешифратора кодовых групп, первый коммутатор 7, элементы ИЛИ 8| первого коммутатора, элементы И 9) -т-9к первого коммутатора, второй коммутатор 10, элементы ИЛИ 1 11к второго коммутатора, элементы И 12, второго коммутатора, блок элементов ИЛИ 13, .элементы ИЛИ 14) , шины выходного кода 15| -;-15к. Шины IK+I, , I-n входного кода соединены со входом анализатора кодовых комбинаций 2, содержащего q элементов И 3| -3q с (п -kj-входами каждый. Первые р (п - k + I) элементов И 3, объединены по выходу через р-входовой элемент ИЛИ 4. Входы дешифратора кодовых групп 5, содержащего m элементов И 6i , соединены с выходами элементов , ...,3q анализатора кодовых комбинаций 2 и с шинами 1, ,..., Ij, входного кода. Выход элемента ИЛИ 4 и выходы элементов И 6i соединены через элементы ИЛИ 8| первого коммутатора 7 с перзыми входами элементов И 9 -;-9к; Выходы элементов 6) соединены также через элементы ИЛИ .11 -i- 1 IK второго коммутатора 10 с перЕ5ыми входами элементов И 12) -г-12к. Шины разрядов Ij -ь IK входного кода соединены со вторыми (пря.мыми) входами элементов И 9| 9 коммутатора 7 и со вторыми (инверсными) входами элементов И 12) - 12к ком.мутатора 10. Выходы элементов И 9i коммутатора 7 и элементов И 12i коммутатора 10 соединены через элементы ИЛИ 141 блока элементов ИЛИ 13 с шиной 15i разряда i выходного кода. Устройство работает следующи.м образом, Слово параллельного п-разрядного кода с постоянным весом типа/т возбуждает шинь( 1( -bin- В анализаторе кодовых комбинаций 2 в зависимости от состояния шин IKH - Ifi во; никает сигнал на выхЬде только одного из элементов И 3) - Зп. Если в щинах и.меет место одна из (п - k + 1) комбинаций 00...О, ПО...О, ..., 11...1, то возникает сигнал на выходе одного из элементов 3| -ьЗр и на выходе элемента ИЛИ 4 анализатора 2. При любой другой комбинации кодов в шинах -н In сигнал возникает на выходе одного из элементов И 3pti -i-3q анализатора 2. Сигнал на выходе элемента ИЛИ 4 открывает через элементы ИЛИ 8| -8к элементы И 9 -9к коммутатора 7, которые срабатывают как открытые ключи, пропуская сигналы шин Ь - IK в прямом коде через элементы ИЛИ 14, 14 блока 13 на шины 15| -т- 15к выходного кода. При наличии сигнала на выходе одного из элементов Зрц анализатора 2, в зависимости от комбинации возбуждений в шинах 1| н-1, возникает сигнал на вых.оде одного из т элементов И 6| -r-6tn дешифратора 5. Этот сигнал открывает часть элементов И 9 через элементы ИЛИ 8 коммутатора 7 и часть элементов И 12 через элементы ИЛИ II коммутатора 10. Сигналы шин li - IK проходят в шины 15| -ь15к-через открытые Элементы И 12 коммутатора 10 в инверсном коде, а через открытые элементы И 9 коммутатора 7 в прямом коде. Выбор открываемых ключей определяется типом m кода с постоянным весом. В качестве примера на фиг. 2 приведена блок-схема устройства для перекодирования типа m 5 восьмиразрядного кода веса 4 в шестиразрядный полный двоичный кйд. В этом коде с постоянным весом р a-k+l 8 - 64-1-3, q -- . Рассмотрим преобразование слов входнрго кода; 10100011, 11010001, 00011101. После поступления первого слова будут возбуждёны шины 1, , Ij, Ь , U . В анализаторе 2 появится сигнал на выходе элемента Зз и элемента ИЛИ 4. Через элементы ИЛИ 8i откроются ключи (элементы И) 9i, 95 коммутатора 7 и через элементы ИЛИ I4i, 14з блока 13 появятся сигналы в шинах I5i , 15з выходного кода, образуя слово 101000. После поступления второго слова будут возбуждены шины 1, , Iz, Ц, 1в В анализаторе 2 появится сигнал па выходе элемента И 3. В дешифраторе 5 возбудится выход элемента И 6, , который через элементы ИЛИ 11| , 2 , Из откроет ключи (элементы И) 12| , 122, 12з ком.мутатора 10. Сигналы шин 1| , 2, 1а в инверсном коде пройдут через коммутатор 10 и через элементы ИЛИ 14| , 14.j, 14з возбудят одну шину-15з выходного кода, образуя слово 001000. После поступления третьего слова будут возбуждены илины U , Is , U, в В анализаторе 2 появится сигнал на выходе элемента И 3 . В дещифраторе 5 возбудится выхо элемента И 65, который через элементы ИЛИ 84, 85, 8б коммутатора 7 и 11,, 1Ь, 11з коммутатора 10 откроет ключи (элементы И) 9, 95, 9б ком.мутатора 7 и 12i, 12, 12з коммутатора 10. В результате на выходах элементов ИЛИ 14) блока 13 на шинах появятся сигналы, образующие слов.о И 1111. Применение устройства позволяет увеличить быстродействие системы кодер декодер не менее че.м в 2-раза и менять порядок кодирования без изменения структуры преобразователя. Это приводит к повышению помехоустойчивости тракта, в котором применено устройство, за счет возможности адаптации передачи к состоянию канала. Формула изобретения 1. Преобразователь кода с постоянньпи весом в двоичный код, содержащий шины входного кода, дешифратор кодовых групп, блок элементов ИЛИ и шины выходного кода, отличающийся тем, что, с целью повышения быстродействия и расширения класса преобразуемых кодов, он содержит анализатор кодовых комбинаций, входы которого соединены с шинами k-нп входного кода (где k - число разрядов двоичного кода, п - число разрядов входного кода), первый и второй коммутаторы, выходы которых подключены к соответствующим входам блока элементов ИЛИ, первые входы первого и второго коммутаторов соединены с (1 н-и)-й шинами входного кода, вторые входы первого и второго коммутаторов соединены с выходами дешифратора кодовых групп, а третий вход первого коммутатора соединен с первым выходом анализатора кодовых комбинаций, первые входы дешифратора кодовых групп соединены с ()-й шинами входного кода, а вторые входы соединены со вторыми выходами анализатора кодовых комбинаций.

Источники информации, принятые во внимание при экспертизе

Г-1

Авторы

Даты

1979-02-15—Публикация

1977-03-24—Подача