(5 4) Я АК АП Л ИВ АЮЩИЙ СУММ ATOP .С КОРРЕКЦИЕЙ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Двоичный счетчик с обнаружением ошибок | 1984 |

|

SU1169163A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Накапливающий сумматор с фиксацией ошибок | 1976 |

|

SU603990A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

Изобретйние относитсяк области вычислительной техники и может быть- использовано в цифровых вычислительных машинах.

Известен накапливающий сумматор с,коррекцией ошибок, содержащий п схем суммирования, схему контроля по модулю 3, схему коррекции, схему управления коммутацией и элементы И и ИЛИ I. Недостаток известного устройства состоит в том, что С 1гналы коррекции зависят от ия-; формации, вырабатываемой схемой контроля отчетности номера разрядной схемы, коррекция осуществляется сложной схемой управления коммутацией.

Из известных устройств наиболее близким техническим решением к предлагаемому изобретению является накапливающий сумматор с коррекцией ошибок, содержащий в каждом разряде триггер со счетным входом, первый, второй и третий элементы ИЛИ, первый и второй формирователи импульсов, элемент задержки, первый и второй элементы И, блок сравнения, четвертый элемент ИЛИ, триггер фиксации ошибок, третий и четвертый элементы И, причем выход первого элемента. ИЛИ каждого разряда соединен со счетным входом триггера, единичный выход каждого триггера соединен с первым входом первого элемента И и со входом первого формирователя импульсов; выход которого соединен с первым входом второго элемента ИЛИ, нулевой выход каждого триггера соединен со входом второго формирователя импульсов, выход которого соединен первым входом второго элемента И и со вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым вхОдОм блока сравнения, второй вход которого соединен с выходом элемента за держки, выходы первого и второго элементов И соединены с первым и вторым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ каждого разряда сумматора сое

дииен с первым входом первого элемента ИЛИ и вторым входом первого элемента И следующего старшего разряда сумматора, вторые входы первых элементов ИЛИ образуют первую группу входов устройстьа,

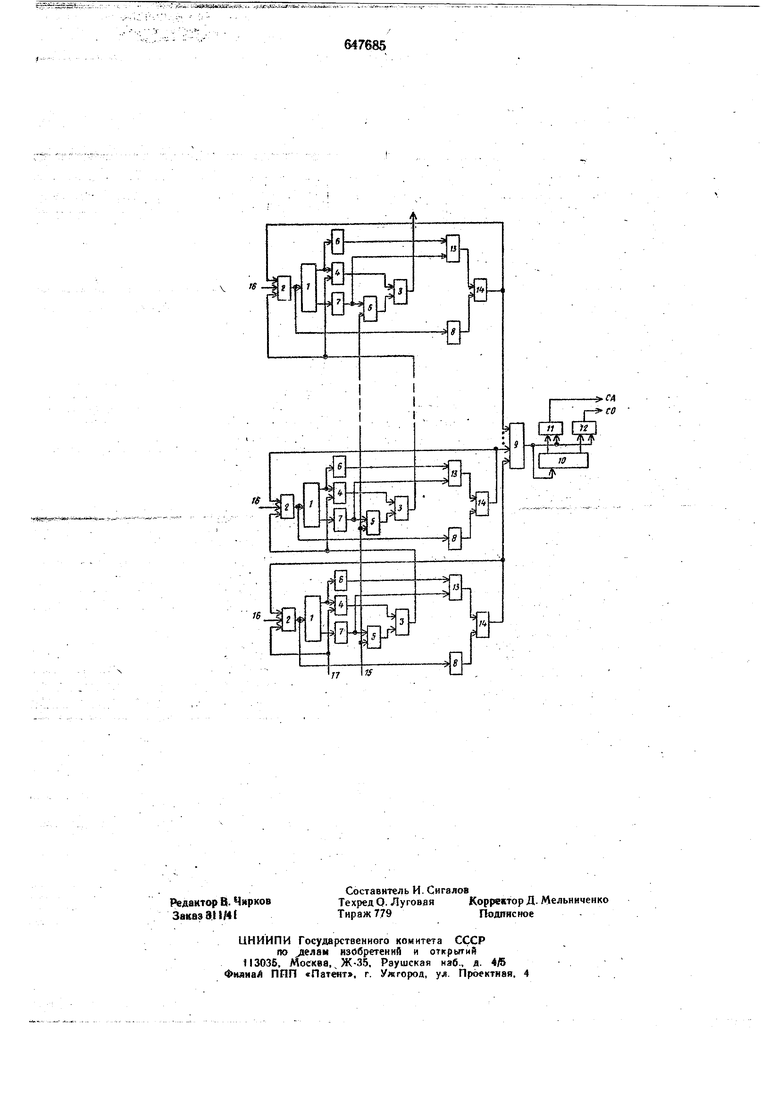

второй вход второго элемента И всех разрядов соединен с управляющим входом устройства, выход каждого блока сравнения соединен с третьим входом первого элемента ИЛИ каждого разряда н со входом четвертого элемента ИЛИ, выход которого соеди364нен с единичным входом триггера фиксации ошибок и с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответетвеннб с нулевым и единичным выходом триггера фиксации ошибок, выходы третьего и четвертого элементов И соединены соответственно с первым я вторым выходом устройства |2}. Недостатком известного устройства является его сложность. Целью изобретения является эконЬмия оборудо 5ания. Поставленнай цель достигается тем, что is каждом разряде выход первого элемента ИЛИ соединен со входом элемента задерх кй. Структурная схема предлагаемогь сумматора приведена на чертеже. В предлагаемом сумматоре каждый разряд содержит счетный триггер I, первый и третий элементы ИЛИ 2 и 3, первый и второй элементы И 4 и 5, формирователи, импульсов 6 и 7, элемент задержки 8, четвёртый элемент ИЛИ 9, триггер Ш фиксации ошибок, третий и четвертый элементы И II и 12, втqpoй элемент ИЛИ 3, блок сравнения 14, щину 15 запрета пЬвтбрнргЬ переноса, упр;авляющий вход устройства. Счетный вход счетного триггера 1 каждого разряда подключен к выходу первого элемента ИЛИ 2, входы которого подсоединены к входной шине 16, шине выхода пере|юса из предыдущего разряда 17 и К 18ыходу блока сравнения 14. Единичный выход счетного триггера I соединён со входом формирователя импульсов 6 и с Первым вводом первого элемента И 4, ко второму входу которого Подключена шина выхода jiepeHoca из предыдущего разряда 17. Нулевой вь1ход счетного триггера f соецинен со входом второго формирователя им1ульсов 7, выход которого подключен к перюму входу второго элемента И 5, второй зход которого соединен с шиной запрета поугорного переноса i 5. Выходы элементов И 4 и 5 подключены к входам третьего элемента ИЛИ 3, №Шхкотор 6гбсоёдШе с ииной выхода jiepeHOCa в последующий . В каждом разряде выходы формиро ателей импульсов 6 и 7 соёдннёны с пер1ЫМ и вторым входами второго элемента ИЛИ 13, выход к Шр6го подключен к первому входу блока сравнения И, второй вход которого подсоедийёй к выходу элемента задержки 8, вход W toporuнепосредственно соединен со счетным входом счетного триггера i соответствующего разряда. . Кроме того, выходы блоков сравнения 14 «ех подключены ко входам четвертого элегенТЯ ИЛИ 9, выход которого соединен с диничным входом триггера фиксации ошиOK 10 и вторыми входами эжмеЩРР, 12, первые входы которых подключены к адничному и нулевому выходам триггера нксации ошибок 10 соответственно. Сигналы «аварии н «О1иибка снимаются с выходов алементов И И, 12 сооггветственно. Так как все разряды предлагаемого сумматора выполнены идентично,, то работу устройства рассмотрим на примере одиого разряда.. Перед работы в сумматоре может содержаться результат предыдущей операции, но триггер фиксации ошибок устан;авливаётся в нулевое .состояние. На вход первого элемента ИЛИ 2 поступает единичный сигнал либо со входа 16, либо с выхода бло14а сравнения 14 (сигнал коррекции ошибок), либос выхода третьего элемента ИЛИ 3 предыдущего разряда (сигнал переноса). С выхода элемента ИЛИ 2 снгнал поступа-.--f- .--- -: -t--Kn-ffKl Й-5.. - - ет на счетный вход счетного триггера 1 и ia вход элемента задержки 8 этого разряда, который рассчитан на сумму времен срабатывания счетного триггера, элемента ИЛИ и формирования импульсов. Если при поступлении единичного сигнала счетный триггер I срабатывает (изменяет свое состояние на противоположное), то на выходе одного из формирователей импульсов 6 и 7 сформируется сигнал требуемой полярности, который через второй элемент ИЛИ 3 узла коррекции ошибок поступает на первый вход блока сравнения 14 данного рааряда. На второй вход этого же блока сравнения 14 через элемент задержки 8 поступает «единичной сигна.п со счетного входа счетнйго триггера 1. При этом на выходе данного блока сравнения 14 сигнал не образуется и, с.ледовательно, будет отсутствовать сигнал «Ошибка (СО) на выходе элемента И 12. Если при поступлении «единичного сигнала счетный триггер J не сработает, то на выходах формирователей импульсов 6 и 7 Сигнал не формируется. В этом случае на первом входе блока сравнения 14 снгнал отсутствует, а иа его второй вход поступит задержанный «единичный сигнал, который приводит ft появлению сигнала на выходе блока сравнения 14. «Едини иый сигнал с выхода этого блока сравнения 14 поступит на вход первого элемента ИЛИ 2 расCMarpBlEtaeMOrb разряда и. иа соответствующий вход четвертого элемента ИЛИ 9. Сигнал с выхода элемента ИЛИ 9 одновременно выдается на вторые входы элементов И И, 12 и на вход записи единицы в триггер фиксации ошибок. В результате этого на выходе элемента И 12 образуется сигнал, который свидетеяьс7вует о наличии ошибки при суммировами чисел. Одковрененяо сигнал с выхода элемента 14 (сигнал коррекции) П€ ступает «1ерез первый элемент ИЛИ 2 на счетный вход счетного триггера I, в котором зафиксирована ошибка, и через элемент ИЛИ 2 - на вход элемента задержка 8 (для контроля коррекции). Если ошибка скорректирована, т на оба входа соответствующего блока сравиеиия 14

одновременно поступят сигналы с выхода элемента ИЛИ 13 и с выхода элемента задержки 8. В этом случае на выходе блока сравнения 14 и на выходе элемента И 12 сигналы отсутствуют.

Если же ошибка не скорректировалась, то на входе рассматриваемого блока сравнения 14 повторно образуется «единичный сигнал, который через четвертый элемент ИЛИ 9 подаётся на входы элементов И 11 и 12. Поскольку триггер фиксации ошибок 10 находится в «единичном состбянни, то на выходе элемента И 11 образуется сигнал «Авария (СА).

Таким образом, в отличие от прототипа, предлагаемое устройство при меньшем количестве оборудования обладает большими возможностями по обнаружению и коррекции ошибок при суммировании числа, благодаря чему повышается наДен ность работы устройства.

Формула изобретения

Накапливающий сумматор с коррекцией ошибок, содержащий в каждом разряде триггер со счетным входом, первый, второй и третий элементы ЙЛИ первый и второй формирователи импульсов, элемент задержки, ° п1рвь1й и..второй элементы И, блок сравыепия, четвертый элемент ИЛИ, триггер фиксации ошибок, третий и четвертый элементы И, причем выход первого элемента ИЛИ каждого разряда соединен со счетпым входом триггера, единичный выход каждого триггера соединен с первым входом первого элемента И и со входом первого формирователя импульсов, выход которого соединен, с первым входом второго элемента ИЛИ, нулевой выход каждого триггера соединен со входом второго формирователя импульсов, выход которого соединен с первым входом второго элемента И со вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом блока сравнения, второй вход которого соединен с выходом элемента задержки, выходы первого и второго И соединены с первым и вторь м входом третьего элемента ИЛИ, выход третьего элемента ИЛИ каждого сумматора соединен с первым входом первого элемента ИЛИ я вторым входом Первого элёмеПТа И следующего старшего разряда сумматора, вторые входы первых элементов И Л Pi образуют первую группу пхоДов устройства, второй вход второго элемента И всех разрядов соединен с управляющим входом устройства, выход каждого блока сравнения соединен с третьим входом первого элемента ИЛИ каждого разряда и .со входом четвертого элемента ИЛИ, быход которого соедипеп с единичным входом фиксации ошибок и с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с пулевым и в)1ходом триггера фиксации ошибок, выходь третьего и четвертого элементов И соединены соответственно с первым и вторым выходом устройства, отличаю(, 1йся тсм Чго с целью экономии оборудования, в каждол р азряйс пШШТГ Ilер вТУГо элемелта ИЛИ соединеп совходом элемента задержки.

Источники информация, принятые во вниМапие при экспертизе

Авторы

Даты

1979-02-15—Публикация

1977-02-07—Подача