1

Изобретение относится к области цифровой вычислитепьной техники и может быть испопьзовано при построении арифметических устройств цифровых вычислительных машин.

Известны устройства для умножения, в которых многократные сложения, за исключением последнего такта, выполняются без затрат времени на распространение переносов l. Это свойство обеспечивает устройству относительно высокие скоростные характеристики, однако достигается ово путем увеличения атшратурного состава.

Имеются устройства, выполняющие операцию умножения, которые содержат триггерный накапливающий сумматор с цепью сквозного переноса 2. Такие устройства аппаратурно выполнены прощ но имеют меньшее быстродействие, поскольку требуют на каждое сложение временных затрат на распространение переносов.

Наиболее близким аналогом является устройство для умножения содержащее накапливающий сумматор, регистр множимого, регистр множителя, элемент И, причем выходы регистра множимого подключены к первым входам соответствующих элементов И, выходы которых подключены к соответствующим входам накапливающего сумматора, выход старшего разряда регистра множителя подключен к первому входу первого управляемого элемента И, второй вход которого подключен к первому управп5пощему входу устройства, а выход - ко вторым входам четных элементов ..

Такое устройство имеет низко..

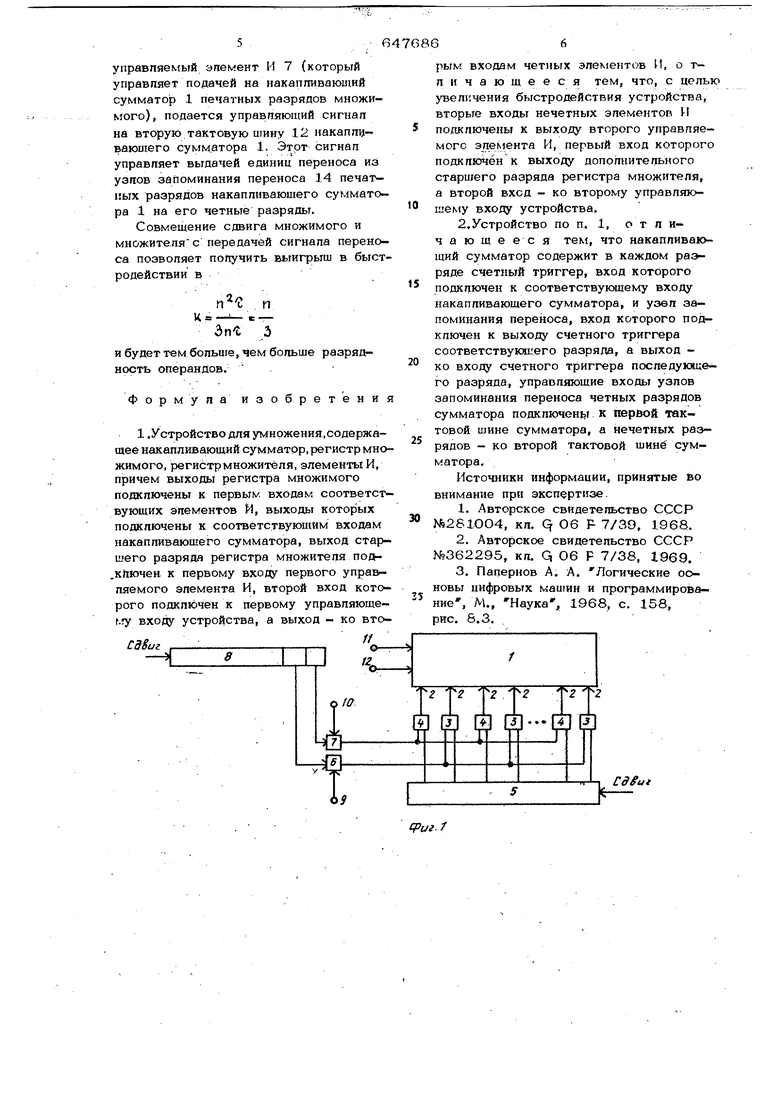

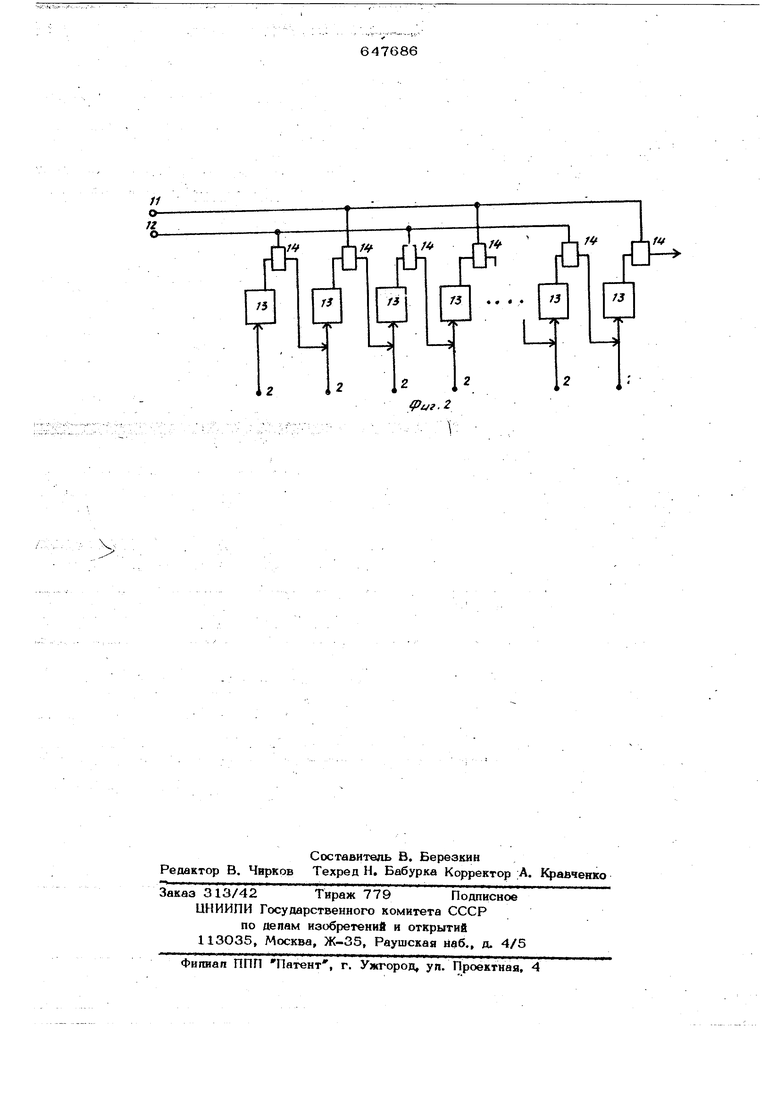

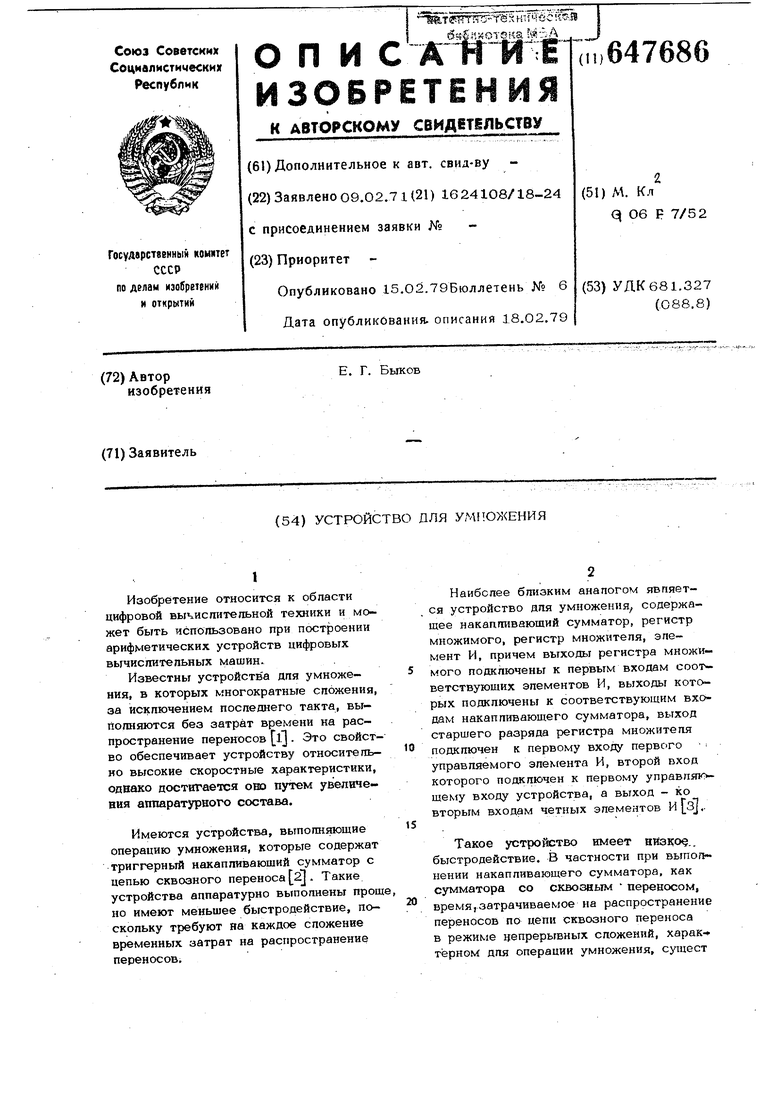

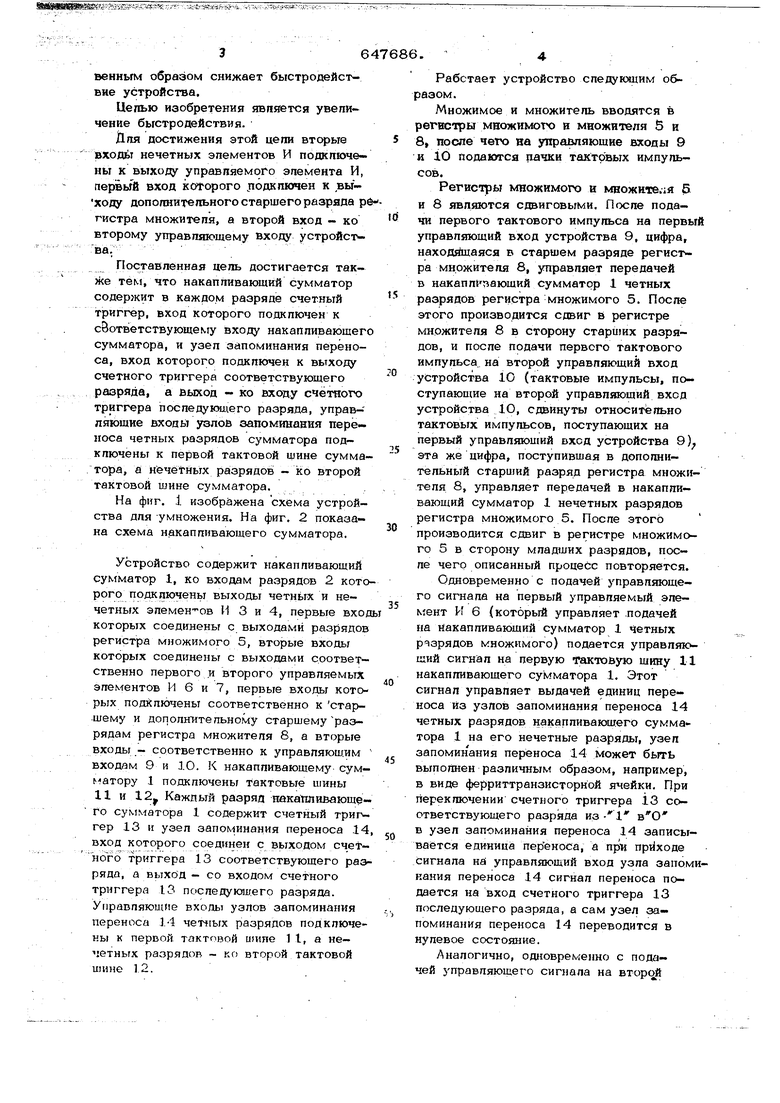

быстродействие. В частности при выпог нении накапливающего сумматора, как сумматора со сквозным переносом, время,затрачиваемое на распространение переносов по цепи сквозного переноса в режиме непрерывных сложений, характерном для операции умножения, сущест венным образом снижает быстродействие устройства. Цепью изобретения является увеличение быстродействия. йпя достижения этой цепи вторые входит нечетных элементов И подкпючены к выходу управляемого эпемента И, вход kotoporo подключен к выходу дополнительного старшего разряда ре гистра множителя, а второй вход ко второму управляющему входу устройств ва. Поставленная цепь достигается также тем, что накапливающий сумматор содержит в каждом разряде счетный триггер, вход которого подключен к соответствующему входу накапливающег сумматор/а, и узел запоминания переноса, вход которого подключен к выходу счетного триггера соответствующего разряда, а выход ко входу счетного триггера последующего разряда, управляющие входы узлов запоминания переноса четных разрядов сумматора подключены к первой тактовой шине сумматора, а нечётных разрядов - ко второй тактовой шине сумматора. На фиг. 1 изображена схема устройства для -умножения. На фиг. 2 показана схема накаппивающего сумматора. Устройство содержит накапливающий сумматор 1, ко входам разрядов 2 кото рого подключены выходы четных и нечетных элемен- ов И 3 и 4, первые вхо которых соединены с выходами разрядов регистра множимого 5, вторые входь; которых соединены с выходами соответственно первого и второго управляемых элементов И 6 и 7, первые входы которых подключены соответственно к старшему и дополните пьному старшемуразрядам регистра множителя 8, а вторые входы - соответственно к управляющим входам 9 и Ю. К накапливающему сум- aтopy 1 подключены тактовые шины 11 и 12 Каждый разряд накапливающе го сумматора 1 содержит счетный триг гер 13 и узел запоминания переноса 14 вход которого соединен с выходом счетного триггера 13 соответствующего раз ряда, а выход - со входом счетного триггера 13 последующего разряда. Управляющие входьт узлов запоминания переноса 14 четных разрядов подключе ны к первой тактовой uaine 1 1, а нечетных разрядов ко второй тактовой шине 12. Работает устройство следуквцим обазом. Множимое и множитель вводятся в егистры множимого и множителя 5 и , после четч на управляющие входы 9 и 10 подаются пачки тактовых импульсов. Регистры множимого и множнте.чя Б и 8 являются сдвиговыми. После подачи первого тактового импульса на первый управляющий вход устройства 9, цифра, находящаяся в старшем разряде регистра множителя 8, управляет передачей в накапливающий сумматор 1 четных разрядов регистра множимого 5. После этого производится сдвиг в регистре множителя 8 в сторону старишх разрядов, и после подачи первого тактового импульса, на второй управляющий вход устройства 10 (тактовые импульсы, поступающие на второй управляющий вход устройства 1О, сдвинуты относительно тактовых импульсов, поступающих на первый управляющий вход устройства 9) эта же цифра, поступившая в дополнительный старший разряд регистра множителя 8, управляет передачей в накапливающий сумматор 1 нечетных разрядов регистра множимого 5. После этого производится сдвиг в регистре множимого 5 в сторону младших разрядов, после чего описанный процесс повторяется. Одновременно с подачей управляющего сигнала на первый управляемый элемент И 6 (который управляет .подачей на накапливающий сумматор 1 четных разрядов множимого) подается управляющий сигнал на первую тактовую щину 11 накапливающего сумматора 1. Этот сигнал управляет выдачей единиц переноса Из узлов запоминания переноса 14 четных разрядов накапливающего сумма тора 1 на его нечетные разряды, узел запоминания переноса 14 может быть выполнен различным образом, например, в виде ферриттранзисторной ячейки. При переключении счетного триггера 13 соответствующего разряда из -I в О в узел запоминания переноса 14 записывается единица переноса, а пр« приходе сигнала ни управляющий вход узла запоминания переноса 14 сигнал переноса подается на вход счетного триггера 13 последующего разряда, а сам узел запоминания переноса 14 переводится в нулевое состояние. Аналогично, одновременно с подачей Зправпяющего сигнала на второй управляемый элемент И 7 (который управляет подачей на накапливающий сумматор 1 печатных разрядов множимого), подается управляющий сигнал на вторую тактовую щину 12 иакапл1 вающего сумматора 1. Этот сигнал управляет выдачей единиц переноса из узлов запоминания переноса 14 печат пых разрядов накапливающего суммато ра 1 на его четные разряды. Совмещение сдвига множимого и множителя с передачей сигнала перено са позволяет получить выигрыш в быст родействии в Зп Ь и будет тем больше, чем больше разрядность операндов. Формула изобретени 1 .Устройство для умножения,содержащее накапливающий сумматор, регистр мно жимого, регистр множителя, элементы И, причем выходы регистра множимого подключены к пepвы . входам соответст вующих элементов И, выходьг которых подключены к соответствукяиим входам накапливающего сумматора, выход стар шего разряда регистра множителя под.кйючен к первому входу первого управ ляемого элемента И, второй вход кото рого подключен к первому управляющеN5y входу устройства, а выход - ко вто С98иг -66 рым входам четных элементов И, о тл и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, вторые входы нечетных элементов И подключены к выходу второго управляемого элемента И, первый вход которого подключён к выходу дополнительного старшего разряда регистра множителя, а второй вход - ко второму управляющему входу устройства. 2. Устройство по п. 1, отличающееся тем, что накапливающий сумматор содержит в каждом раэряде счетный триггер, вход которого подключен к соответствующему входу накапливающего сумматора, и узел запоминания переноса, вход которого подключен к выходу счетного триггера соответствукяиего разряда, а выход ко входу счетного триггера последукяцего разряда, управляющие входы узлов запоминания переноса четных разрядов сумматора подключен к пер&ой тактовой шине сумматора, а нечетных разрядов - ко второй тактовой шине сумматора. Источники информации, принятые во внимание при экспертизе. 1.Авторское свидетельство СССР №281004, кл. q 06 F 7/39, 1968. 2.Авторское свидетельство СССР N«362295, кл. Q 06 F 7/38, 1969. 3.Папернов А. А. Логические осьновы цифровых машин и программирование, М., Наука, 1968, с. 158, рис. 8.3. тг тг Т п Ш Е

(Риг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1980 |

|

SU974369A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1979 |

|

SU842799A1 |

| Устройство для умножения | 1986 |

|

SU1401454A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

Авторы

Даты

1979-02-15—Публикация

1971-02-09—Подача