(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для умножения | 1975 |

|

SU1206773A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

1

Изооретение относится к вычислительной технике и может быть использовано в арифметических устройствах цифровых вычислительных машиЬ.

Известно устройство для умножения чисел, основанное на запоминании цифр переноса и выполненное Ъо сдвигом частичньдх воспроизведений вправо на один разряд, с анализом множителя, начиная с младших разрядов, и сохранением младшей части произведения в регистре множителя. Устройство содержит также триггер запоминания, сумматор - два дополнительных младших разряда. Ускорение умножения происходит за счет анализа двух цифр множителя 1.

Недостаток заключается в том, что в случае, если обе цифры равны , то ускорения умножения не будет, кроме того - устрйство характеризуется большим количеством оборудования.

Наиболее близким к предлагаемому является устройство, содержгицве регистры множителя, множимого, два регистра частичных произведений, два сумматора, схему управления и коммутатор. Работа этого устройства заключается в том, Что одновременно

осуществляется умножение множимого отдельно на старшую и младшую половину разрядов множителя. Добавлением множимого к содержимому первого

регистра частичных произведений управляют последовательно старшие множители, добавлением множимого к содержимому второго регистра частичных произведений управляют последоoвательно младшие разряды. Процессы идут одновременно, поэтому в целом уменьшается время умножения. Для. суммирования двух частичных произве-дений одно из них сдвигаетсяпп/4раз, где № - количество разрядов множи5мого и через коммутатор поступает на суммирование с другрм частичным произведением 2.

Недостаток устройства - низкое

0 быстродействие, определяемое тем, что перед сложением двух частйчийк произведений требуется дополнительное время на 1п/1 сдвигов.

Время умножения этого устройства

5 составляет

( -iVfc --tt/ сдьЛ а 1 ,1 c.f,t,. °е.

гдь; время одного сдвига еМ. ... время одного суммиро ;вавия;

0

mn - количество разрядов

множителя;

.(j-l) - время сдвига регистров множителя;

t 5 время сдвига частич ных произведений, результатов параллельноI го множения; . Ъс -С - времЯ: суммирования

двух частичных произведений.

Цель изобретения - повышения быстродействия.

Поставленная цель достигается тем, ЧТО устройство для умножения, содержащее первый и второй сдвигающие регистры частичных произведений соединенные поразрядно с сумматорами, коммутатор, регистр множимого, блок хранения множителя, блок управления, первый выход которого соединен со входами управления сдвигом первого и второго регистров частичных произведений и со входом управления сдвигом блока хранения множителя, второй выход блока управления соединен со входами записи певого и второго регистров частичных произведений,третий выход блока упрления соединен со стробирующим входом регистра множимого и входами установки регистров частичных произведений, четвертый выход блока управления подключен к управляющему входу коммутатора, содержит блок распределения множителя, содержащий элементы И, блок хранения множителя содержит два сдвигающих регистра соответственно четных и нечетных разрядов множителя, выходы четных элементов И блока распределения множителя подключены к соответствущим входам регистра нечетньк разрядов множителя, первые входы элементов И блока распределения множителя соединены со входами, множителя устройства, а вторые входы соединены с третьим выходом блока управления, выходы регистра множимого подключе,ны первым входом элементов И первой и второй групп, выход каждого элемента И первой группы соединен с первым входом соответствующего разряда первого сумматора, выходы элементов И второй группы соединены со входами коммутатора первой группы, вторые входы каждого элемента И первой группы .подключены к выходу регистра четных разрядов, второй вход каждого элемента И второй группы подключен к выходу регистра нечетных разрядов, выходы старших разрядов первого сдвигающего регистра частичных произведений соединены со вторыми входами разрядов первого сумматора со сдвигом на один разряд в сторону младших разрядов, выходы младших разрядов первого сдвигающего регистра частичных произведений

соединены со входами этого же регистра со сдвигом на один разряд в сторону младших разрядов, выходы разрядов второго регистра частичных

произведений соединены с первыми входами разрядов второго сумматора со сдвигом на один разряд в сторону младших разрядов, вторые входы разрядов BTCfporo сумматора соединены

С выходами коммутатора, входы втооой группы которого соединены с выходами разрйдов первого регистра частичных произведений.

Сущность изобретения заключается в следующем.

.Умножение осуществляется отдельн на четные, и нечетные разряды множителя. В этом случае для получения полного произведения не требуется сдвигать т/2 раз частичные произведения друг относительно друга. В прототиПе необходимость сдвигов обусловлена тем, что умножение происходит отдельно на старшую и младшую половину разрядов множителя.

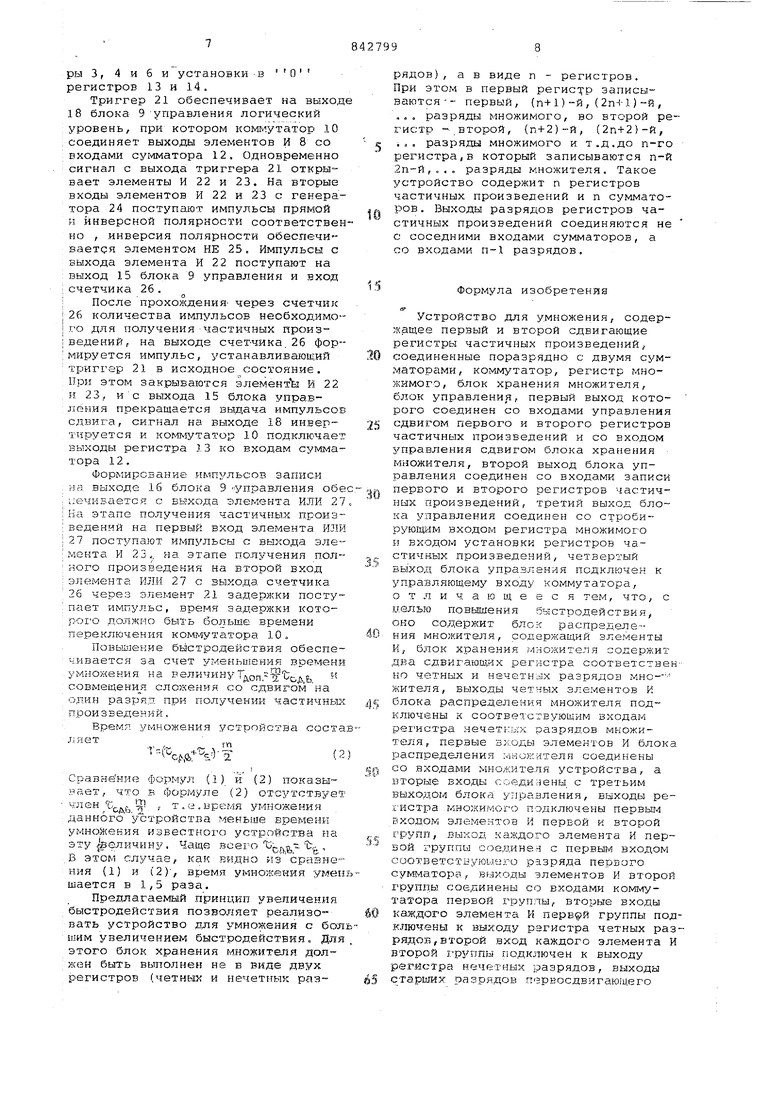

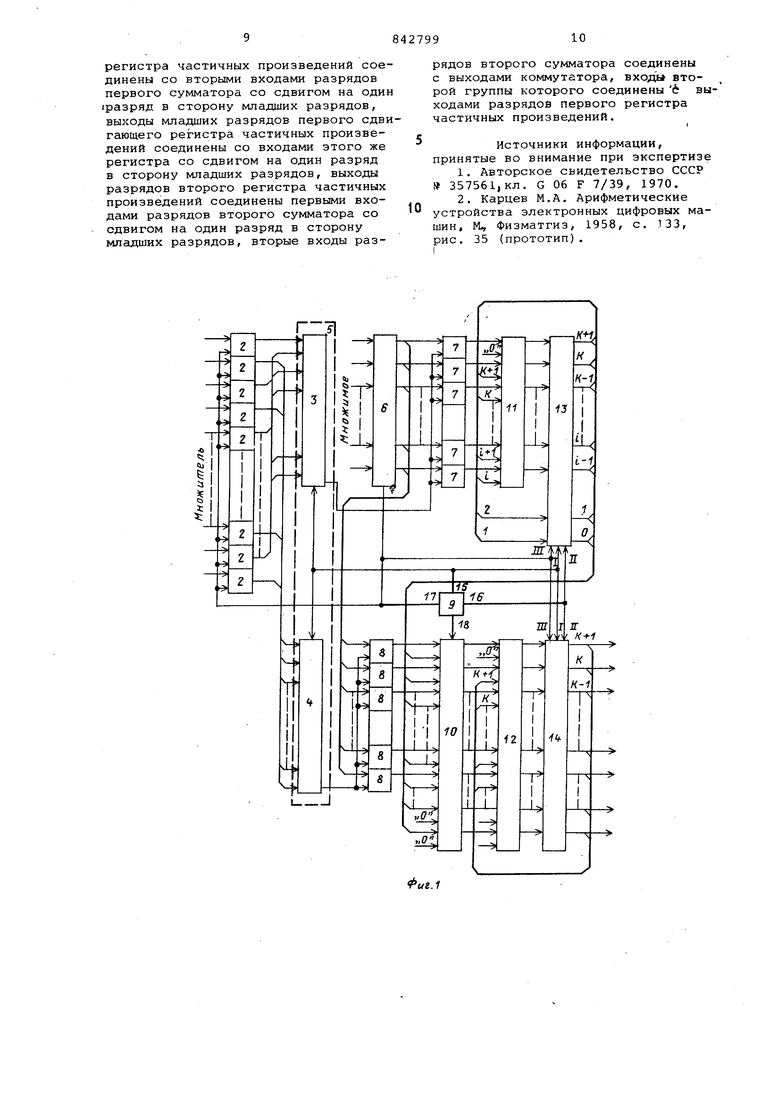

На фиг. 1 приведена структурная схема устройства для умножения; на фиг. 2 - схема умножения; на фиг.Зконструкция блока управления.

Устройство для умножения содержи блок Г распределения множителя, состоящий из элементов И 2, сдвигающий регистр 3 четных разрядов и сдвгающий регистр 4 нечетных разрядов, составляющие блок 5 хранения множителя, регистр б множимого, группу элементов И 6 - 8, блок 9 управления, ко1 1мутатор 10, сумматоры 11 и 12, сдвигающие регистры 13 и 14 частичных произведений, выходы 15 18 блока 9 управления. Выходы всех нечетных элементов И 2, блока 1 распределения множителя подключены к информационным входам регистра 3 четных разрядов, выходы всех четных элементов И 2 блока 1 распределения множителя подключены к информационным входам регистра 4 нечетных разрядов.

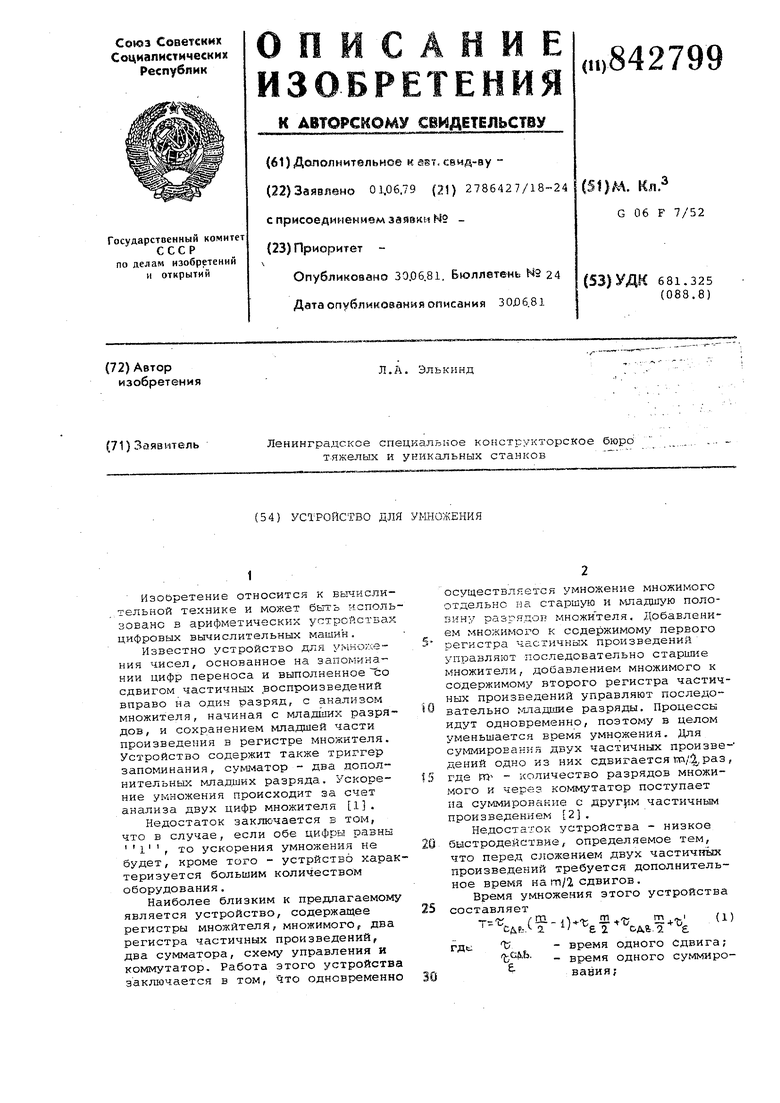

Стробирующие входы элементов И 2 блока 1 и регистра б множимого и входы установки в О регистров 13 и 14 подключены к выходу 17 юлока 9 управления,, Сигнал на выходе 17 производит запись множимого в регис б множителя в регистры 3 и 4, приче в регистр 3 обеспечивается запись четиых. разрядов, в регистр 4 - нечетных, в регистрах 13 и 14 записываются во всех разрядах нули. Выходы регистра б множимого соединены поразрядно с первыми входами сумматора 11 через элементы И 7 и с первыми входами сумматора 12 через элементы И 8 и коммутатор 10, стробирующие входы элементов И 7 и 8 соединены с выходами младших разряд регистров 3 и 4 соответственно. В процессе умножения.на первые входы сумматоров 11 и 12 поступают значения разрядов множимого или ло гические нули в зависимости от зна чения в анализируемом четном и нечетном разряде множителя, которые через выходы с регистров 3 и 4 стр бируют элементы И 7 ,и 8 соответственно. Вторые входы разрядов сумматоро 12и 11 соединены с выходами регистра 14 частичных произведений и птэловиной выходов регистра 13 частичных произведений соответственн причем соединение разрядов выполне но со смещением, при котором выход К-го разряда регистра 14 или 13 со динён со входом (K-l)-ro разряда сумматора 12 или 11,где К - номер ряда. Вторая половина выходов регистр 13частичных произведений соединен со второй половиной входов, соседни разрядов этого регистра. Каждый iвыход второй половины разрядов регистра 13 частичныхпроизведений соединен с (i-l) входом этого регистра, где i - номер разряда. Пер вая половина первой группы входов коммутатора 10 соединена с выходам элементов И 8, вторая половина пер вой группы входов коммутатора 10 подключена к шине логического О Такое подключение входов сумматоров 11 и 12 обеспечивает сдвиг результата суммирования в регистрах 13и 14 на один разряд в сторону младших разрядов на каждом такте суммир.ования, что дополнительно по вышает быстродействие без увеличения количества оборудования. Регист ры 3,4, 13 и 14- сдвигающие. Входы, управляющие их сдвигом соединены с выходом 15 блока 9 управления, на котором формируются импульсы управления сдвигом. Входы управления записью регистров 13 и . 14подключены к выходу 16 блока 9 управления, на котором формируются .импульсы записи. Управляющий вход коммутатора 10 подключен к выходу 18 блока 9 управления. В зависимости ,от сигнала на выходе 18 (логический О или 1 ) коммутатор 10 соединяет свои выходы поразрядно с первой группой входов или со второй. Первая группа входов подключена к выходам элементов .И 8 и к шине логическо.го О, вторая группа входов подключена к выходам сдвигающего регистра 13 частичных произведений. Устройство работает следующим об разом. Перед умножением обеспечивается запись множимого в регистР б множителя в регистры 3 и 4 и нулей в рег стры 13и 14 блоком 9управления, который формирует импульс на выхоя ,-., Умножение происходит в два получение двух частичных произведений и сложение их между собой для получения полного произведения. В течение первого этапа блок 9 формирует на выходе 18 сигнгш, присутствие которого на управляющем входе , коммутатора 10 обеспечивает соединение части входов коммутатора 10 с выходами элементов И 8 и части входов с шиной логического . О . В результате множимое с выходов регистра 6 через элементы И 8 и коммутатор 10 поступает на входы половины разрядов сумматора 12, на входы второй половины разрядов которого поданы логические О. Получение частичных произведений осуществляется паралттельно в двух регистрах 13 и 14 потактно путем сложения и сдвига. В каждом такте блок 9 управления формирует поочередно на выходах 16 и 15 импульсы записи и сдвига. При поступлении на входы записи регистров 13 и 14 импульса записи обеспечивается запись в эти регистры результатов суммирования в сумматорах 11 и 12. Импульс сдвига формируется на выходе 15 блока 9 и обесцечивает сдвиг содержимого в регистрах 3,4 13 и 14. Таким образом, обеспечивается сдвиг каждого результата суммирования в регистрах 13 и 14 относительно предьвдущего результата на два разряда. Блок 9 управления выдает (-1) импульсов записи ипч импульсов сдвига на управляющие входы регистров 3, 4,13,14. Второй этап (получение полного произведения) реализуется следующим образом. Блок 9 меняет значение сигналов на выходе 18 на противоположное-.при этом коммутатор 10 коммутирует поразрядно первое частичное произведение с выходов регистра 13 на входы сумматора 12 со сдвигом на один разряд. Блок 9 упрайле.чия формирует . на входе 16 импульс записи, которым обеспечивается запись в регистр 14 произведения. Таким образом, обеспечивается сложение двух частичных произйедений и получение полного произведения. Блок 9 управления содержит элементы 19 и 20 задержки, тригг-ер 21,элементы И 22,23,генератор 24,элемент НЕ 25, счетчик 26, элемент ИЛИ 27. При поступлении на устройство множения сигнала Пуск он постуает на выход 17 и через элемент 19 адержки на установочный вход RSриггёра 21; Время задержки элемента 19 должно; ыть больше времени записи в регистры 3, 4 и 6 и установки в О регистров 13 и 14.

Триггер 21 обеспечивает на выходе 18 блока 9 управления логический уровень, при котором коммутатор Ю соединяет выходы элементов И 8 со входами сумматора 12. Одновременно сигнал с выхода; триггера 21 открывает, элементы И 22 и 23. На вторые входы элементов К 22 я 23 с генератора 24 поступают импульсы прямой и инверсной полярности соответственно , инверсия полярности обеспечиваетдя элементом НЕ 25. Импульсы с выхода элемента И 22 поступают на выход 15 блока 9 управления и вход счетчика 26.

После прохождения- через счетчик

26количества импульсов необходимого для получения частичных произведений, на выходе счет-чика. 26 формируется импульс, устанавливающий триггер 21 в исходное состояние. При этом закрываются элементна И 22 и 23, и с выхода 15 блока управления прекращается выдача импульсов сдвига, сигнал на выходе 18 инвертируется и коммутатор 10 подключает выходы регистра 13 ко входгия сумматора 12.

Формирование импульсов записи на выходе 16 блока 9 «управления обепечивается с выхода элемента ИЛИ 27 На этапе получения частичных произведений на первый вход элемента ИЛИ

27поступают импульсы с выхода элемента И 23 на этапе получения полного произведения на второй вход элемента ИЛИ 27 с выхода счетчика 26 через элемент 21 задержки поступает импульс, время задержки которого должно быть больше времени переключения коммутатора 10.

Повышение быстродействия обеспечивается за счет уменьшения времени

умножения на величинуТлоп.

и

с.дь.

совмещени я сложения со сдвигом на один разряд при получении частичных произведений.

Время умножения устройства состаляет

(2

- -roi

Сравнение формул (1) и (2) показывает, что в формуле (2) отсутствует .д Ш , т.е.время умножения данного устройства меньше времени умножения известного устройства на эту величину. Чаще всегоС х t, ,В этом случае, как видно из сравнения (1) и (2), время умножения уменшается в 1,5 раза.

Предлагаемый принцип увеличения быстродействия позволяет реализовать устройство для умножения с бол шим увеличением быстродействия. Для этого блок хранения множителя должен быть выполнен не в виде двух регистров (четных и нечетных разрядов), а в виде п - регистров. При этом в первый регис р записываются-- первый, (п+1)-и, (2п+1)-й, ... разряды множимого, во второй регистр -.второй, {п+2)-й, (2п+2)-й, i,. разряды множимого и т.д.до п-го регистра,в который записываются п-й 2п-й,... разряды множителя. Такое устройство содержит п регистров частичных произведений и п сумматоров . Выходы разрядов регистров частичных произведений соединяются не с соседними входами сумматоров, а со входами п-1 разрядов.

Формула изобретения

.

Устройство для умножения, содержащее первый и второй сдвигающие регистры частичных произведений, соединенные поразрядно с двумя сумматорами, коммутатор, регистр множимого, блок хранения множителя, блок управлени, первый выход которого соединен со входами управления сдвигом первого и второго регистров частичных произведений и со входом управления сдвигом блока хранения множителя, второй выход блока управления соединен со входами записи первого и второго регистров частичных произведений, третий выход блока управления соединен со стробирующим входом регистра множимого и входом установки регистров частичных произведений, четвертый выход блока управления подключен к управляющему входу коммутатора, отличающееся тем, что, с целью повышения быстродействия, оно содержит блок распределения множителя, содержащий элементы И, блок хранения множителя содержит два сдвигающих регистра соответствено четных и нечетных разрядов мно- жителя, выходы четных элементов И блока распределения множителя подключены к соответствующим входам регистра нечетных разрядов множителя, первые входы элементов И блок распределения множителя соединены со входами множителя устройства, а вторые входы соединены с третьим выходом блока: управления, выходы регистра множимого подключены первым (ВХОДОМ элементов и первой и второй ррупп, выход каждого элемента И первой группы соединен с первым входом соответствующего разряда первого сумматора, выходы элементов И второ групды соединены со входами коммутатора первой группы, вторые входы каждого элемента И перв9й группы поключены к выходу регистра четных рарядов, второй вход каждого элемента второй группы подключен к выходу регистра нечетных разрядов, выходы старших разрядов первосдвигающего

регистра частичных произведений соединены со вторыми входами разрядов первого сумматора со сдвигом на один гразряд в сторону младших разрядов, выходы младших разрядов первого сдвигающего регистра частичных произведений соединены со входами этого же регистра со сдвигом на один разряд в сторону младших разрядов, выходы разрядов второго регистра частичных произведений соединены первыми входами разрядов второго сумматора со сдвигом на один разряд в сторону младших разрядов, вторые входы разрядов второго сумматора соединены с выходами коммутатора, входа второй группы которого соединены 6 выходами разрядов первого регистра частичных произведений.

Источники информации, принятые во внимание при экспертизе

0 устройства электеюнных цифровых машин, М Физматгиз, 1958, с. 133, рис. 35 (прототип).

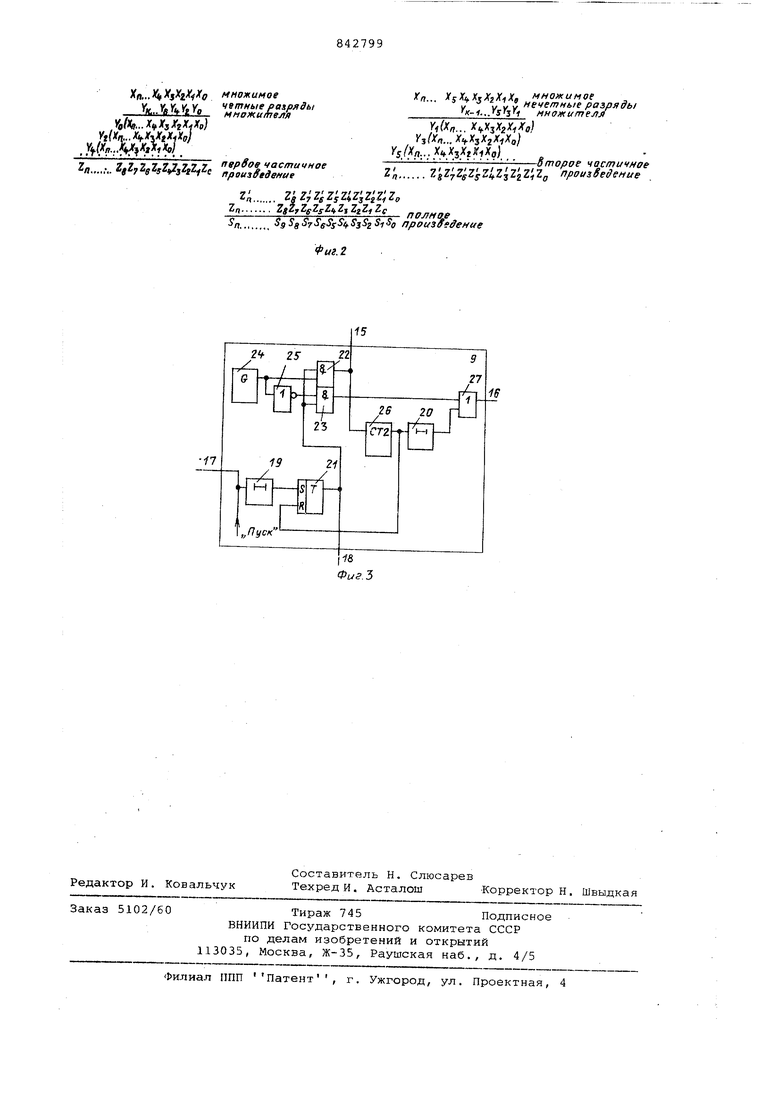

I Хл„ «V Xi iXiXo V Y V V Y ж,..йУУгУ y,l...X tXsXtXM /ifJf/t.A s fJffW ,.Ы т9 у 9 7 77777 Z/.,.,;.. ,«;r2# rVjfir / C множим Of eaiHtie разряды множиАвл пврвов чостичнве npOUtMeftUt z,; z,z;zizsZl,z,ziz,Zo z/.,, z,z, z, „„.. 5„SgSaSrSeSsSi SjSiSiSf произоевемие fn... .;j -r/;«.,, ... множителя yi(Xn... ) YjfXn... Х ХуХгХ Х,) У(Х„...)(1Хо) - -1 . .:. Второе частичное 2„2gZ Z Z Zl, произведение .

Авторы

Даты

1981-06-30—Публикация

1979-06-01—Подача