(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1971 |

|

SU647686A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для умножения | 1979 |

|

SU842799A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения | 1978 |

|

SU763897A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

1

Изобретение агносится: к области цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин.

Известно устройство для умножения, содержашеег регистр множителя, регистр множимого, элементы И, элементы ИЛИ. коммутатбр, сумматор, блок управления tl3Однако данное устройство обладает низким быстродействием вследствие временных затрат на распространение переносов.

Известное устройство для умножения, содержащее накапливающий сумматор, регистр множимого, регистр множителя, элементы И 2 . Однако вьшолнение накапливающего сумматора, как сз иматора со сквозным переносом, приводит к существенному снижению быстродействия в режиме непрерывных сложений, характерном для операции умножения.

Наиболее близким к предлагаемому по технической сущности является устройство для умножения, содержащее накапливающий сумматор, регистр множимого, регистр множителя, элемен- ты И, причем выходы регистра мно- жимого подключены к первым Входам соответствующизс, элементов И, выходы которых подключены к соответствую щим входам накапливакнцего сумматора,

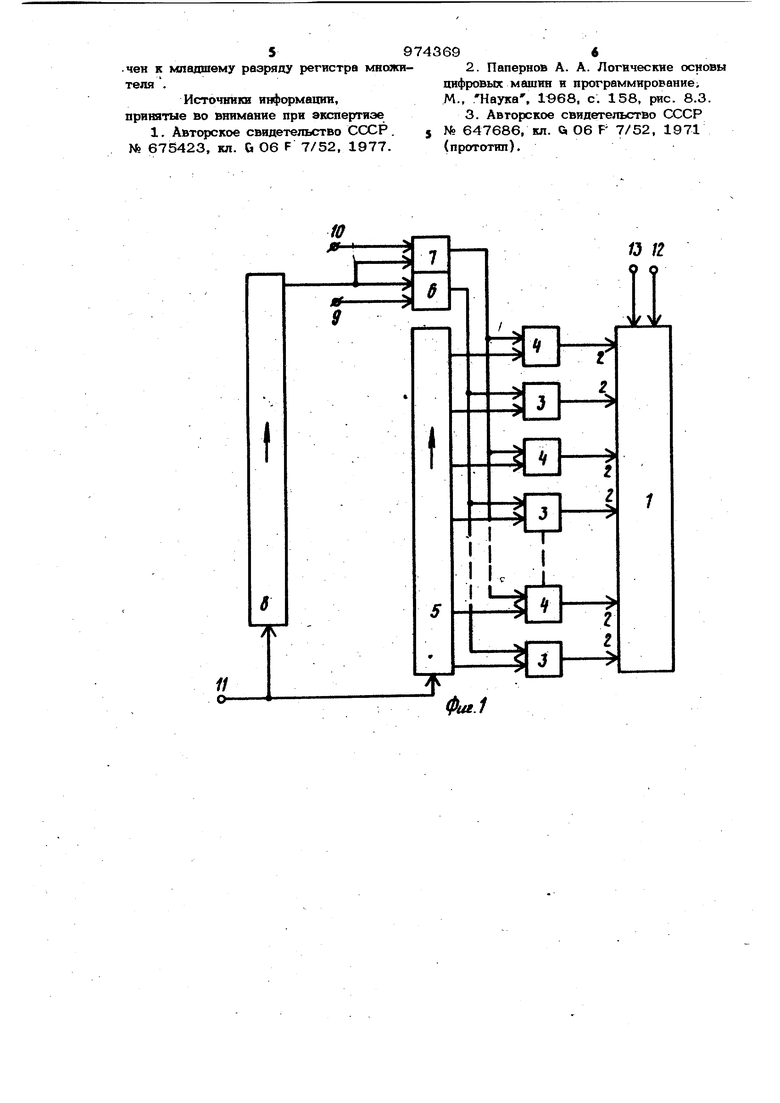

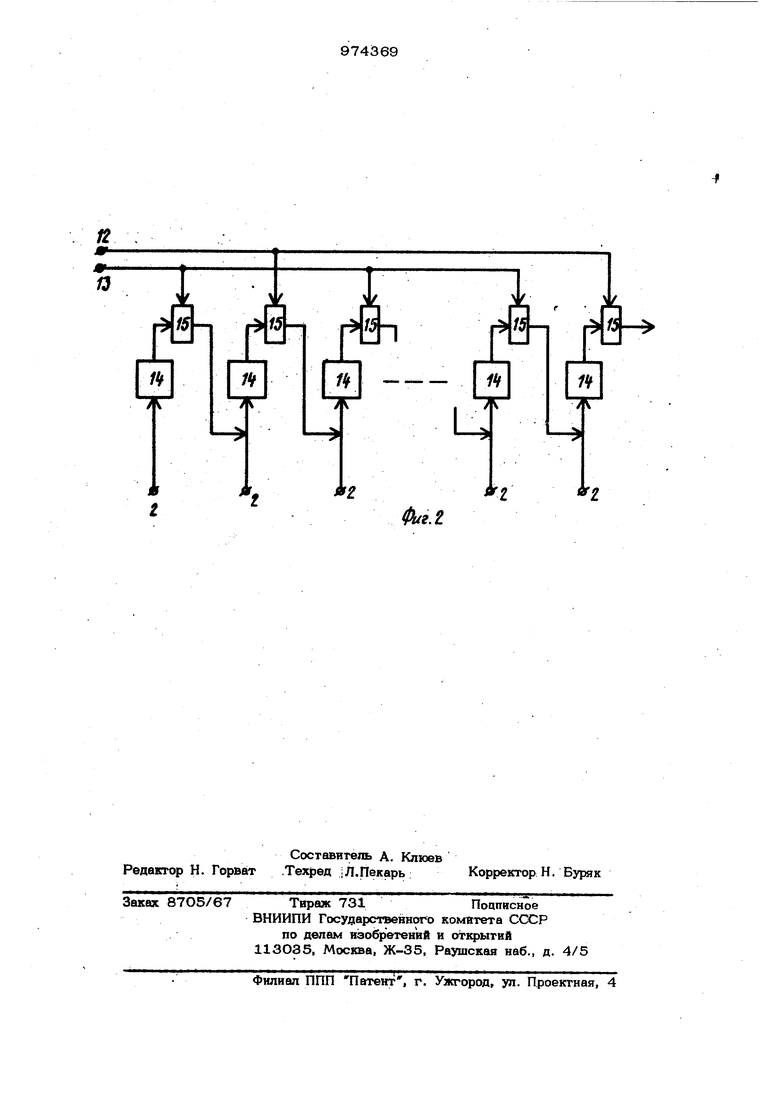

10 выход старшего разряда регистра множителя подключен к первому входу первого управляемого элемента И, второй вход которого подключен к первому управляк щему входу устройства, а выход - ко вто15рым входам четных элементов И, выход дополнительного старшего разряда регистра множителя подключен к первому входу BTopoms элемента И, второй вход которого подключен ковторому управляю20щему входу устройства, а выход - ко вторым входам нечетных элементов И, кроме того, накапливающий сумматор содержит в каждом разряде счетный триггер. Вход которого подключен к соогвегствующему ВХОДУ накапливающего сумматора, и узел запоминания переноса, вход которо го подключен к выходу счетного триггера соответсвующего разряда, а выход - ко входу счетного триггера последукшего разряда, управляющие входы узлов запоминания переноса четных разрядов сумма тора подключены к первой тактовой шине -сумматора, а нечетных разрядов - ко вто -рой тактовой, шине сумматора 33 . Такое устройство имеет низкое быстро действие вследствие того, что сдвиг содержимого регистров множителя и мно жимого осуществляется последовательно. Целью изобретения является увеличение быстродействия. Поставленная цель достигается тем, что устройство для умножения,.- содержащее накапливающий сумматор, регистр, множимого, регистр множителя, элементы И, причем выходы регистра множимого подключены Кпервым Входам соответствующих элементов И, выходы которых подключены к соответствунидим входам накапливающего сумматора, вторые входы четных элементов И подключены к выходу первого управляете ого элемента И, первый вход которого подключен к. младшему разряду регистра множителя, а второй его вход соединен с первым управлякнцим входом устройства вторые входы нечетных элементов И подключень к выходу второго управляемого элемента И, первый вход которого соеди н нен со вторым управдякиим входом устройства, содержит связь второго входа второго управляемого элемента И с млад шим разрядом регистра мноясителя. На фиг. 1 изофажена схеме устройства для умножения; на фиг. 2 - схема .накапливающего сумматора. Устройство содержит накаляиваквдий cyjwiMaTop 1, ко нхрдам разрядов 2 которого подключены выходы нечетных и четных элементов И 3 и 4, регистр множимого 5, первый .и второй управляемые . элементы И 7 и 6, регистр множителя 8 . ,управлякяци&( входы устройства 9 и 10, тактовые шины устройства 11, 12 и 13, счетные триггеры 14, узлы запоминания переноса 15. Устройство работает следующим образом. Множимое и множитель заносятся в регистры-множл ого и множителя 5 и 8 после чего на управл5}ющие входы 9 и 10 подаются тактовые импульсы. Регистры 5 и 8 сдвиговые, После подачи первохо тактового импульса на вход 10 цифра, находящаяся в младшем разряде регистра 8, управляет подачей в сумматор 1 четных разрядов регистра 5. Затем подается тактовый импулыЗ на вход 9 и младший разряд регистра 8 управляет Передачей б умматор 1 нечетнЬвс разрядов регистра 5. После чего производится сдвиг в регистре 8 в сторону младших разрядов, а в регистре 5 - в сторону старших разрядов подачей тактового импульса на шину 11 и процесс повторяется. Одновременно с подачей управляющего сигнала на вход 10 подается тактовый импульс на шину 12, управлякнций выдачей из узлов запоминания четных разрядов на нечетные разряды накапливающего сумматора. Аналогично с подачей управляющего сигнала на вход 9 подается тактовый импульс на шину 13, управляющий выдачей информации из узлов запомина- . ния нечетных разрядов на четные разряды накапливающего .сумматора. Совмещение сдвига множимого и множителя позволяет сократить время вычисления произведения по сравнению с из- , вестным на п /, где п - разрядность множителя, время одного сдвига. Формула изобретения Устройство для умножения, содержащее накапливающий сумматор, регистр множимого, регистр множителя, элементы И, причем выходы регистра множимого подключены к первым входам соответствующих элементов И, выходы которых подклзючены к соответствующим входам накапливающего сумматора, вторые входы четных элементов И подключены к выходу первого элемента И, первый вход которого подключен к младшему разряду регистра множителя, а второй его вход соединен с первым управляющим входом устройства, вторые входы ;нечетных элементов И подключены к выходу второго управляющего элемента И, первый вход которого соединен Со вторым управляющим входом устройства, входы регистров .множимого и множителя подключены к первой тактовой шине устройства, управляющий вход узлов зшюмннания переноса четных разрядов суммато- . ра подключен ко второй тактовой шине устройства, а нечетных разрядов - к третьей тактовой шине устройства, отличающееся тем, что, с целью увеличения быстродействия устройства, второй вход второго управляемого элемента И подклю чен к младшему разряду регистра множителя .

Источники информации, принятые во внимание при экспертизе

(прототип).

о п

:

9 о

б

11

оib

I

rtl

t

Фи1.1

Авторы

Даты

1982-11-15—Публикация

1980-11-11—Подача