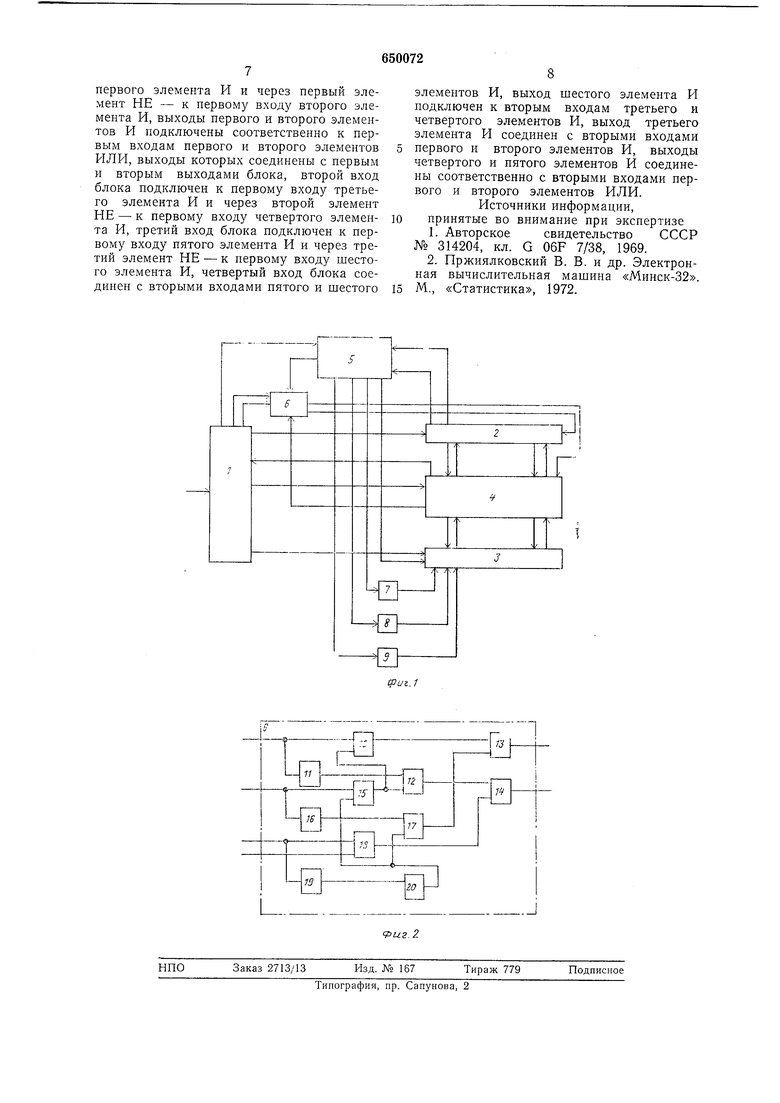

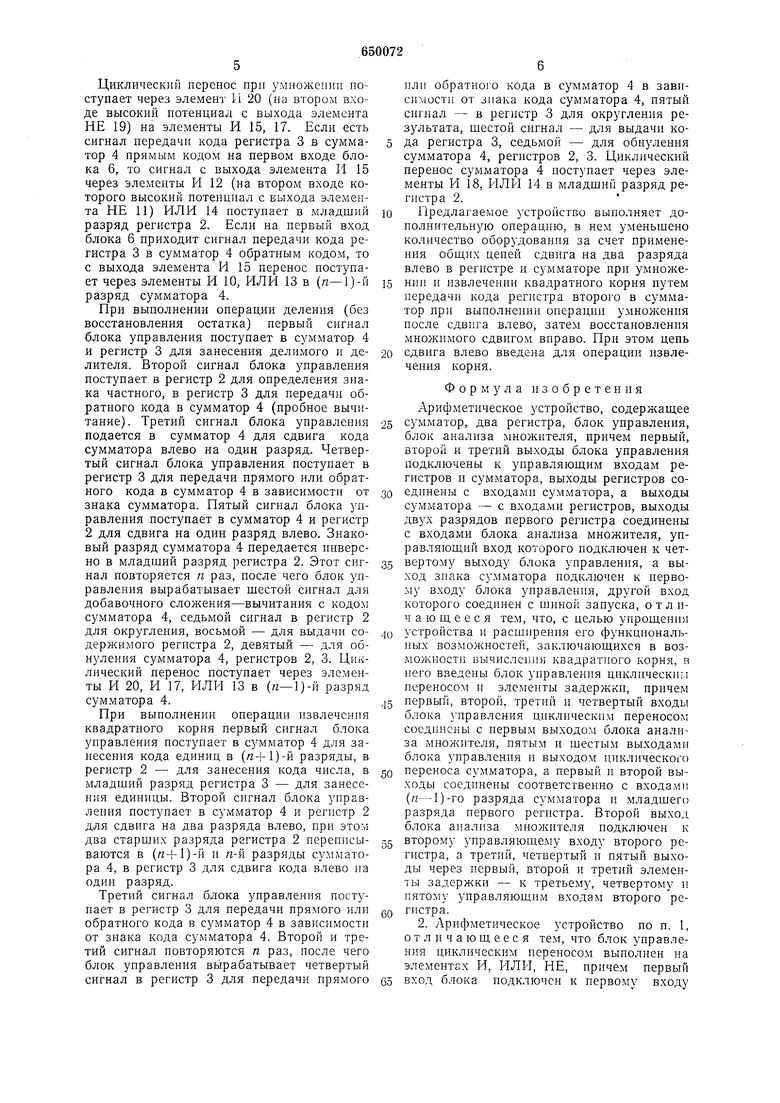

Поставленная цель достигается также тем, что блок управления циклическим переносом выполнен на элементах И, Р1ЛИ, НЕ, причем первый вход блока подключен к первому входу первого элемента PI и через первый элемент НЕ - к первому входу второго элемента И, выходы первого и второго элементов И подключены соответственно к первым входам первого и второго элементов ИЛИ, выходы которых соединены с первым и вторым выходами блока, второй вход блока подключен к первому входу третьего элемента И и через второй элемент НЕ - к первому входу четвертого элемента И, третий вход блока подключен к первому входу пятого элемента И и через третий элемент НЕ - к первому входу шестого элемента И, четвертый вход блока соединен с вторыми входами пятого и шестого элементов И, выход шестого элемента И подключен к вторым входам третьего и четвертого элементов И, выход третьего элемента И соединен с вторыми входами первого и второго элементов И, выходы четвертого и пятого элементов И соединены соответственно с вторыми входами первого и второго элементов ИЛИ.

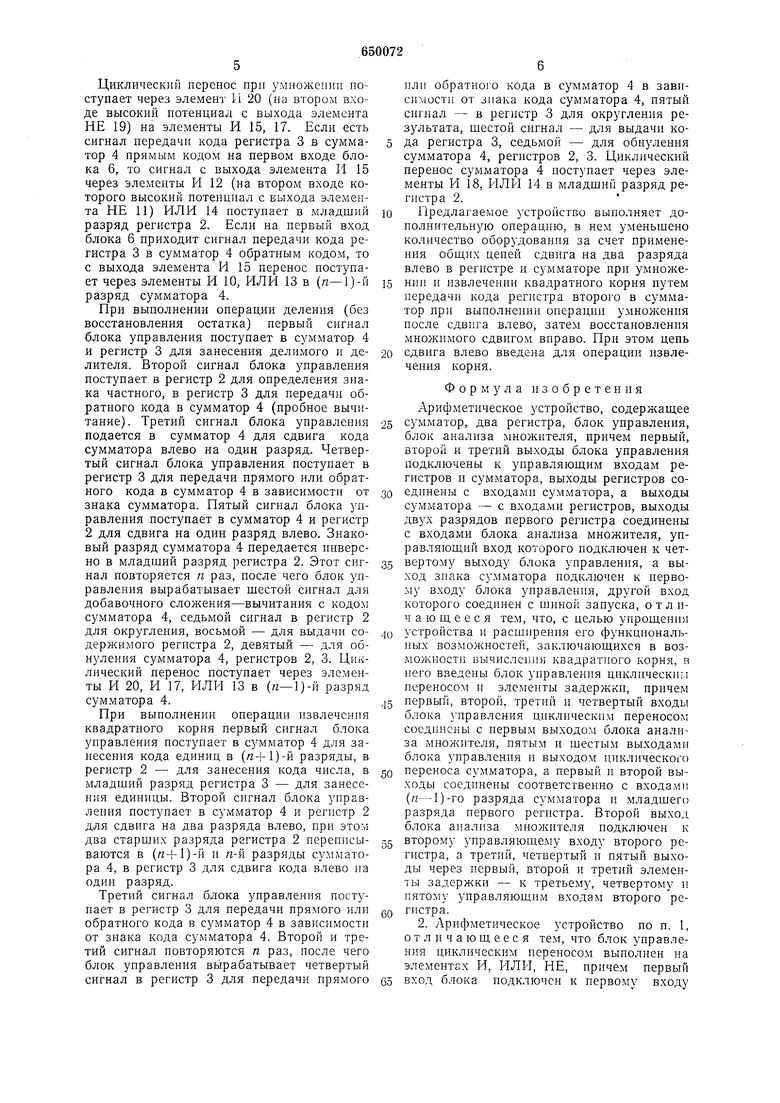

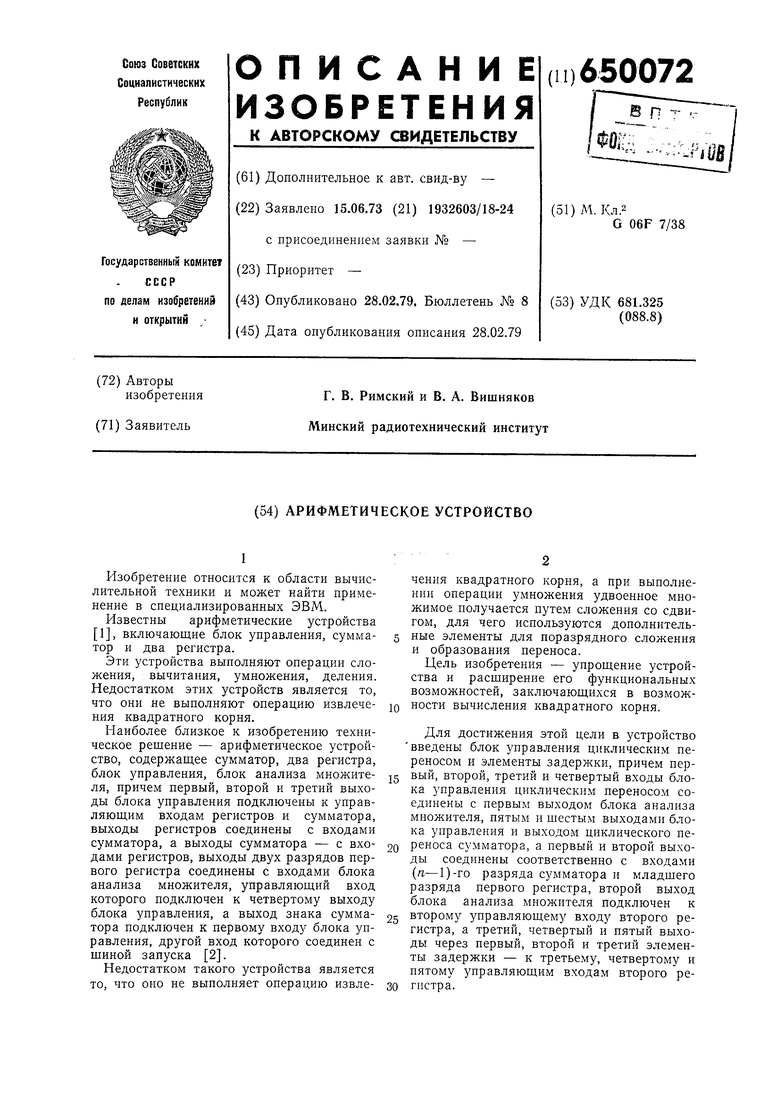

На фиг. 1 представлена структурная схема арифметического устройства; на фиг. 2 показан блок управления циклическим переносом.

Первый, второй и третий выходы блока 1 управления соединены с управляюш,ими входами регистров 2 и 3 и сумматора 4, входы которого соединены с выходами регистров 2 и 3, а выходы подключены к входам этих регистров. Выходы двух разрядов регистров 2 подключены к входам блока 5 анализа множителей, первый выход которого подключен к первому входу блока 6 управления циклическим переносом; второй выход - к второму управляюшему входу регистра 3, а третий, четвертый и пятый выходы через элементы задержки 7, 8 и 9 - к третьему, четвертому и пятому управляюшим входам регистра 3. Управляющий вход блока 5 анализа множителя подключен к четвертому выходу блока 1 управления. Второй вход блока 6 управления циклическим переносом подключен к пятому выходу блока 1 управления, а третий вход - к выходу циклического переноса сумматора 4. Выходы блока 6 управления циклическим переносом подключены к входу (п-1)-го разряда сумматора 4 и входу младшего разряда регистра 2.

Блок управления циклическим переносом включает элементы И 10, НЕ 11, И 12, ИЛИ 13, ИЛИ 14, И 15, НЕ 16, И 17, И 18, НЕ 19, И 20. Первый, второй и третий входы блока подключены к входам элементов И 10, 15, 18 и через элементы НЕ 11, 16, 19 - к входам элементов И 12, 17, 20. Четвертый вход блока соединен с вторыми входами элементов И 18, 20. Выход элеменча И 20 соединен с вторыми входами элементов И 15, 17. Выход элемента И 15 соединен с вторыми входами элементов И 10, 12, выходы которых подключены к входам элементов ИЛИ 13, 14, дрзгие входы которых нодключены к выходам элементов И 17, 18, а выходы - к первому и второму выходам блока 6 унравления циклическим переносом.

Устройство работает следуюш им образом.

При выполнении операции сложения- вычитания блок 1 управления вырабатывает сигналы для занесения операндов в сумматор 4 и регистр 3, для передачи операндов из регистра 3 в сумматор прямым или обратным кодом, для анализа переполнения сумматора, которые поступают с регистра 3 на управляющие входы сумматора. Пиклический перенос в этом случае через элементы И 20 (нет извлечения корня), И 17 (нет умножения) ИЛИ 13 в («-1)-й разряд сумматора 4.

При выполнении операции умножения по

сигналу из блока 1 управления осуществляется занесение множимого в регистр 3 и множителя в регистр 2. Второй сигнал поступает в регистр 2, в знаковом разряде которого образуется знак произведения.

Третий сигнал блока управления поступает в блок 5 анализа множителя, который анализирует два старших разряда регистра 2 и триггер запоминания регистра 2.

При коде двух разрядов множителя 00

nil и триггера запоминания О и 1 соответственно код регистра 3 не передается в сумматор 4. При коде 01, 10 и О триггера запоминания код регистра 3 нередается в сумматор 4 прямым кодом. При 11 и О блок

5 анализа множителей вырабатывает сигнал сдвига регистра 3 влево на один разряд, затем через элемент задержкн 8 - сигнал передачи кода регистра 3 в сумматор 4 прямым кодом, через элемент задержки 7 - сигнал сдвига кода регистра 3 вправо на один разряд.

При коде 00 и 1 блок 5 анализа множителя вырабатывает сигнал сдвига влево на

один разряд, через элемент задержки 9 - сигнал передачи кода регистра 3 в сумматор 4, обратным кодом через элемент задержки 7 - сигнал сдвига регистра 3 вправо на одннразряд. Сигнал блока 1 управления поступает в сумматор 4 и в регистр 2 для сдвига влево на два разряда. Эти сигналы блоком управления повторяются п/2 раз (п - разрядность множителя). Затем вырабатываются сигналы для обработки триггера запоминания в блоке 5 анализа множителя, для сдвига на один разряд влево сумматора 4 и регистра 2, для округления результата регистра 2, для выдачи результата регистра 2 и для обнулення сумматора 4 и регистров 2, 3. Циклический перенос при умножении поступает через элемеит И 20 (на втором входе высокий потенциал с выхода элемента НЕ 19) на элементы И 15, 17. Если есть сигнал передачи кода регистра 3 в сумматор 4 пряным кодом на первом входе блока 6, то сигнал с выхода элемента И 15 через элементы И 12 (на втором входе которого высокий потенциал с выхода элемента НЕ 11) ИЛИ 14 поступает в младший разряд регистра 2. Если на первый вход блока 6 приходит сигнал передачи кода регистра 3 в сумматор 4 обратным кодом, то с выхода элемента И 15 перенос поступает через элементы И 10, ИЛИ 13 в (л-1)-й разряд сумматора 4. При выполнении операции деления (без восстановления остатка) первый сигнал блока управления поступает в сумматор 4 и регистр 3 для занесения делимого и делителя. Второй сигнал блока управления поступает в регистр 2 для определения знака частного, в регистр 3 для передачи обратпого кода в сумматор 4 (пробное вычитание). Третий сигнал блока управления подается в сумматор 4 для сдвига кода сумматора влево на один разряд. Четвертый сигнал блока управления поступает в регистр 3 для передачи прямого или обратного кода в сумматор 4 в зависимости от знака сумматора. Пятый сигнал блока управления поступает в сумматор 4 и регистр 2 для сдвига на один разряд влево. Знаковый разряд сумматора 4 передается инверсно в младший разряд регистра 2. Этот сигнал повторяется л раз, после чего блок управления вырабатывает шестой сигнал для добавочного сложения-вычитания с кодом сумматора 4, седьмой сигнал в регистр 2 для округления, восьмой - для выдачи содержимого регистра 2, девятый - для обнуления сумматора 4, регистров 2, 3. Циклический неренос поступает через элементы И 20, И 17, ИЛИ 13 в (л-1)-й разряд сумматора 4. При выполнении операции извлечения квадратного корня первый сигнал блока управления поступает в сумматор 4 для занесения кода единиц в (л+1)-й разряды, в регистр 2 - для занесения кода числа, в младший разряд регистра 3 - для занесения едииицы. Второй сигнал блока управления поступает в сумматор 4 и регистр 2 для сдвига на два разряда влево, при этом два старших разряда регистра 2 перепись ваются в (л-f 1)-й и я-й разряды сумматора 4, в регистр 3 для сдвига кода влево иа один разряд. Третий сигнал блока управления поступает в регистр 3 для передачи прямого или обратного кода в сумматор 4 в зависимости от зиака кода сумматора 4. Второй и третий сигнал повторяются л раз, после чего блок управления вьфабатывает четвертый сигнал в регистр 3 для передачи прямого или обратного кода в сумматор 4 в зависимости от зиака кода сумматора 4, пятый спгнал - в регистр 3 для округления результата, шестой спгнал - для выдачи кода регистра 3, седьмой - для обнуления сумматора 4, регистров 2, 3. Циклический перенос сумматора 4 поступает через элементы И 18, ИЛИ 14 в младший разряд регистра 2. Предлагаемое устройство выполняет дополнительную операцию, в нем уменьшено количество оборудования за счет применения обш,их ценей сдвига на два разряда влево в регистре и сумматоре при умножении и извлечении квадратного корня путем передачи кода регистра второго в сумматор при выполнении оиерации умноження иосле сдвига влево, затем восстановления множпмого сдвигом вправо. При этом цепь сдвига влево введена для операции извлечения корня. Формула нзобретения Арифметическое устройство, содерл :ащее сумматор, два регистра, блок управления, блок аиализа множителя, причем первый, второй и третий выходы блока управления подключены к управляюшим входам регистров и сумматора, выходы регистров соединены с входами сумматора, а выходы сумматора - с входами регистров, выходы двух разрядов первого регистра соединены с входами блока аналнза множителя, управляюш,ий вход которого подключен к четвертому выходу блока управления, а выход зиака сумматора подключен к нервому входу блока управления, другой вход которого соединен с шиной заиуска, о т л ич а ю ш, е е с я тем, что, с целью уирошения устройства и расширения его функциональных возможностей, заключаюшихся в возможности вычисле1П1я квадратного корня, в него введены блок уиравлеиия циклическим переносом п элементы задержкн, нрнчем первый, второй, третий и четвертый входы блока управления циклическим переносом соединены с первым выходом блока анализа мнол ителя, пятым и шестым выходами блока управленпя и выходом циклического переноса сумматора, а первый и второй выходы соединены соответственно с входами (п-1)-го разряда сумматора и младшего разряда первого регистра. Второй выход блока анализа миожителя иодключен к второму управляющему входу второго регистра, а третий, четвертый и пятый выходы через первый, второй и третий элементы задержки - к третьему, четвертому и иятому управляющим входам второго регистра. 2. Арифметическое устройство по п. 1, отличающееся тем, что блок управления циклическим иереносом выполнен на элементах И, ИЛИ, НЕ, причем первый вход блока подключен к первому входу

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

Авторы

Даты

1979-02-28—Публикация

1973-06-15—Подача