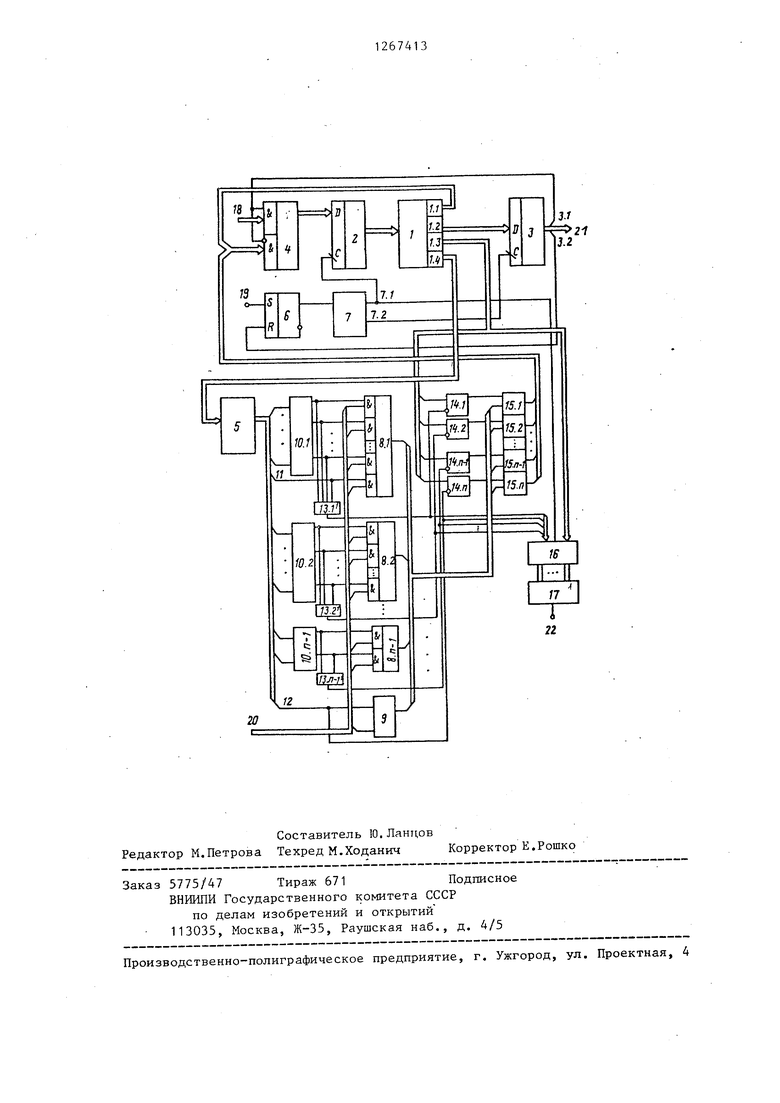

f1 Изобретение относится х автоматике и вычислительной технике и может быть использовано при построении центрапьных устройств управления ЭВМ и вычислительных устройств с микроnporpaMMHbUvi управлением о Цель изобретения - сокращение оборудования за счет уменьшения объе ма памяти микрокоманд. На чертеже приведена функциональ нал схема микропрограммного, устройства управления с контролем. Микропрограммное устройство управ ления с контролем содержит блок 1 памяти микрокоманд с выходами 1,, -l регистр 2 адреса, регистр 3 микрокоманд с выходами 3, конца команды и 3 конца работы, коммутатор 4 ,реса, делшфратор 5 логических условий, триггер 6 пуска, генератор 7 тактовых импульсов с первым 7, и вторым 7, выходами, с nepiaoro 8, по (п-1)-й коммутаторы логических условий, элемент И 9, с первого по (п-1)-й блоки элементов ИЛИ ,. первый выход 11 дешифратора логических условий, второй выход 12 дешргфратора логических условий, вторую группу из элементов ИШ 3 групп-у из элементов И |Л,--14(т; первую группу из элементов ШШ 15., -15,-,, блок элементов И 16, элемент ИШа 7, вход 18 кода команд, вход 19 пускаэ вход 20 логических условий, выход 21 управления и выход, 22 неисправностиМикропрограммное устройство управления с контролем работает следую щим образом, В исходном состоянии все элементы находятся в нулевом состоянии; в разряде регис ра 3 микpOF oмaндJ, соответствующем выходу 3, , записана единица. Цепи приведения элементов устройства в исходное состояние условно не показаны„ По сигналу .Пуск с входа 19 устройства, постуггающему на вход, установки в единицу триггера 6,, последни устанавливается в единичное состояни При этом на выходах 7 и 7, генератора 7 возбуждаются последовательнос ти тактовых импульсов 1, и 2 первому тактовому импульсуI,, 5 посту пающему на синхровход регистра 2 адреса, последний открывается. При это код операции., являющейся адресом пер вой микрокоманда вьполняемой гл.жропрограммы, через коммутатор 4 .гюсту3нает на информационньй вход регистра 2 и записывается Б нем. По записанному в регистре 2 адресу из блока 1 памяти выбирается соответствующая микрокоманда и поступает на его выходы 1, -l.. При наличии сигнала на синхровходе регистра 3 операционная часть микрокоманды с выхода 1 блока 1 па.чяти поступает на информащ-юнный вход регистра 3, Сигналы микроопераций с регистра 3 поступают на выход 21 устройства, При формировании адреса очередной микрокоманды возможны следующие реяшмы работы устройства; форм.ирован11е адреса очередной микрокоманды при выполнении линейных участков микропрограмм без проверки логических (первый режим) J формирование адреса очередной микрокоманды при реализации условных переходов (второй ), Рассмотрим работу устройства в этих режимах. Первый peHctiM, При считывании микрокоманды из блока 1 памяти адрес очередной микрокоманды форг-шруется следующим образом. Немодифицируемая часть адреса (старшие разряды адреса) очередной микрокоманды с выхода 1 блока 1 памяти поступает на соответствующие разряды информационного входа коммутатора 4. Ютадшие разряды адреса (модифицируемые) с выхода 1J бло.ка 1 памяти поступают на соответствующие входы элементов И группы элементов И 14;-14.,, Так как в поле 1 блока 1 записан нулевой код, то на вьшодах дешифратора 5 и ; на выходах коммутаторов ,,, и элемента И 9 присутствует нулевой потенцртап и элементы И 14.|-l4f открыты по соответствующр1ь входам. Таким образом 1 шадшие разряди адреса через группу элементов И 14., - - РУПпу элементов ИЛИ 15., 15,, поступают на соответствующие разряды информационного входа коммутатора 4 адреса. Ввиду отсутствия сигнала мкpooпepaции Конец команды адрес очередной микрокоманды через .ко {утатср 4 поступает на информационный вход регистра 2 адреса. При поступлении очередного тактового импульса Т адрес очередной шкpoкoманды затесывается в регистр 2 адреса. Далее устройство работает в этом режиме аналогично oпиcaннo ry алгоритму.

312

Второй режим. Работу устройства во втором режиме рассмотрим в следующих случаяхг

при проверке одного логического условия;

при проверке i логических условий (i : п k, где п - максимальное число одновременно проверяемых логических условий, к - число модифицируемых разрядов адреса очередной микрокоманды);

при проверке логических условий в случае п k;

при проверке логических условий в случае п k,

Если при выполнении текущей микрокоманды необходимо проверить значение одного логического условия и произвести ветвление микропрограммы, то на выходе 1 блока 1 памяти бу.дет код этого логического условия, Значения логических условий с входа 20 поступают на соответствующие входы коммутаторов логических условий и элемента И 9. В данном случае модификация адреса осуществляется только по младшему разряду, какое бы условие не проверялось (первого коммутатора 8 логических условий), его значение поступает на элемент ИЛИ 15 группы элементов ИЛИ 15,-15г, и через него на соответствующий разряд информационного входа коммутатора А адреса. Таким образом, адрес очередной микрокоманды определяется следующим выражением

ACT .,

исп

где А (j - значение старших (немодифицируемых) разрядов адреса;

- знак конкантенации; а - значение модифицируемых

разрядов адреса; . а - значение промодифицированного значения младшего разряда адреса.

При проверке i(i п ) логических, условий на выходе 1ц блока 1 памяти появляется код проверяемых логических условий. Этот код дешифрируется дешифратором 5. Сигнал с выхода дешифратора 5, соответствующий проверяемой комбинации i логических условий проходит через соответствующие элементы ИЛИ первого 10, -(n-i)-ro 10n-i блоков элементов ИЛИ на управляющие

134

входы коммутаторов 8,-St. На выходах этих коммутаторов появляются сигналы проверяемых логических условий, которые и модифицируют i младших разрядов адреса аналогично описанному алгоритму..

Если при выполнении текущей микрокоманды проверяется п логических условий (число проверяемых логических условий равно числу модифицируемых разрядов адреса), то адрес очередной микрокоманды определится выражением

А А

т а„ап,

Зла,

Модификация младших разрядов адреса при этом происходит аналогично описанному горитму. Модификация п-го разряда происходит следующим образом. На втором выходе 12 дешифратора 5 появляется единичный сигнал, который открывает элемент И 9, При этом сигнал п-го логического условия с входа 20 устройства поступает через элемент И 9 на второй вход элемента ИЛИ 15t-| . Далее формирование адреса очередной микрокоманды происходит аналогично описанному алгоритму.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, коммутатор адреса, генератор тактовых импульсов, триггер пуска, группу из п элементов И (п - количество младших разрядов адреса блока памяти микрокоманд) и первую группу из п элементов ИЛИ, причем первая группа информационных входов коммутатора адреса соединена с группой входов кода команды устройства, выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, i-й выход поля адреса старших разрядов которого соединен соответственно с i-м информационным входом второй группы коммутатора адреса (i 1,m, m - количество старших разрядов адреса блока памяти микрокоманд), j-й информационный вхо второй группы которого (j m t1, m -t- n) соединен с выходом к-го элемента ИЛИ первой группы (к 1,п), §12 первый вход которого с выходом п-го элемента И группы, прямой вход которого соединен с к-м выходом поля адреса младших разрядов блока памяти микрокоманд,, выход поля микро операций КОТО130ГО соединен с информационным входом регистра микрокоманд, выход поля микроопера1Д1й которого подключен к выходу управления устройства, выход признака конца команды регистра микрокоманд соединен с управляющим входом коммутатора адреса, выход признака конца работы регистра микрокоманд соединен с входом установки в О триггера nycKaj вход установки в 1 которого подключен к вхо,1ту пуска устройства вы ход триггера пускгг соединен с входом запуска генератора тактовых импульсов, первый и второй выхода которого соединены соответственно с синхро™ входаг-м регистра адреса и регистра микрокоманд, отличающееся тем, что, с целью сокращения оборудования за счет уменьшения объема па мяти .микрокоманд, оно содерядат дешиф ратор логических условий, группу из блоков элементов ИЛИ вторую группу из элементов ИЛИ, группу из п-1 коммутаторов логических условий, элемент И, блок элементов И и элемент ИЛИ, причем выход поля логических условий блока памяти микрокоманд -соединен с входом дешифратора логических условий, первый выход которого соединен с первым входом первого элемента Ш1И второй группы и с первьм управляющим входом первого ко мутатора группы остальные управляющие входы которого соединеШ) с одноименными входами первого элемента ИЛ второй группы и с одноименными выходами первого блока элементов- ИЛИ группы, второй вгзгход дешифратора логичес-ких условий соединен с первым входом элемента И, с инверсным входом п-го элемента И группы и с первым входом блока элементов И,, остальные выходы дешифратора логических условий соединены с входш и всех блоков элементов ИЛИ группы, выходы с второго по (п 1) блоков элементов ИЛИ группы соедашены с одноименными входами одноименных элементов ИЛИ второй группы и с одноименньПШ управляющими входами одноименных коммутаторов группы, информационные входы всех коммутаторов группы и второй вход элемента И подключены поразрядно к входу логических условий устройства, выходы с первого по (п-1)й элементов ИЛИ второй группы соединены соответственно с инверсными входами одноименных элементов И группы и с второго по входами блока элементов И, выходы с первого по (п-1)-и коммутаторов группы соединены с вторыми входами одноименных элементов И.1М первой группы, второй вход п-го элемента ИЛИ первой группы соединен с выходом элемента И, с (п-М)-го по 2п-й входы блока элементов И соединены соответственно с первого по п-й вьпсодами поля адреса младших разрядов блока памяти микрокоманд, (2п+1)-й вход блока элементов И соединен с первым вькодом генератора тактовых импульсов, вьга;оды блока элементов И соедииены с входами элемента ИЛИ, выход которого подключен к выходу неисправности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении центральных устройств построения ЭВМ и вычислительных устройств с микропрограммным управлением. Цель изобретения - сокращение оборудования за счет уменьшения объема памяти микрокоманд. Устройство содержит блок памяти микрокоманд, регистр адреса, регистр микрокоманд, коммутатор адреса,дешифратор логических условий, триггер пуска, генератор тактовых импульсов, группу коммутаторов логических условий, элемент И, группу блоков элементов ИЛИ, две группы элементов ИЛИ, группу элементов И, блок элементов И и элемент ИЛИ. Совокупность блоков позволяет достигнуть це- tg ли изобретения. 1 ил. (Л

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1091160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-11—Подача