1

Изобретение относится к вычислительной технике и может быть нспользовано в ЭВМ для локализации неисправностей.

Современные высокопроизводительные ЭВМ обычно бывают снабжены встроенной аппаратурой для локализаций неисправностей с точностью до группы типовых элементо-в замены, т. е. группы :печатных плат с интегральными схемами. Для локализации неисправности с точностью до интегральной схемы для последующей их замены иснользуются стенды проверки типовых элементов замены, которые при этом бывают с ручным и автоматическим управлением .

Комплектование ЭВМ автоматическим стендом для индивидуального обслуживания приводит к значительному удорожанию стоимости ЭВМ. Ручные стенды имеют невысокую стоимость, но требуют много времени на проверку, что значительно снижает ремонтопригодность ЭВМ.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство 2. Это устройство содержит входной регистр, буферный блок памяти, блок сравнения, преобразователь параллельного кода в последовательный, блок управления, регистр обмена. Вход входного регистра соединен с

входом блока управления и является первым входом устройства, первый, второй и третий выходы блока управления подключены соответственно к управляющим входам входного регнстра, регистра обмена и буферного блока памяти, выход которого соединен с первым входом блока сравнения. Выход преобразователя нараллельного кода в последовательный соединен с первым входом регистра обмена, выход которого подключен к -первому входу буферного блока памяти и к второму входу блока сравнения. Второй вход буферного блока памяти соединен с первым выходом

входного регистра, второй выход входного регистра - с третьим входом блока сравнения..;. Недостаток этого устройства состоит в том, что оно не обеспечивает локализации

неисправности с точностью до интегральной схемы, вследствие чего оно имеет невысокую производительность.

Цель изобретения - повышение производительности устройства.

Это достигается введением в устройство регистра тестов, дешифратора, счетчика, переключателя входов, переключателя выходов. Четвертый и пятый выходы блока управления соединены соответственно с управляющими входами счетчика и регистра

тестов, первый, второй, третий, четвертый, пятый и шестой выходы которого связаны соответственно с входом дешифратора, с первым входом преобразователя параллельного кода в -последовательный, с первым входом диагностируемого устройства, с информационным входом переключателя входов, с упра1вляющмм входом лереключателя входов, с четвертым входом блока cpaiBHeHHH. Третий выход входного регистра соединен с .входом регистра тесто-в, выход дешифратора - с управляюш им входом переключателя выходов, информационный вход которого связан с выходом диагностируемого устройства, а выход переключателя .выходов - с вторым входом преобразователя параллельного «ода в последовательный. Выход блока сравнения подключен к входу счетч1ика, выход которого соединен с третьим входом преобразователя параллельного кода в последовательный и с вторым 1ВХОДОМ регистра обмена, а выход переключателя входов - к -второму входу диагностируемого блока.

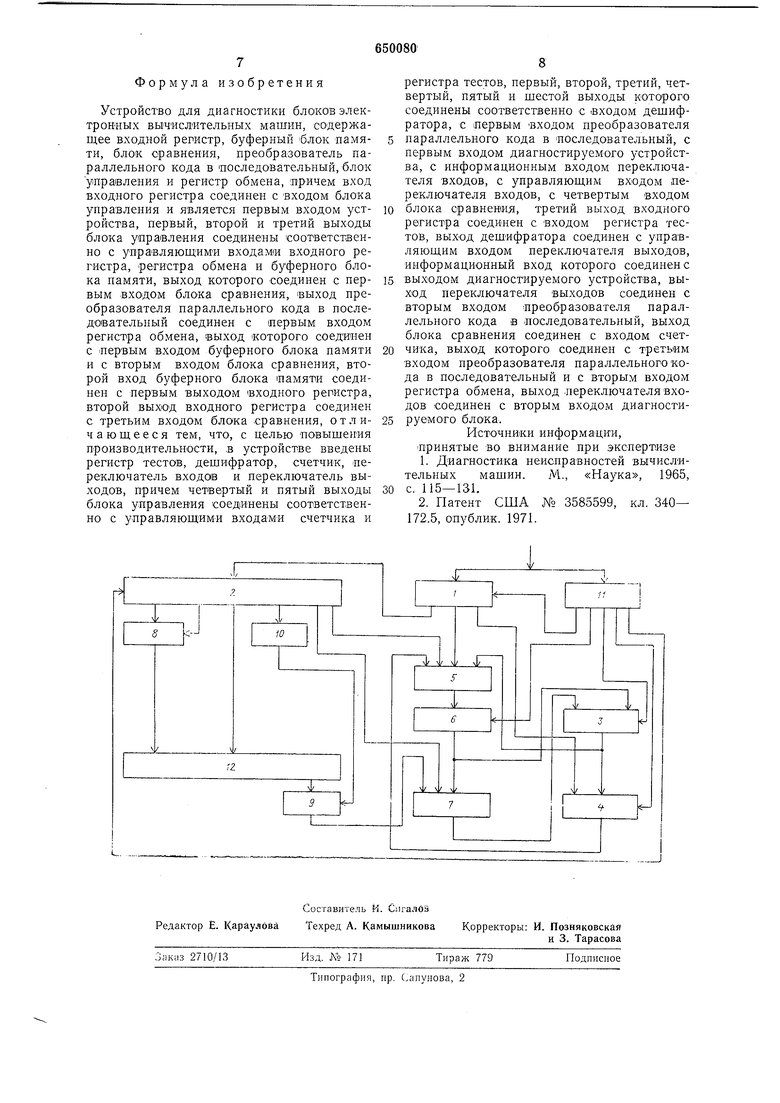

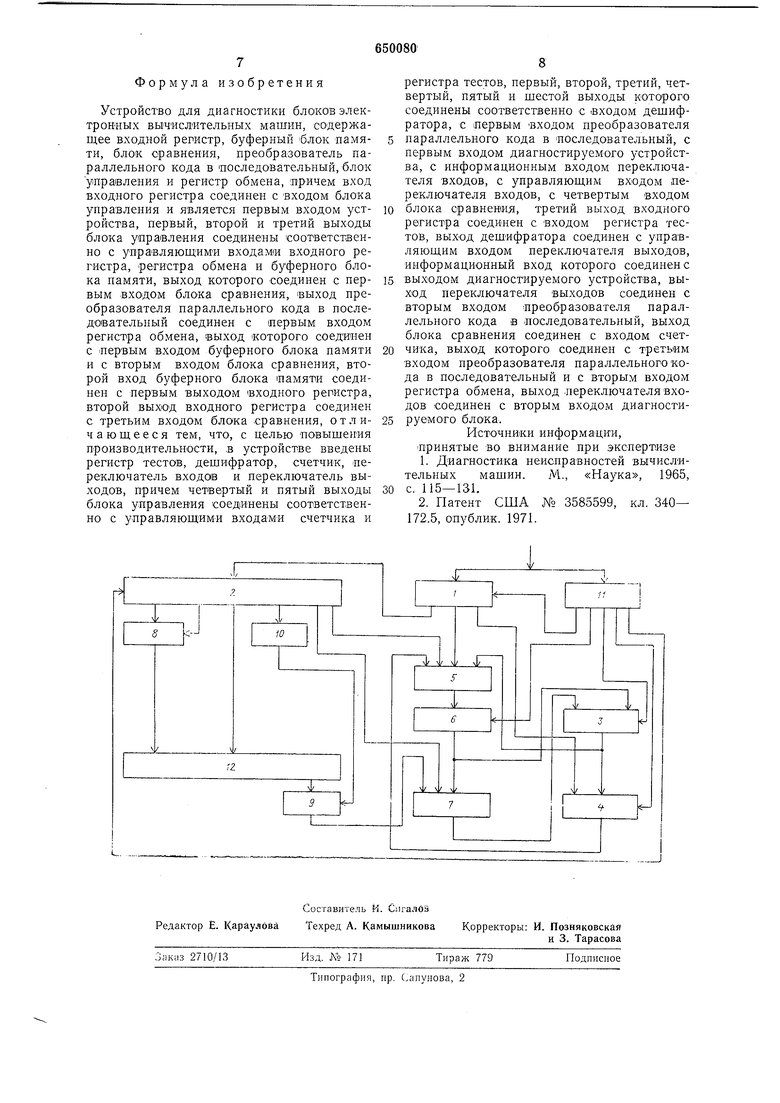

На чертеже .представлена структурная схема предлагаемого устройства для диагностики блоков ЭВМ.

Устройство включает входной регистр 1, регистр 2 тестов, регистр 3 обмена, буферный блок 4 памяти, блок 5 сравнения, счетчик 6, преобразователь 7 параллельного кода в последовательный, переключатель 8 входов, переключатель 9 выходов, дешифратор 10, блок 11 управления.

входы входного регистра Г п блока 11 образуют вход устройства. Первый, второй, третий, четвертый и пятый выходы блока 11 соединены соответственно с управляющими входами входного регистра 1, регистра 3, буферного блока 4, счетчика 6 и регистра 2. Выход преобразователя 7 подключен к первому входу регистра 3, выход которого соединен с первым входом буферного блока 4 и с вторым входом блока 5. Второй вход буферного блока 4 соединен с первым выходом входного регистра 1, второй выход которого связан с третьим входом блока 5, третий выход входного регистра - с Б.ходом регистра 2, первый, второй, третий, четвертый, пятый, шестой выходы которого соединены соответственно с входами дешифратора 10, с первым входом преобразователя 7, с первыми входами диагностируемого блока 12, с информационными и управляюш,им входами переключателя 8, с четвертым входом блока 5. Выходы переключателя 8 подключены к вторым входам диагностируемого блока 12, выходы которого соединены с -информационными входа-ми переключателя 9. Управляюшие входы переключателя 9 соединены с выходами дешифратора 10, а выходы - с вторым входом преобразователя 7. Выход блока 5 связап с входом счетчика 6, выход которого соединен с третьим входом преобразователя 7 и вторым входом регистра 3. Работу устройства можно свести к выполпен-ию следующей последовательности функций: авто.матическая установка регистра тестов для подачи входных последовательностей на проверяемый типо-вой элемснт замены согласно програ.мме контроля; опрос выходов проверяемого типового

элемента замены; сравнение полученных данных с эталоном; накопление результата, полученного на множестве тестов в буферном блоке -памяти; определение неисправных интегральных схем по -справочнику в

соответствии с полученным кодом; переход к следующему циклу диагностики, т. е. подтверждение правильности локализации неисправности путем останова процесса диагностики на первом тесте, . обнаруж-ивающем неисправность, и уточнение локализации с помощью специального индикаторного щупа и справочника эталонных значе}1ий в схеме типового элемента замены. В устройстве имеется специальный разъем, в .который вставляется проверяемый типовой элемент замены. С монтажной стороны к -каждому сигнально-му контакту разъема подведен выход соответствующего разряда регистра 2. (К свободным конта-ктам и контактам питания выходы регистра 2 не подводятся). Разрядность регистра 2 равна К+4, где К. количество сигнальных контактов типового элемента замены, а 4 - количество дополнительных разрядов для управления впутренним-и мультиплексорами в проверяемом типовом элементе замены.

При установке проверяемого типового элемента замены -в разъем устройства на

контактах разъема происходит соединение выходов регистра тестов с контактами проверяемого типового элемента замены. В результате этого на входные конта-кты проверяемого типового элемента поступают

з-начения соответствуюш1их разрядов регистра 2. Выходные контакты проверяемого типового элемента замены образуют с выхода.ми соответствующих им разрядов регистра 2 монтажное И. Поэтому для получения па контактах значения выходов типового элемента замены соответствующие разряды регистра 2 устанавливаются в «1. Вследствие того, что выходы регистра 2 образуют в этих позициях монтажное И

с выходами проверяемого типо-вого элемента за-мены, при опросе выходов регистра тестов в этих позициях будут значения выходов проверяемого типового элемента замены. Благодаря этому в устройстве отсутствует коммутатор, -который в других стендах обеспечивает коммутацию входов и выходов.

Опрос выходов регистра 2 тестов осуществляется с помощью преобразователя 7

параллельного кода в последовательный.

информация с выхода которого поступает в регистр 3 обмена и далее в б.чок 5 сравнения. После установки проверяемого типового элемента замены в разъем устройства и запуска устройства данные с внешнего носителя тестовой информации поступают к входам устройства во входной регистр 1, если информац1ия представляет собой тестовый набор, или в блок 11, если информация - управляющая. Блок 11 обеспечивает заполнение регистра 2 путем приема данных из входного регистра 1. В результате этого в разрядах регистра 2, соответствующих входным контактам проверяемого типового элемента замены, устанавливается входной набор, а в разрядах, соответствующих выходным контактам проверяемого типового элемента замены - «1.

Высокая плотность монтажа в типовом элементе замены современных ЭВМ «приводит к тому, что цена каждого контакта разъема возрастает. В этих случаях трудно выделить свободные контакты для использования их в качестве контрольных точек для индикации и опроса состояния схем. Поэтому с целью сокращения количества контактов, применяемых в качест;ве контрольных точек, в типовом элементе замены устанавливают мультиплексоры, которые преобразуют параллельный код регистров типового элемента замены в последовательный. В этом случае для вывода из типового элемента замены восьмибитного регистра требуется не восемь контактов, а четыре (три контакта для управления входами мультиплексора н один - для его выхода).

Обычно управляющие сигналы и выход мультиплексора подключаются к фиксированным контактам типового элемента замены.

Если типовой элемент замены не содержат мультиплексоров, эти контакты используются для обычных целей.

Посредством переключателя 8 обеспечивается подача на определенные контакты проверяемого типового элемента замены либо сигналов управления мультиплексорами (если таковые имеются в типовом элементе замены), лпбо сигналов с выходов регистра 2 тестов (когда в типовом элементе замепы нет мультиплексоров). Это позволяет «спользовать при проверке внутренние мультиплексоры типового элемента замены для получения доступа к схемам, не имеющим непосредственного выхода на контакты.

Переключатель 8 управляется битом регистра тестов.

Когда в проверяемом типовом элементе замены имеется несколько внутренних мультиплексоров, обеспечивающих вывод информации о состоянии регистра и триггеров типового элемента замены, необходимо коммутировать конкретный мультиплексор на вход преобразователя 7, так как для всех эгих мультиплексоров в буферном блоке 4 (н на индпкацип) выделен один адрес (байт). Подключение проверяемого мультиплексора к преобразователю 7 осуществляется установкой в трех управляющих битах регистра 2 кода, соответствующего проверяе.мому мультиплексору.

Для этой цели служит переключатель 9, который в соответствии с выходом дешифратора 10 выбирает и подключает к преобразователю 7 выход соответствующего мультиплексора.

Для опроса результата и сравнения с эталоном формируется адрес данных. Содержимое входного регистра 1 передается 3 буферный блок 4 для указания адреса данных, которые поступают через регистр

обмена в буферный блок 4. Выбранная для сравнения информация попадает в блок 5, на другой вход которого из регистра 1 подается эталонная информация. Результат сравнения поступает на вход счетчика

6, который может работать в двух режимах: сдвигателя и счетчика.

В режиме сдвпгателя результат сравнения по управляющему сигналу, поступающему из блока 11, сдвигается вправо.

После заполнения счетчика 6 из входного регистра 1 в буферный блок 4 поступает адрес записи содерл имого счетчика 6 и оно записывается в буферный блок 4, как составная часть кода неисправности. Этотпроцесс продолжается до тех пор, пока не закончится формирование полного вектора неисправности. После формирования н записи в буферный блок 4 полного вектора неисправности происходит останов устройства.

По окончан ;и проверки код неисправности считывается из буферного блока 4н по диагностическому справочнику определяются неисправные интегральные схемы.

В другом счетчик 6 работает при проверке результатов автоматической диагностики. Этот режим позволяет остановить процесс диагностики на первом тесте, обнаружившем неисправность, и с помощью щупа подтвердить правильность локализации неисправности.

С этой целью счетчик 6 по сигналу управления 1из блока 11 переводится в режим счетчика и повторным пуском устройства

по сигналам из блока 11 считает количество тестов до останова устройства. Номер теста определяет входной набор и эталонную ннформацию в схеме типового элемента замены, приведенную в справочнике.

Благодаря возможностн быстрой локализаци1И неисправностей внутри типового элемента замены с точностью до интегральной схемы настоящее устройство обеспечивает более высокую производительность при диагностике блоков ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для диагностики двухмашинного вычислительного комплекса | 1980 |

|

SU959086A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

Авторы

Даты

1979-02-28—Публикация

1976-09-20—Подача