(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ и ДИАГНОСТИКИ ЦИФРОВЫХ Изоб эетение относится к вычислительной технике и может быть использовано для обнаружения и локализации неисправностей цифровых узлов. Известно устройство для проверки блоков ЭВМ с ручным и автоматическим управлением Ш, которое не обеспечивает локализации неисправностей с точностью до интегральных схем (ИС). Наиболее близким к предлагаемому по технической сущности является уст ройство, обеспечивающее локализацию неисправностей с точностью до ИС, которое содержит накопитель тестов, входной регистр, регистр тестов,блок преобразователей параллельного кода в последовательнь1й,управляющий блок блок индикации, а также регистр результата, регистр обмена, буферный блок памяти, блок сравнения и переключатели входов и выходов. Причем выход накопителя тестов соединен со входами входного регистра и управляю щего блока, выходы которого соединен с управляющими входами входного регистра, регистра результата, регистра обмена, буферногр блока памяти и регистра тестов. Информация о сос тоянии выходов регистра тестов

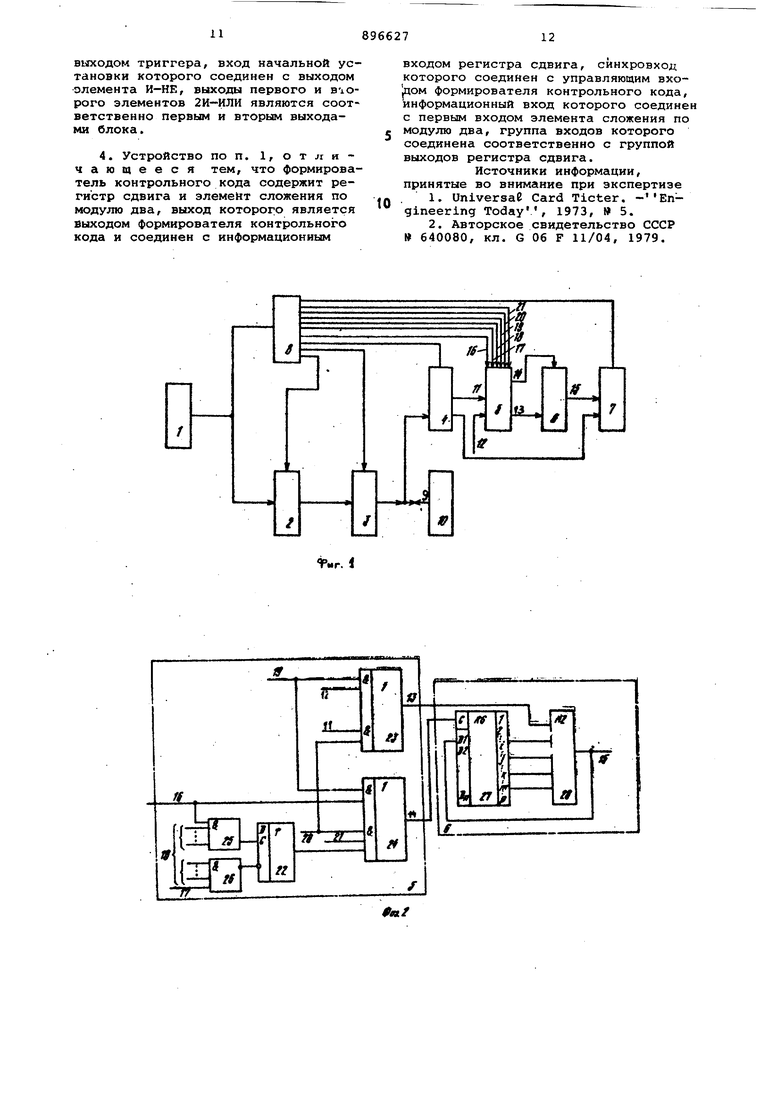

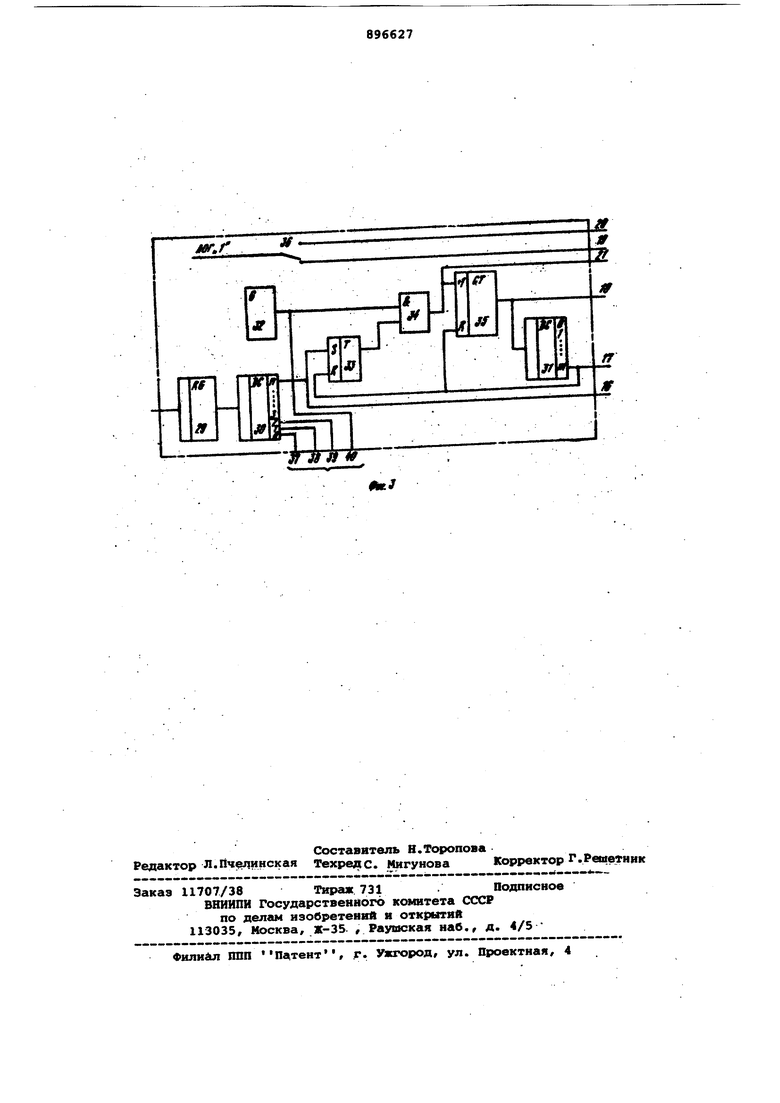

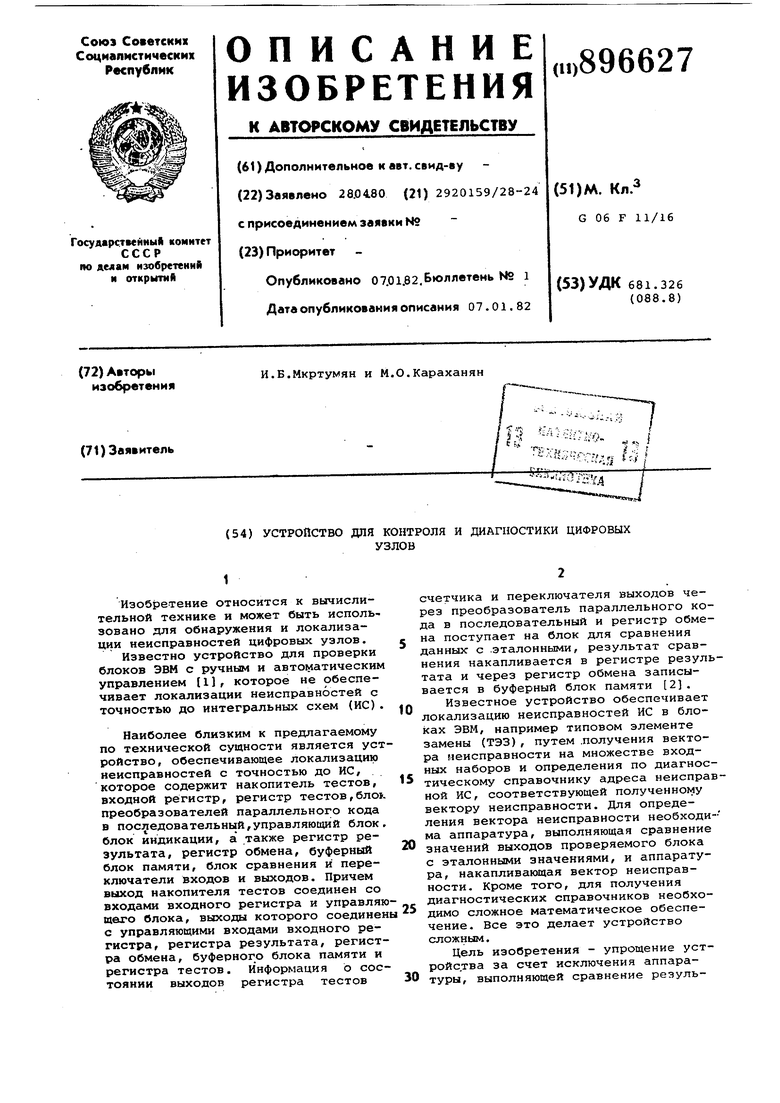

УЗЛОВ счетчика и переключателя выходов через преобразователь параллельного кода в последовательный и регистр обмена поступает на блок для сравнения данных с .эталонными, результат сравнения накапливается в регистре результата и через регистр обмена записывается в буферный блок памяти 2. Известное устройство обеспечивает локализацию неисправностей ИС в блоках ЭВМ, например типовом элементе замены (ТЭЗ), путем .получения вектора В1еисправности на множестве входных наборов и определения по диагностическому справочнику адреса неисправной ИС, соответствующей полученному вектору неисправности. Для определения вектора неисправности необходима аппаратура, выполняющая сравнение значений выходов проверяемого блока с эталонными значениями, и аппаратура, накапливающая вектор неисправности. Кроме того, для получения диагностических справочников необходимо сложное математическое обеспечение. Все это делает устройство сложным. Цель изобретения - упрощение устройства за счет исключения аппаратуры, выполняющей сравнение результата с эталонным и формирующей векто неисправностей, а также диагностичес ких справочников и матобеспечения, необходимого для их получения. Поставленная цель достигается тем что устройство, содержащее накопител тестов, блок управления, входной регистр, регистр тестов, блок преобразования параллельного кода в последов.ательный и блок индикации, первый вход которого соединен с первым выходом блока преобразования параллель ного кода в последовательный, информационные входы которого соединены с выходами контролируемого цифрового узла, входы которого соединены с выходами регистра тестов, информациокные входа которого соединены с выходами входного регистра, информационные входы которого соединены с выходами накопителя тестов и входами блока управления, первый, второй, третий и четвертый выходы которого соединены соответственно с управляющими входами входного регистра, реги стра тестов, блока преобразования параллельного кода в последовательный и блока индикации, содержит блок селекции и формирователь контрольного кода, причем второй вход блока индикации соединен с выходом формирователя контрольного кода, информационный вход которого соединен с первым выходом блока селекции, первый, второй, третий, четвертый, пять и шестой управляющие входы которого соединены соответственно с пятым, шестым, седьмым, восьмым, девятым и десять выходами.блока управления, второй выход блока преобразования параллельного кода в последовательный соединен с первым информационным входом блока селекции, второй информационн9йЕй вход которого является входом устройства, второй выход блока селекции соединен с управляющим входом формирователя контрольного кода. Блок управления содержит два дешифратора, генератор, элемент И, триггер, счетчик и регистр диагности ческих операций, выход которого соединен со входом первого дешифратора, первьй, второй и третий выходы которого являются соответственно первым, вторым и третьим выходс1ми блока, четвертый выход которого соединен с выходом ген.ератора и первым входом элемента И, второй вход которого соединен с в лгодом триггера, вход установки в единицу которого соединен с п-выходом (,2,.,.) первого дешифратора и является пятым выходом блока, выход элемента И сое динен со счетным входом счетчика, вход начальной установки которого соединен со входом установки тригге в ноль и с т-выходом второго дешифратора и является шестьам вы-ходом блока, седьмой выход которого соединен с выходом счетчика и входом дешифратора, восьмой выход блока соединен с первым выходом переключателя, ВТ9Р.ОЙ выход которого является девятым выходом блока, десятый выход которого соединен с выходом элемента И, вход регистра диагностических операций является входом блока. Блок селекции содержит два элемента 2И-ИЛИ, элемент И, элемент ИНЕ и триггер, синхропровод которого соединен с выходом элемента И, первый вход которого соединен с первым входом первого элемента 2И-ИЛИ и является первым управляющим входом блока, второй управляющий вход которюго соединен с первым входом элемента И-НЕ, второй вход которого соединен со вторым входом элемента И и является третьим управляющим входом, блока, четвертый управляющий вход которого соединен со вторым входом первого элемента 2Й-ИЛИ и первым входом второго элемента 2И-ИЛИ, второй и третий входы которого являются соответственно первым и вторым инфорФ ационными входами блока, пятый управлякюдай вход блока соединен с третьим входом первого элемента 2И-ИЛИ и четвертым входом второго элемента 2И-ИЛИ, четвертый вход первого элемента 2И-ИЛИ является шестым управляющим входом блока, пятый вход первого элемента 2И-ИЛИ соединен с выходом триггера, вход начальной установки которого соединен с выходом элемента ИНЕ1Е, выходы первого и второго элементов 2И-ИЛИ являются соответственно первым и вторым выходами блока. Формирователь контрольного кода содержит регистр сдвига и элемент сложения по модулю два, выход которого является выходом формирователя контрольного кода и соединен с информационным входом регистра сдвига, синхровход которого соединен с управляющим входом формирователя контрольного кода, информационный вход которого соединен, с лервым входом элемента сложения до модулю два, группа входов которого соединена соответственно с группой выходов регистра сдвига. На фиг. 1 иэображена структурная схема устройства; на фиг. 2 - принципиальная схема блока .селекции и формирователя контрольного кода; на фиг. 3 - принципиальная схема блока управления. Устройство (фиг. 1) содержит накопитель 1 тестов, входной регистр 2, регистр 3 тестов, Олок 4 преобразования параллельного кода в последовательный, блок 5 селекции, формирователь 6 контрольного кода, блок 7 индикации и блок .8 управления. В состав блока 5 селекции (фиг. 2 входит триггер 22, элементы 2И-ИЛИ 23 и 24, элемент И 25 и элемент И-НЕ 26, Первые входы элементов 2И-ИЛИ 23 и 24 образуют управляющий вход 19 блока 5 селекции, вторые входы вход 20. -Другие два входа элемента 2И-ИЛИ 23 являются информационными входами 11 и 12 блока 5 селекции, третий вход элемента 2И-ИЛИ 24 вместе с первым входом элемента И 25 образуют управляющий вход 16, а четвер тый вход - управляющий вход 21. Пятый вход элемента 2И-ИЛИ 24 соединен с выходом триггера 22, синхронизирую щий вход которого соединен с выходом элемента И 25, вход установки О с выходом элемента .и-НЕ 26, один из входов которого является управляющим входом 17 блока 5 селекции, а вторые входы вместе со вторыми входами элемента И 25 образуют управляющие вход 18 блока 5 селекции. Выходами блока селекции являются выходы 13 и 14 эле ментов 2И-ИЛИ 23 и 24. В состав формирователя 6 входят регистр 27 сдвига и элемент 28 еложения по модулю два. Синхронизирующий вход регистра 27 соединен с упра ляющим входом формирователя 6, который соединен с выходом 14 селектора 5, а информационный вход регистра 27 соединен с выходом элемента 28, который соединен также с выходом 15 формирователя б. Первый вход элемента 28 соединен с информационным входом формирователя 6, который соединен с выходом 13 селектора 5, а остальные входы - с выходами разрядов регистра 27, определяемых порождающим полиномом Р(X). В состав блоха управления входят регистр 29 диагностических операций, дешифраторы 30 и 31, генератор 32 синхроимпульсов, -RS-TpHrrep 33, эле-мент И 34, счетчик 35 и переключател 36 режимов. Выходы регистра 29 соединены со входами дешифратора 30, первые три входа которого соединены соответственно с выходами 37 - 39 блока 8 управления, которые соединены с управляющими входами регистров 2 и 3- и блока 4 соответственно (фиг. Четвертый выход дешифратора 30 соединен с S -входом триггера 33 и выхо дом 1G блока 8 управления, R-входы триггера 33 и счетчика 35 соединены с выходом дешифратора 31 и выходом 1 блока 8 управления, а выход триггера 33 соединен с одним из входов элемента И 34, другой вход которого сое динен с выходом генератора 32 и выходом 40, который соединен с управляющим входом блока 7 (фиг. 1). Выход элемента И 34 соединен с выходом 21 управляющего блока В и счетным входом счетчика 35, выход которого соединен с выходами 18 блока 8 управ ления и входами дешифратора 31. Вход установки счетчика 35 в нулевое состояние соединен с выходом дешифратора 31. На вход переключателя режимов 36 поступает логическая единица, а выходы переключателя соединены с выходами 19 и 20 управляющего блока 8. В устройстве использован принцип сжатия информации о состоянии контактов проверяемого блока на тестовых наборах путем формирования контрольного кода для последовательности двоичных сигналов на выходах проверяемого блока. К-разрядный контрольный код для двоичной последовательности образуется с помощью порождающего полинома Р(Х), степени К. Контрольный код формируется с помощью К-разрядного регистра, имеющего обратные связи, соответствующие виду порождающего полинома. Порождающий полином должен иметь такую степень, чтобы контрольный код, полученный для двоичной последовательности на выходе неисправного блока, всегда отличался от контрольного кода для исправного блока, т.е. сжатие информации не должно приводить к неправильному диагнозу. Предлагаемое устройство функционирует следующим образом. В первом режиме для определения исправности диагностируемого блока вырабатывается контрольный код для двоичной последовательности сигналов, с которым затем сравнивается эталонный код блока. За эталонный контрольный код принимается код, полученный в этом режиме для заведомо исправного блока. Во втором режиме контрольный код вырабатывается для двоичной последовательности сигналов на выходе проверяемой ИС диагностируемого блока. Полученный код сравнивается с эталонным. За эталонные принимаются коды, полученные на выходах ИС заведомо исправного блока в этом режиме. Для удобства работы обслуживающего персонала эталонный код для выхода каждой ИС блока записывается у соответствующего вывода ИС на функциональной схеме блока. Работа по определению эталонных кодов и нанесению их на функциональную схему блоков предшествует передаче ЭВМ в эксплуатацию. После подключения выводов 9 диагностируемого блока 10 к выводам устройства и установки первого режима обеспечивается запуск устройства, тестовые наборы считываемые из накопителя 1, через входной регистр 2 поступает в регистр 3, в результате чего на выводы диагностируемого блока 10 поступает последовательность тестовых наборов. Вследствие наличия двусторонней связи, сигналы с выводов диагностируемого блока 10 через блок 4 последовательно поступают на вход 11 селектора 5, входы 19 и 20 которого (фиг. 2) после установки первого режима переходят в состояние f I р I t JJ I 12 I 1 соответственно, далее сигналы с выхода 13 селектора 5 поступают на первый вход элемента 28. Контрольный код для этой двоичной последовательности сигналов вырабатывается в регистре 27 с обратной связью, определяемой заданным порождающим полиномом. Очередной сигнал двоичной последовательности с выхода 13 селектора 5 суммируется в элементе 28 по модулю два со значениями разрядов регистра 27 и результат с выхода 15 элемента 28 поступает на информацион ный вход регистра 27. В этом режиме сигналы на синхрониризующий вход регистра 27 поступают с выхода 14 лемента 2И-ИЛИ 24, на вход 21 которого они поступают из управляющего блока 8. После установки первого режима выходы 19 и 20 управляющего блока 8 (фиг. 3) устанавливаются в состояние соответствен но, осуществляя запуск устройства. Коды операции, считываемые с накопителя, поступают в регистр 29.диагнос тических операций, в результате чего на выходах 37 - 39 дешифратора 30 в зависимости от программы испытаний появляются сигналы управления входным регистром 2, регистром 3 тестов и блоком 4 преобразования параллельного кода в последовательный. Сигнал операции Конец тестового набора вырабатывается на п-ом выхо де дешифратора 30 и осуществляет ус тановку в единицу триггера запуск блока селекции через вход 16, после чего начинает работать счетчик 35 по счетному входу от импульсов с выхода генератора 32 через элемент И 34,, Состояния счетчика, соответствую щие кодам 00...01+11+111 определяют порядковый номер выводов разъема диагностируемого блока. Из этих сос тояний - первый (код 00...01) соответствует сигналу Готовность к опросу и при появлении его на выходах 18 начинается опрос состояния выводов диагностируемого блока и фо мирование контрольного кода. Процес накопления контрольного кода завершается, когда счетчик 35 переходит в состояние 1111 и на выходе дешифратора 31 возникает сигнал Конец цикла накопления контрольно го кода , который сбрасывает триггер 23 и счетчик 35, переводя управ ляющий блок 8 в состояние ожидания до появления следующего кода операКонец тестового набора на выходе дешифратора 30. Таким образом, в первом режиме тестовые наборы, поступающие на диагностируемый блок 10, формируют контрольный код соответствии с состоянием выводов диагностируемого блока 10. Во втором режиме на выходах 19 и 20 устанавливаются сигналы i и О соответственно. Выход проверяемой ИС диагностируемого блока 10, как было описано выше, соединяется со входом 12 блока селекции. После пуска устройства тестовые наборы, считываемые из накопителя поступают в диагностируемый блок 10. Состояние выхода проверяемой ИС на каждом тестовом наборе поступает на первый вход элемента.28 (фиг. 2) и формирует контрольный код для последовательности сигналов с выхода проверяемой ИС при появлении сигнала Коне.ц тестового набора на входе 16 устройства. Прохождение синхросигналов на вход регистра 27 разрешается единичным состоянием триггера 22, которое устанавливается при поступлении на его синхронизирующий вход сигнала с выхода элемента 25 и сбрасывается при поступлении на его вход установки О сигнала с выхода элемента 26. На входы элементов 25 и 26 из блока 8 поступают сигналы, определяющие порядковый номер вывода разъема диагностируемого блока 10. Сигнал на выходе 14 элемента 2И-ИЛИ 24 появляется при поступлении на вход 16 блока селекции сигнала Конец тестового набора и на входы 18 кода, определяющего номер первого из выводов, т. .е, сигнал на выходе 17 свидетельствует о готовности к опросу состояния выводов диагностируемого блока 10 и к очередному циклу накопления контрольного кода. При поступлении на входы 18 блока 5 селекции кода номера последнего вывода диагностируемого блока 10 и сигнала на вход 17, свидетельствующего об окончании очередного цикла накопления контрольного кода, сигналом на выходе элемента И-НЕ 26 производится сброс триггера 22, в результате которого на выходе 14 блока 5 селекции присутствует О, т. е. содержимое регистра 27 не изменяется. Состояние регистра 27 сдвига по окончании последовательности тестовых наборов является контрольным кодом диагностируемого блока. По окончании проверки полученный контрольный код визуально сравнивается с эталонным контрольным кодом диагности- руемого блока 10, записанным на его функциональной схеме. Несовпадение результатов свидетельствует о неисправности блока. Для локализации неисправной ИС устанавливается второй режим. При его установке из блока 8 управления на входы 19 и 20 блока 5 селекции поступают сигналы i и О соответственно. Выход проверяемой ИС диагностируемого, блока 10 соединяется со входом 12 устройства. После пуска устройства тестовые наборы, считываемые из накопителя 1 через входной регистр 2, поступают в регистр 3, в результате чего на входы диагностируемого блока 10 поступает последовательность тестовых наборов. Состояние выхода ИС на каждом тестовом наборе поступает на первый вхо элемента 28 и суммируется по модулю два со значениями разрядов регист ра 27, где и формируется контрольный код для последовательности сигналов с выхода проверяемой ИС. Синхросигнал приема и сдвига информации на регистре 27 поступает через выход 14 элемента 2И-ИЛИ 24 при появлении в этом режиме сигнала Конец тестового набора на вход 16 блока 5 селек ции. Состояние регистра 2.7 наблюдае мое через блок индикации, определяет контрольный код для проверяемого элемента ИС. Признаком неисправности ИС является совпадение контрольного кода с эталонным на ее входах и несовпадение на выходе. При предлагаемой организации диаг ностики цифровых узлов достигается высокая локализуемость неисправностей до ИС в диагностируемом блоке пр значительном упрощении устройства диагностики и его программных средст Формула изобретения .Устройство для контроля и диагнос тики цифровых узлов, содержащее нако питель тестов, блок управления, вход ной регистр, регистр тестов, блок преобразования параллельного кода в последовательный и блок индикации, первый вход которого соединен с первым выходом блока преобразования параллельного кода. в последовательный, информационные входы которого соединены с выходами контролируемого -цифрового узла, входы которого соедйнен с выходами регистра тестов, информационные входы которого соединены с выходами входного регистра, информационные входы которого соединены с выходами накопителя тестов и входами блока управления, первый, второй, тр тий и четвертый выходы которого соединены соответственно с управляющими входами входного регистра, регистра тестов, блока преобразования параллельного кода в последовательный и блока индикации, отличающеес я тем, что, с целью упрощения устройства, оно содержит блок селекции и формирователь контрольного кода, причем второй Ьход блока индикации соединен с выходом формирователя контрольного кода,информационный вход которого соединен с первым выходом блока селекции,первый,второй,третий, четвертый,пятый и шестой управляющие входы которого соединены соо ветственно с пятым,шестым,седьмым,восьмым,. девятым, десятым выходами блока управления, второй выход блока преобразования параллельного кода в последовательный соединен с первым информационным входом блока селекции, второй информационный вход которого является входо.м устройства, второй выход блока селекции соединен с управляющим входом формирователя контрольного кода. 2.Устройство по п. 1, отличающееся тем, что блок управления содержит два дешифратора, ге(нератор, элемент И, триггер,.. счетчик и регистр диагностических операций, выход которого соединен со входом первого дешифратора, первый,второй и третий выходы которого являются соответственно первым, вторым и третьим выходами блока, четвертый выход которого соединен с . ВЕЛХОДОМ генератора и первым входом элемента И, второй вход которого соединен с выходом триггера, вход установки в единицу которого соединен с п-выходом перво-го дешифратора и является пятым выходом блока, выход элемента К соединен со счетным входом счетчика, вход начальной установки которого соединен со входом установки триггера в ноль и т-выходом второго дешифратора и является шестым выходом блока, седьмой выход которого соединен с выходом счетчика и входом-второго дешифратора, восьмой выход блока соединен с первым выходом переключателя, второй выход которого является девятым выходом блока,десятый выход которого соединен с выходом элемента И, вход регистра диагностических операций является входом блока. 3.Устройство по п. 1, о т л и .чающееся тем, что блок селекции содержит два элемента 2И-ИЛИ, .элемент И, элемент И-НЕ, триггер, синхровход которого соединен с выходом элемента,И, первый вход которого соединен с первым входом первого элемента 2И-ИЛИ и является первым управляющим входом блока,второй управляющий вход которого соединен с первым входом элемента И-НЕ,второй вход которого соединен со вторым входом элемента И и .является третьим управляющим входомблока,четвертый управляющий вход которого соединен со вторым входом первого элемента 2И-ИЛИ и второй и третий входы которого являются соответственно первым и вторым информационными входами блока, пятый управляющий вход блока соединен с третьим входом первого элемента 2И- ИЛИ и четвертым входом второго элемента 2И-ИЛИ, четвертый вход первого элемента 2И-ИЛИ является шестым управляющим входом блока, пятый вход первого элемента 2И-ИЛИ соединен с

выходом триггера, вход начальной установки которого соединен с выходом элемента И-НЕ, выходы первого и вчорого элементов 2И-ИЛИ являются соответственно первым и вторым выходами блока.

4. Устройство по п. 1, отличающееся тем, что формирователь контрольного кода содержит регистр сдвига и элемент сложения по модулю два, выход которого является выходом формирователя контрольного кода и соединен с информационным

входом регистра сдвига, синхровход которого соединен с управляющим вхо|ЦОМ формирователя контрольного кода, информационный вход которого соедине с первым входом элемента сложения по модулю два, группа входов которого соединена соответственно с группой выходов регистра сдвига.

Источники информации, принятые во внимание при экспертизе . 1. Universal Card Ticter. -Engineering Today, 1973, 5.

2. Авторское свидетельство СССР 640080, кл. G 06 F 11/04, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1976 |

|

SU650080A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Устройство для диагностики неисправностей технических объектов | 1987 |

|

SU1515175A2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-28—Подача