Жходы cyNfMaropoB по модупю Р, каждой первой ступени подключены к выходам переносов-взятых попарно Р-ичных сумматоров первой ступени, а входы сумматоров по модулю Р каждой последующей ступени подключены .к выходам взятых попарно сумматоров по модушо Р предыдущей ступени и выходам переносов попарно взятых Р-нчньгх сумматоров той же ступени, входы оконечного сумматора по модупю Р подключеш 1 к выходам сумматора по модулю Р последней ступени и выходам переноса Р-41чного сумматора последней ступени, а выходы совместно с выходами суммы Р-ичного сумматора последней ступени подключены ко входам Р-ичного сумматора с распространением переноса, выходы которого подключены ко входам выходного регистра.

Кроме того, каждый Р-ичный сумматор может содержать К однораэрййных Р-ичных сумматоров, входы которых подключены к соответствующим входам Р-ичного сумматора, а выходы суммы и переноса кажхюго одноразрядного Р-ичного сумматора подключены к соответствующим выходам суммы и переноса сумматора.

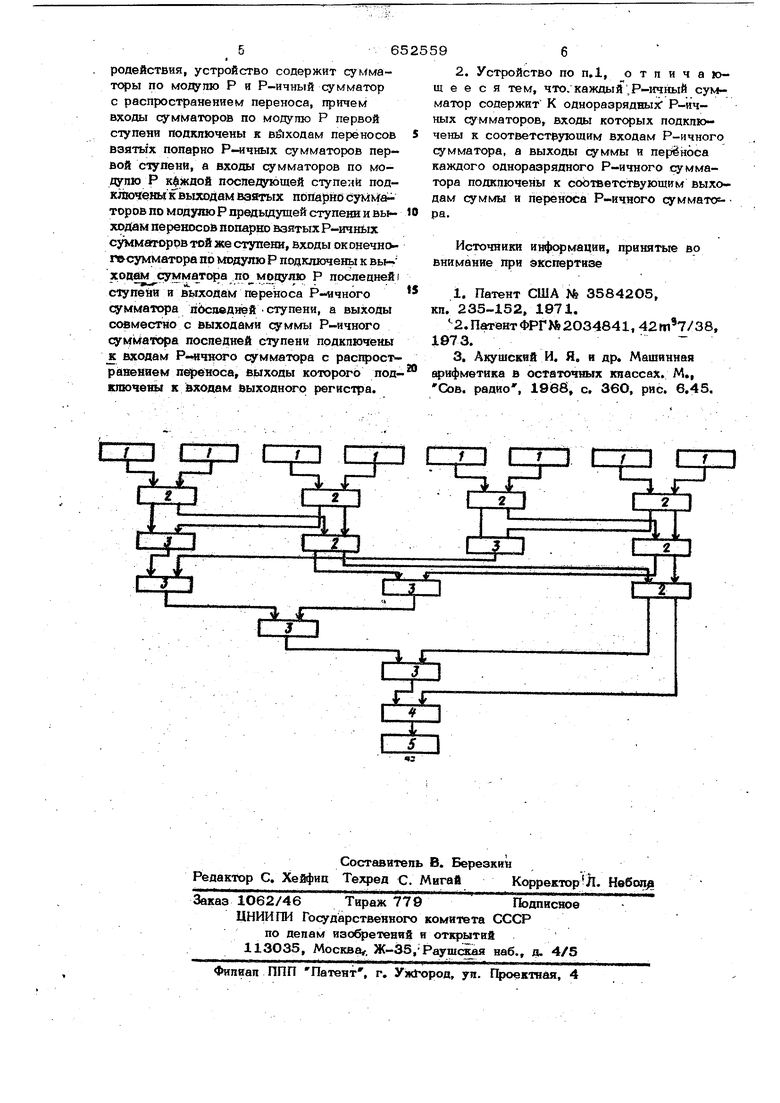

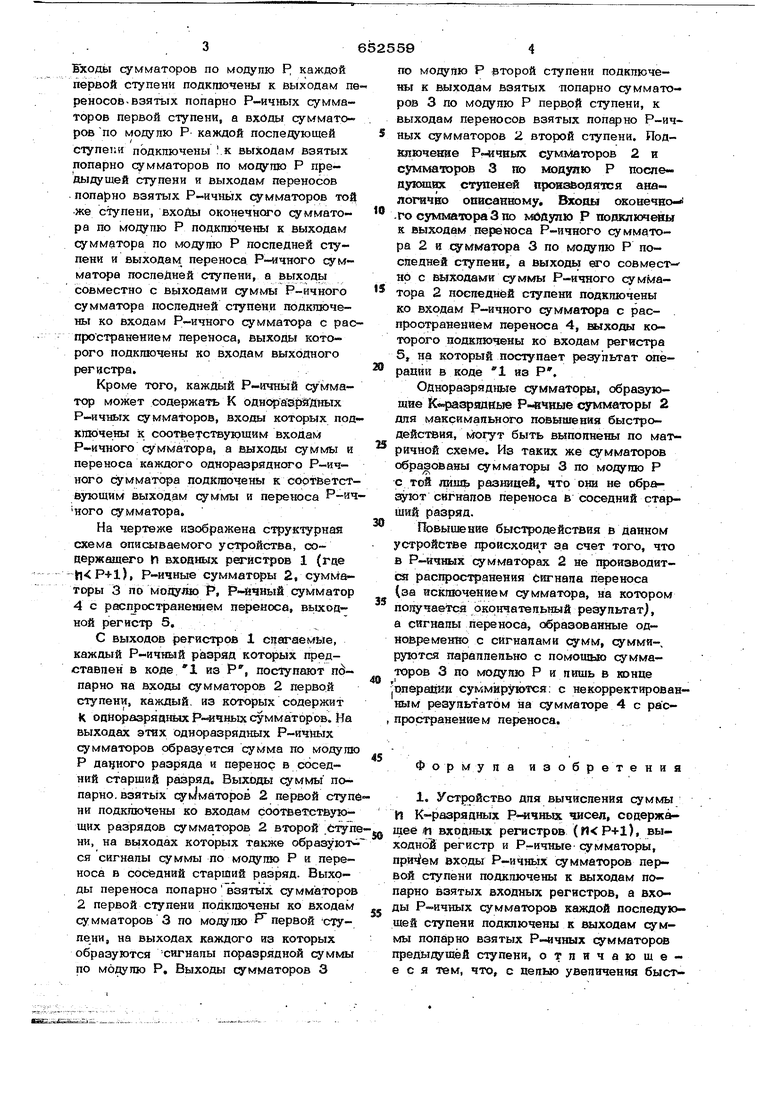

На чертеже изображена структурная схема описываемого устройства, содержащего П вхонш 1х регистров 1 (где И P+l). Р-ичные сумматоры 2, сумматоры 3 по модулю Р, Рнйчиый сумматор 4 с рас11ространением переноса, вьцсоцной регистр 5.

С выходов регистров 1 слагаемые, каждый Р-ичный разряд которых представлен в коде i из Р, поступают п6парно на входы сумматоров 2 первой ступени, каждый, из которых содержит К одноразрядных Р--ЙЧНЫХ сумматоров. На выходах этих одн зазрядных Р-ичных сумматоров образуется сумма по модушо Р данного разряда и перенос в соседний старший разряд. Выходы суммы попарно, взятых сумматоров 2 первой ступи ни подключены ко входам соотеетствующих разрядов сумматоров 2 второй ступни, на выходах которых также образуют ся сигналы су ммы по модулю Р и переноса в соседний старщий разряд. Выходы переноса попарно взятых сумматоров 2 первой ступени подключены ко входам сумматоров 3 по модулю F первой ступени, на выходах каждого из которых образуются сигналы поразрядной суммы по модулю Р. Выходы сумматоров 3

по модулю Р второй ступени подключены к выходам взятых попарно сумматоров 3 по модулю Р первой ступени, к выходам переносов взятых Р-ичных сумматоров 2 второй ступени. Подключение Р«41чных сумматоров 2 и сумматоров 3 по модупю Р поспепукяцих ступеней претворятся ана- логачво описанному. Вховы ОКОЕЮЧЕОХ .го сумматора 3 по мбдулю Р подключевы к выходам переноса Р-ичного сумматора 2 и сумматора 3 по модулю Р последней ступени, а выходы его сов местно с выходами суммы Р-ичного сумМа-

тора 2 последней ступени подключены ко входам Р-ичного сумматора с распространением переноса 4, выходы которого подключены ко входам регистра 5, на который поступает результат операдии в коде 1 из Р.

Одноразрядные сумматоры, образующие К разряДйые Р-ечные сутлматоры 2 для максимального повышения быстродействия, могут быть выполнены по матричной схеме. Из таких же сумматоров образованы сумматоры 3 по модулю Р с той лишь разгагцей, что они не обра гют сигналов переноса в соседний старший разряд.

Повышение быстродайствия в данном устройстве происходит за счет того, что в Р-ичных сумматс ах 2 не производится распространения сигнала переноса (за исключением сумматора, на котором полЕучаеТсй окончате льный результат), а сигналы переноса, образованные одйовременйо с сигналами сумм, суммя-, руются параллельно с помощью сумма- тхэров 3 по мойулю Р и лишь в юнце ipnepeatiHH суммируются, с некорректированным реауяьт атом на сумматоре 4 с распространением переноса.

Ф о Р м у л а и 3 о б Р а т е н и я

1. Усггррйство для вычисления суммы И К-разрядных Р-«чных чисел, соцержащее ti входных регистров (), выходнбй регистр и Р-ичные сумматоры, прич(ем входы Р-ичнызс сумматоров первой ступени подключены к выходам попарно взятых входных регистров, а входы Р-ичных сумматоров каждой последующей ступени подключены к выходам суммы попарно взятых Р-ичных сумматоров предыдущей ступени, отличающее с я тем, что, с целью увеличения быстродействия, устройство содержит cyMNfaторы по модулю Р и Р-ичный сумматор с распространением переноса, причем входы сумматоров по модупю Р первой ступени подключены к вйходам переносов взятьтх попарно Р-ичных сумматоров первой ступени, а входы сумматоров по модупю Р последующей ступени подключены к выходам взятых пбпарнб cyMW торов по модулю Р предыдущей ступени и выходам переносов попарно взятых Р-ичнь1х сумматоров той же ступени, Входы оконечнсьг&сумматора по модулю Р подключень к ходам сумматора подмодулю Р последней ступени и выходам переноса Р-ичного сумматора п6спвдн вйступени, а выходы совместно с выходами суммы Р-ичного сумматчэра последней ступени подключены к входам Р-ичного qyMMaTopa с распрострЕ1Не8яем переноса, выходы которого под кшочены к входам выходното регистра. 2.Устройство по п,1, о т л и ч а ющ е е с я тем, что. каждый Р-ичныЙ сумматор содержит К одноразрядныхГ Р-ичных сумматоров, входы которых подключены к соответствующим входам Р-ичного сумматора, а выходы суммы и переноса каждого одноразрядного Р-ичного сумматора подключены к соответствующим выходам суммы и переноса Р-ичного сумматог- ра. Источники информации, принятые во внимание при экспертизе 1. Патент США № 35842О5, кл. 235-152, 197 i. 2. Патент ФРГ№ 2034841, 42т7/38, 1073. 3.Акушский И. Я, и др. Машинная арифметика в остаточных классах. М., Сов. радио , 1966, с. 36О, рис. 6.45.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Устройство для подсчета числа двоичных единиц | 1980 |

|

SU966700A1 |

| Устройство для умножения | 1981 |

|

SU974370A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

| ОБНАРУЖИТЕЛЬ КОМБИНАЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1996 |

|

RU2096822C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1991 |

|

RU2030792C1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

Авторы

Даты

1979-03-15—Публикация

1976-07-08—Подача