1

Изобретение относится к вычислительной технике и предназначено для применения в десятичных и универсальных арифметдаеских устройствах.

Известно устройство для умножения десятичных чисел, содержащее регистры множимого и множителя, сумматор и блок управления 1 .

Недостаток известного устройства - его низкое быстродействие.

Наиболее близким к предлагаемому является устройство, содержащее блок управления, регистр множимого, регистр множителя, сумматор и регистр переноса, разрддные выходы которого подключены к первым разрядным входам сумматора, вход блока управления подключен к выходу регистра множителя, управляющий од которого подключен к первому выходу блока управления, к первому управляющему входу сумматора и к первому управляю- щему входу регистра переноса, второй управляющий вход которого подключен ко второму выходу блока управления, третий, че твертый, пятый и щестой выходы которого подключены соотвегственно ко второму, третьему, четвертому и пятому управляющим входам сумматора, выходы переноса каждого разряда которого подключены к соответствующим входам регистра переноса 2.

Недостатком известного устройства является большое время, затрачиваемое на сложение десятичных чисел.

Цель изобретения - повышение быстродействия устройства.

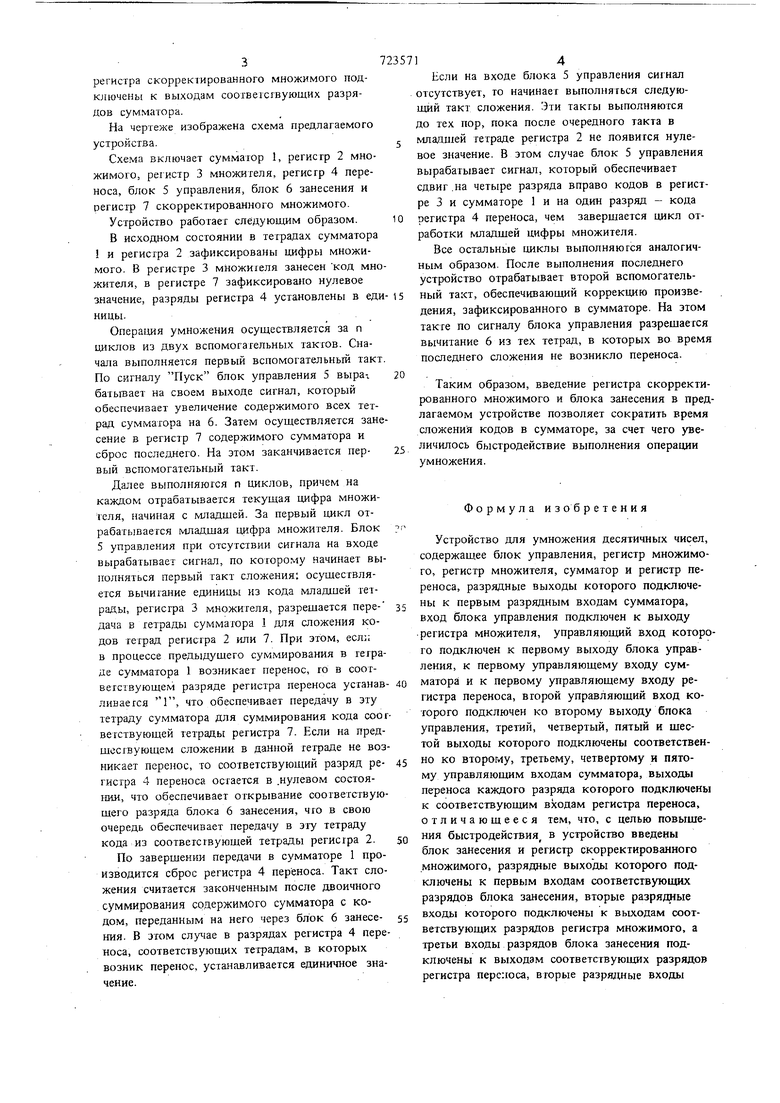

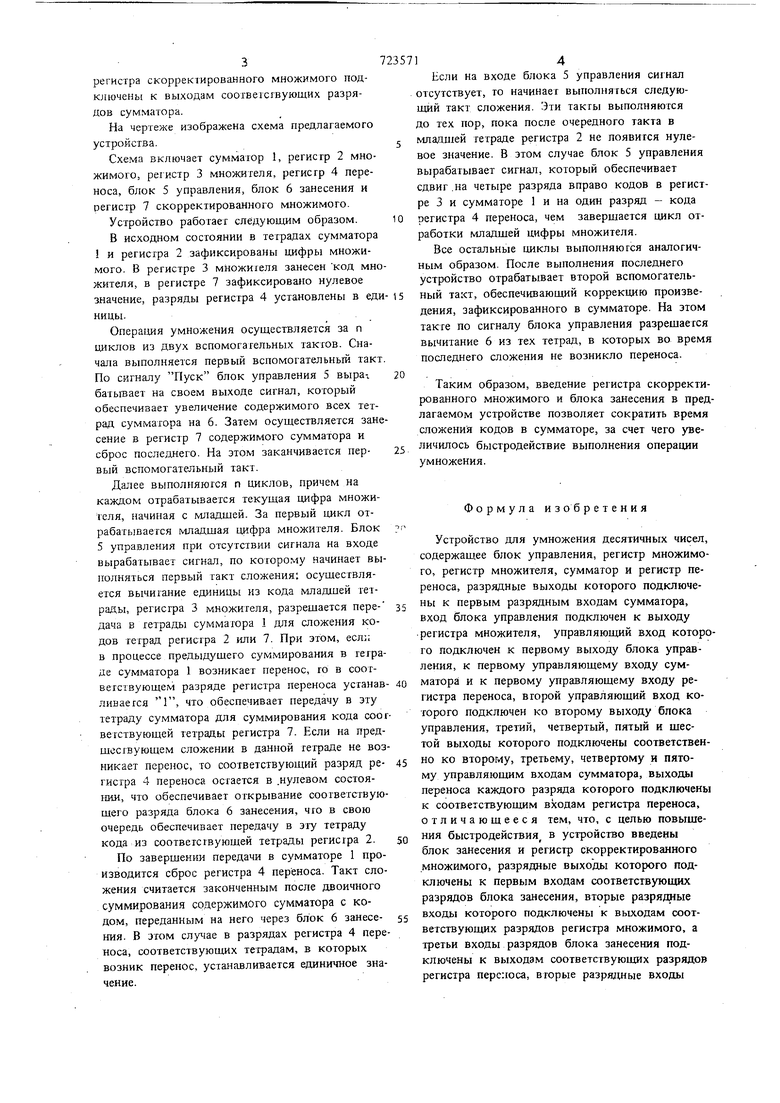

Указанная цель достигается тем, что в устройство введены блок занесения и регистр скорректированного множимого, разрядные выходы которого подключены к первым входам соответствующих разрядов блока занесения, вторые разрядные входы которого подключены к выходам соответствующих разрядов регистра множимого, а третьи входы разрядов блока занесения подключены к выходам соответствующих разрядов регистра переноса, вторые разрядные входы сумматора подключены к выходам соотаетствующих разрядов блока занесения, управляющий вход которого подключен к шестому выходу блока управления и ко входу регистра множителя, разрядные входы регистра скоррекгированного множимого подключены к выходам соотвегсгвующих разрядов сумматора. На чертеже изображена схема предлагаемого устройства. Схема включает сумматор 1, регистр 2 мнО жимого, регистр 3 множителя, регисгр 4 переноса, блок 5 управления, блок 6 занесения и регистр 7 скорректированного множимого. Устройство работает следующим образом. В исходном состоянии в тетрадах сумматора и регистра 2 зафиксированы цифры множимого. В регистре 3 множителя занесен код мно жителя, в регистре 7 зафиксировано нулевое значение, разряды регистра 4 установлены в еди ницы. Операция умножения осуществляется за п циклов из двух вспомогательных тактов. Сначала выполняется первый вспомогательньш такт По сигналу Пуск блок управления 5 выра-. батьгеает на своем выходе сигнал, который обеспечивает увеличение содержимого всех тетрад сумматора на 6. Затем осуществляется зане сение в регистр 7 содержимого сумматора и сброс последнего. На этом заканчивается первый вспомогательный такт. Далее выполняются п циклов, причем на каждом отрабатывается текущая цифра множителя, начиная с младшей. За первый цикл отрабатывается младщая цифра множителя. Блок 5 управления при отсутствии сигнала на входе вырабатывает сигнал, по которому начинает вы полняться первый такт сложения: осуществляется вычитание единицы из кода младшей тетрады, регистра 3 множителя, разрешается передача в тетрады сумматора 1 для сложения кодов тетрад регистра 2 или 7. При этом, есл;; в процессе предыдущего суммирования в тетра де сумматора 1 возникает перенос, то в соответствующем разряде регистра переноса устанав ливаегея 1, что обеспечивает передачу в эту тетраду сумматора для суммирования кода соо ветствующей тетрады регистра 7. Если на предшествующем сложении в данной тетраде не воз никает перенос, то соответствующий разряд регистра 4 переноса остается в .нулевом состоянии, что обеспечивает открывание соответствую щего разряда блока 6 занесения, что в свою очередь обеспечивает передачу в эту тетраду кода из соответствующей тетрады регистра 2. По завершении передачи в сумматоре 1 производится сброс регистра 4 переноса. Такт сложения считается законченным после двоичного суммирования содержимого сумматора с кодом, переданным на него через блок 6 занесения. В этом сл)чае в разрядах регистра 4 пере носа, соответствующих тефадам, в которых возник перенос, устанавливается единичное значение. 14 Если на входе блока 5 управления сигнал отсутствует, то начинает вытюлняться следующий такт сложения. Эти такты выполняются до тех пор, пока после очередного такта в младшей тетраде регистра 2 не появится нулевое значение. В этом случае блок 5 управления вырабатывает сигнал, который обеспечивает сдвиг.на четыре разряда вправо кодов в регистре 3 и сумматоре 1 и на один разряд - кода регистра 4 переноса, чем завершается цикл отработки младщей цифры множителя. Все остальные циклы выполняются аналогичным образом. После выполнения последнего устройство отрабатывает второй вспомогательный такт, обеспечивающий коррекцию произведения, зафиксированного в сумматоре. На этом такте по сигналу блока управления разрешается вычитание 6 из тех тетрад, в которых во время последнего сложения не возникло переноса. Таким образом, введение регистра скорректированного множимого и блока занесения в предлагаемом устройстве позволяет сократить время сложения кодов в сумматоре, за счет чего увеличилось быстродействие выполнения операции умножения. Формула изобретения Устройство для умножения десятичных чисел, содержащее блок управления, регистр множимого, регистр множителя, сумматор и регистр переноса, разрядные выходы которого подключены к первым разрядным входам сумматора, вход блока управления подключен к выходу регистра множителя, управляютций вход которого подключен к первому выходу блока управления, к первому управляющему входу сумматора и к первому управляющему входу регистра переноса, второй управляющий вход которого подключен ко второму выходу блока управления, третий, четвертый, пятый и шестой выходы которого подключены соответственно ко второму, третьему, четвертому и пятому управляющим входам сумматора, выходы переноса каждого разряда которого подключены к соответствуютцим входам регистра переноса, отличающееся тем, что, с целью повышения быстродействия, в устройство введены блок занесения и регистр скорректированного множимого, разрядные выходы которого подключены к первым входам соответствующих разрядов блока занесения, вторые разрядаые входы которого подключены к выходам соответствующих разрядов регистра множимого, а третьи входы разрядов блока занесения подключены к выходам соответствующих разрядов регистра переноса, вторые разря;шые входы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

Авторы

Даты

1980-03-25—Публикация

1975-06-13—Подача