1

Изобретение относится к области интегральных запоминающих устройств (ЗУ).

Известны симметричные элементы памяти на биполярных транзисторах. Основой схем такого рода являются симметричные биполярные триггеры с непосредственными связями. Однако эти схемы содержат большое число компонентов и рассеивают достаточно большую мош,ность.

Известна также ячейка памяти на тиристорном триггере, содержащая два тиристора, транзистор и резистор.

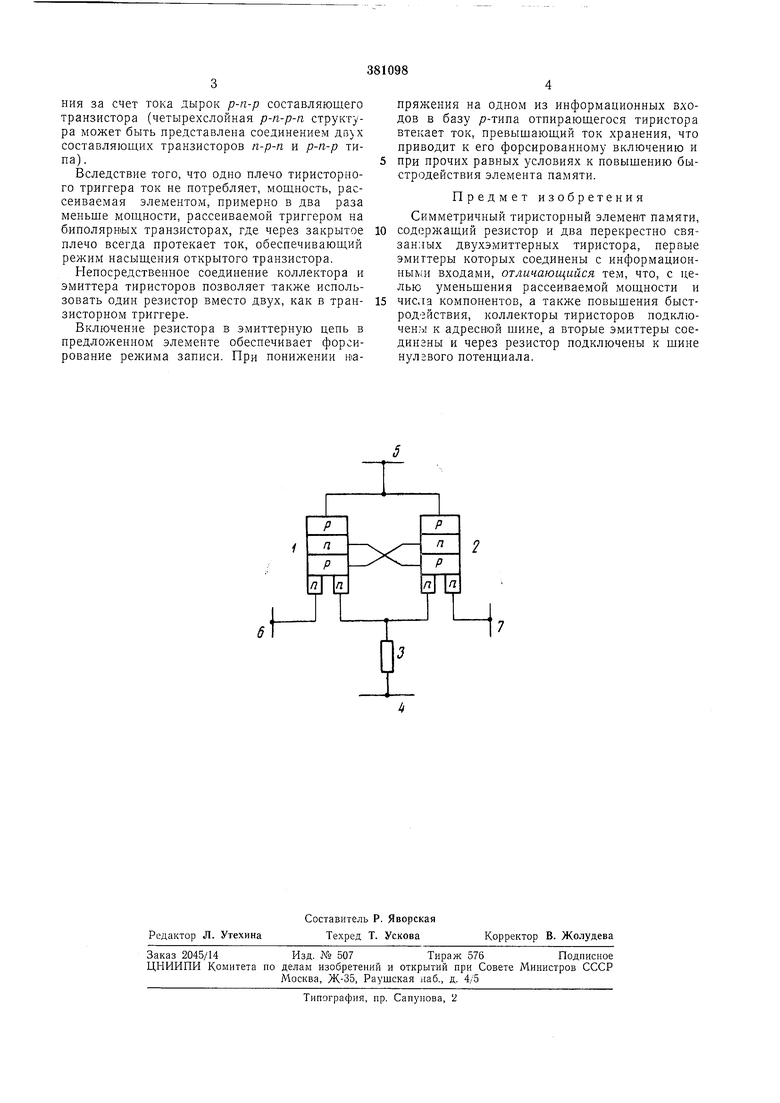

Предлагаемый симметричный тиристорный элемент памяти имеет три компонента и потребляет мощность в два раза меньшую (при прочих равных условиях), чем симметричный триггер на биполярных транзисторах. Это достигается тем, что в нем использованы два перекрестно-связанных двухэмиттерных тирисгора, коллекторы которых непосредственно подключены к адресной шине, вторые (по топологии - внутренние) эмиттеры соединены между собой и через резистор подключены к общей точке, а первые (по топологии - внешние) эмиттеры использованы как информационные входы.

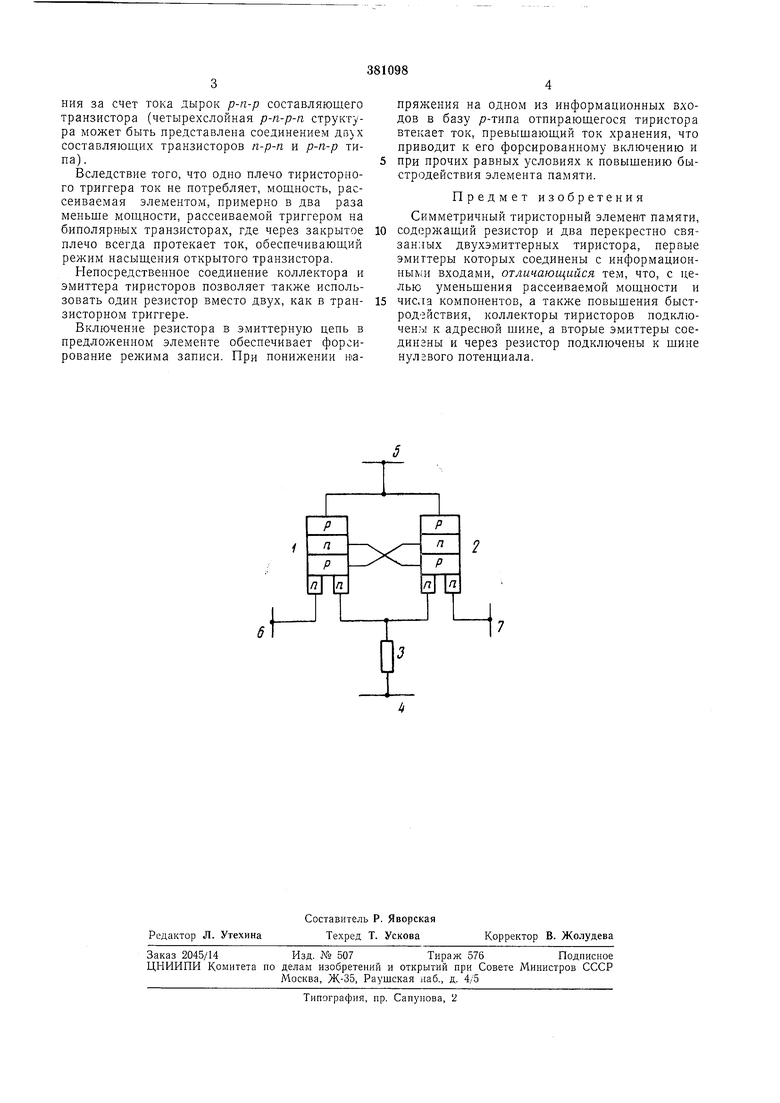

На чертеже показана схема симметричного тиристорного элемента памяти.

Предлагаемый элемент состоит из двух перекрестно гнязанных двухэмиттерных четырехслойных р-п-р-п структур-тиристоров У и 2, вторые эмиттеры которых соединены между собой и через резистор 3 подключены к общей точке 4. Коллекторные области тиристоров ртипа присоединены к адресной шине 5, первые эмиттерные области п-типа - к информационным входам записи и считывания 6 и 7.

В режиме хранения на входах 5 и 7 находится высокий потенциал, и ток хранения протекает через резистор 3. При записи на вход 6 или на вход 7 (в зависимости от вида записываемой информации («О или «1) подается низкий уровень. Считываемый сигнал снимается с одного из информационных входов при

подаче положительного импульса опроса по адресной шине 5.

Таким образом, предлагаемый элемеет при записи и считывании информации работает аналогично обычному симметричному транзисторному триггеру. Отличие состоит в том, что коллекторы и вторые эмиттеры тиристоров непосредственно соединены собой. При таком включении тиристор может оставаться во включенном состоянии и при нулевом управляющем токе, что обеспечивает устойчивую работу тирпсторного триггера. Несмотря на то, что ток через закрытый тиристор не течет, так как напряжение на открытом тиристоре составляет 0,8 в, п-р-п транзистор включенного тиристора находится в режиме н асыщения за счет тока дырок р-п-р составляющего транзистора (четырехслойная р-п-р-п структура может быть представлена соединением двух составляющих транзисторов п-р-п и р-п-р типа).

Вследствие того, что одно плечо тиристорного триггера ток не потребляет, мощность, рассеиваемая элементом, примерно в два раза меньще мощности, рассеиваемой триггером на биполярных транзисторах, где через закрытое плечо всегда протекает ток, обеспечивающий режим насыщения открытого транзистора.

Непосредственное соединение коллектора и эмиттера тиристоров позволяет также использовать один резистор вместо двух, как в транзисторном триггере.

Включение резистора в эмиттерную цепь в предложенном элементе обеспечивает форсирование записи. При понижении напряжения на одном из информационных входов в базу р-типа отпирающегося тиристора втекает ток, превыщающий ток хранения, что приводит к его форсированному включению и при прочих равных условиях к повыщению быстродействия элемента памяти.

Предмет изобретения

Симметричный тиристорный элемент памяти, содержащий резистор и два перекрестно связанлых двухэмиттерных тиристора, первые эмиттеры которых соединены с информационныыи входами, отличающийся тем, что, с целью уменьщения рассеиваемой мощности и числа компонентов, а также повыщения быстродействия, коллекторы тиристоров подключены к адресной шине, а вторые эмиттеры соедингны и через резистор подключены к щине нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩАЯ ЯЧЕЙКАПя^ЙгЙ']- J-.j^L-') •• :: '"?;БИSJiиov!;:^г/^^ i | 1973 |

|

SU378955A1 |

| Симметричный тиросторный элемент памяти | 1976 |

|

SU652613A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Запоминающий элемент | 1977 |

|

SU733022A1 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| Устройство для выборки элементов памяти в накопителе | 1980 |

|

SU930385A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Матричный накопитель | 1984 |

|

SU1403096A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

Авторы

Даты

1973-01-01—Публикация