дополнительного транзистора р-п-р типа - с базой второго дополнительного транзистора п-р--п типами с э iиттepoм четвертого транзистора п-р-п типа, .,3iv}nTTep первого дополнительного транзистора п-р-п типа - с коллектором второго дополнительного транзистора р-п-р типа и С базой первого транзистора п-р-п типа, эмиттер второго дополнительного транзистора я-р-п типа - с коллектором первого дололнительпого транзистора р-п-р типа и с базой второго транзистора п-р-п типа. Базы первого и второго дополнительных транзисторов р-п-р типа и коллекторы первого п второго дополнительных транзисторов п-р-п типа подключены к базам первого и второго транзисторов р-л-р типа.

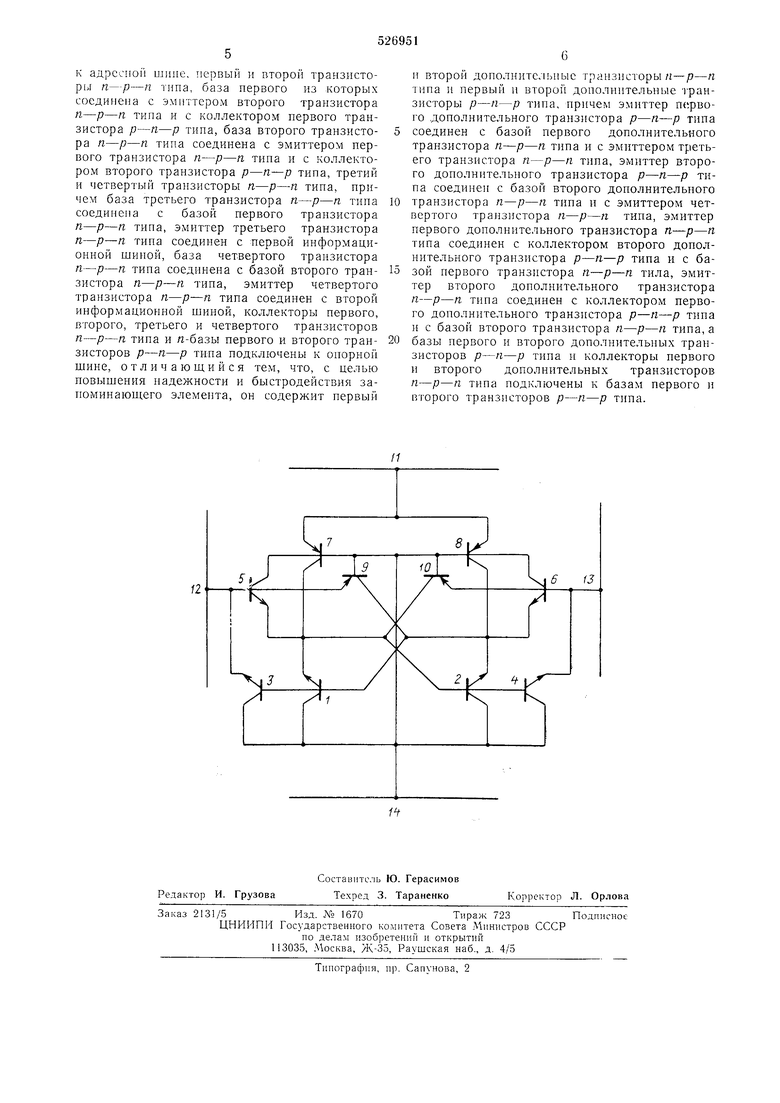

На чертеже представлена принципиальная электрическая схема предлагаемого ипжекционного запоминаюн его элемента.

Запоминающий элемент состоит нз транзисторов п-р-п типа 1-6 и р-п-р 7-10. Все транзисторы имеют общую «-область н могут быть выполнены в одной изолнрованHoii области полупроводника п-типа.

Эмиттеры р-п-;0-трапзисторов 7 и 8 соединены с адресной щиной 11, коллекторы - соответственно с базами транзисторов 2 н 1 и с эмиттерами транзисторов I и 2, базы транзисторов 3 и 4 - соответственно с базами транзисторов 1 и 2, а эмиттеры их - с информационными щинами 12 и 13. Транзисторы 3 и 4 могут рассматриваться совместно с транзисторами 1 и 2 как многоэмиттерные транзисторы. Базы дополнительных п-р-п транзисторов 5 и 6 соединены с информационными щниами соответственно 12 и 13, а эмиттеры их - соответственно с базами транзисторов 2 и 1. Эмиттеры дополнительных р-п-р транзисторов 9 и 10 подключены к базам транзисторов 5 и 6, а коллекторы нх - соответственно к базам транзисторов 1 и 2.

Общая rt-область всех транзисторов соединена с онорной шиной 14.

Предлагаемый запоминающий элемент работает следующим образом.

В режиме хранения информации ток из адресной шины 11 через эмиттеры транзисторов 7 и 8 попадает в опорную щину 14. Коллекторный ток транзисторов 7 и 8 является базовым током соответственно транзисторов 2 и 1. Благодаря наличию перекрестных связей между транзисторами 1 и 2 и при условии, что инверсный коэффициент усиления этих транзисторов больше 1, в открытом состоянии может находиться только один из них, например транзистор 1, в то время как база транзистора 2 шунтирована низким conpoTHBvTCHHем насыщенного транзистора 1, работающего в инверсном режиме.

Так как базы транзисторов 3 и 4 соединены соответственно с базами транзисторов 1 и 2, то транзистор 3 также включен, а транзистор 4 выключен.

При считывании информации на адресной

Н1ине 11 повышается потенциал и через запоминаюи1ий элемент претакет ток, в несколько раз превыщаюии1Й ток режима хранения. Так как транзистор 3 находится в открытом состояНИИ, то повышенный потенциал адресной шины 11 передается через него в информационную шину 12. Как только потенциал шины 12 превысит порог срабатывания подключенного к этой н)ине усилителя считывания (на

чертеже не но:казан), произойдет считывание. Для записи информации на адресной шнне 11 необходимо понизить потенциал п одновременно увеличить ток через запоминающий элемепт. На одной из информационных шин

12 и 13 в зависимости от записываемой информации, например на шине 13, повышается потенциал до уровня, превышаюп1,его потепциал адресной шины 11 па 2 терт.

При этом ток течет из информационной

щины 13 через базу транзистора 6 и эмиттер транзистора 10 в опорную шину 14. Этот ток в несколько раз превышает ток, протекающий из адресной шины 11 в опорную шину 14. Протекание тока через транзистор 6 вызывает

включение его (транзистор 6 работает в инверсном режиме). Коллекторным током транзистора 6 является коллекторный ток транзистора 8, который поддерживал во включенном состоянии транзистор 1. Величина его

существенно меньще базового тока транзистора 6. В результате этого транзистор 6 входит в насыщение и щунтирует базу транзистора 1, вызывая его выключение, а вместе с ним и выключение транзистора 3.

Одновременно коллекторный ток транзистора 10, попадая в базу транзистора 2, включает его и вместе с ним транзистор 4. Транзистор 2 входит в насыщение и щунтирует базу транзистора 1. Таким образом, носле окончания импульса записи запоминающий элемент оказывается переключенным в другое состояние.

Для возвраш.ения запоминающего элемента в прежнее состояние необходимо повысить

уровень напряжения на шине 12. Транзисторы 5 и 9 работают аналогично транзисторам 6 и 10, шунтируя базы транзисторов 2 и 4 и задавая ток в базы транзисторов 1 и 3, в результате чего по описанному способу запоминающий элемент возвращается в прежнее состояние.

Экспериментальное исследование инжекционного запоминающего элемента в интегральном исполнении было проведено на изготовленных в лабораторных условиях образцах. При протекании тока величиной - 1 ма время считывания составило 10 нсек, время записи - 80 нсек.

Формула изобретения

Инжекционпый запоминающий элемент, содержащий первый и второй транзисторы 65 р-п-р типа, эмиттеры которых подключены

к адресной шине, первый и второй транзисторы п-р-п типа, база первого из которых соединена с эмиттером второго транзистора п-р-п тина и с коллектором первого транзистора р-п-р типа, база второго транзистора я-р-п типа соединена с эмиттером первого транзистора п-р-я тина и с коллектором второго транзистора р-я-р типа, третий н четвертый транзисторы п-р-я типа, причем база третьего транзистора я-р-я типа соединена с базой первого транзистора я-р-я тина, эмиттер третьего транзистора п-р-я тина соединен с первой информационной шиной, база четвертого транзистора я-р-п типа соединена с базой второго транзистора я-р-я типа, эмиттер четвертого транзистора я-р-я типа соединен с второй информационной шиной, коллекторы первого, второго, третьего и четвертого транзисторов я-р-я типа и я-базы первого и второго транзисторов р-я-р тцпа подключены к опорной шине, отличаюш,ийся тем, что, с целью повышения надежности н быстродействия запоминающего элемента, он содержит первый

и второй дополните.1ьные транзисторы/г-р-я типа и первый и второй дополнительные транзисторы р-п-р типа, причем эмиттер п(фвого дополнительного транзистора р-я-р типа соединен с базой первого дополнительного транзистора я-р-я типа и с эмиттером третьего транзистора я-р-я типа, эмиттер второго дополнительного транзистора р-я-р типа соединен с базой второго дополнительного транзистора я-р-п типа и с эмиттером четвертого транзистора я-р-я типа, эмиттер первого дополнительного транзистора я-р-п типа соединен с коллектором второго дополнительного транзистора р-п-р типа и с базой первого транзистора я-р-я тила, эмиттер второго дополнительного транзистора я-р-я типа соединен с коллектором первого дополнительного транзистора р-я-р типа и с базой второго транзистора я-р-я типа,а базы первого и второго дополнительных транзисторов р-п-р типа и коллекторы первого и второго дополнительных транзисторов я-р-я типа подключены к базам первого и второго транзисторов р-я-р типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Запоминающий элемент | 1975 |

|

SU570921A1 |

| Запоминающий элемент | 1977 |

|

SU733022A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Элемент памяти | 1975 |

|

SU525160A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

Авторы

Даты

1976-08-30—Публикация

1974-12-31—Подача