Предлагаемое изобретение относится к области вычислительной техники, а именно, к запоминающим устройствам.

Наличие большого количества запоминающих элементов приводит к уменьшению надежности оперативного запоминающего устройства. Поэтому одной из основных проблем при создании запоминающих устройств большой емкости является проблема увеличения их надежности.

В настоящее время известны оперативные запоминающие устройства, в которых резервирование запоминающих элементов памяти оперативного запо.минающего устройства производится с помощью постоянного запоминающего устройства, которое позволяет исправлять неисправные запоминающие элементы, или с помощью ассоциативного запоминающего устройства, которое производит переадресацию неисправных чисел оперативного запоминающего устройства 1.

Из известных оперативных запоминающих устройств наиболее близким по технической сущности к предлагаемому является запоминающее устройство, содержащее первый регистр адреса, вход которого соединен с входом ассоциативного блока памяти, а

ВЫХОД - с первым входом блока коммутации второй вход которого соединен с выходом ассоциативного блока памяти, выход блока коммутации подключен к входу дешифратора адреса, соединенного с накопителем 2.

Недостатком такого оперативного запоминающего устройства является избыточность оборудования, связанная с тем, что в информационной части ассоциативного запоминающего устройства необходимо хранить весь код адреса каждого резервного слова накопителя, а отсюда и. пониженная надежность работы оперативного запоминающего устройства.

Целью предполагаемого изобретения является повыщение надежности устройства.

Поставленная цель достигается тем, что устройство содержит второй регистр адреса и элемент ИЛИ, входы которого соединены с выходами ассоциативного блока памяти, выход соединен с третьим входом блока коммутации, входы младщих разрядов второго регистра адреса соединены с выходами младших разрядов первого регистра адреса, входы старших разрядов соединены с выходом блока коммутации, а выход - с входом дешифратора адреса.

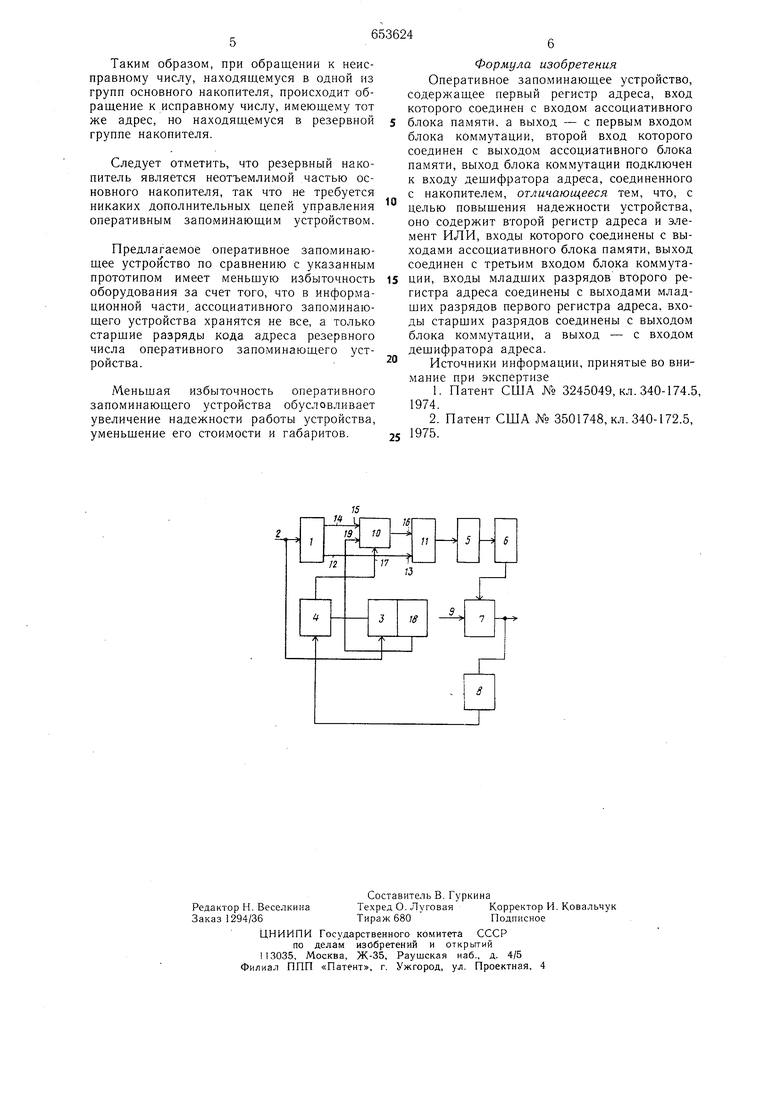

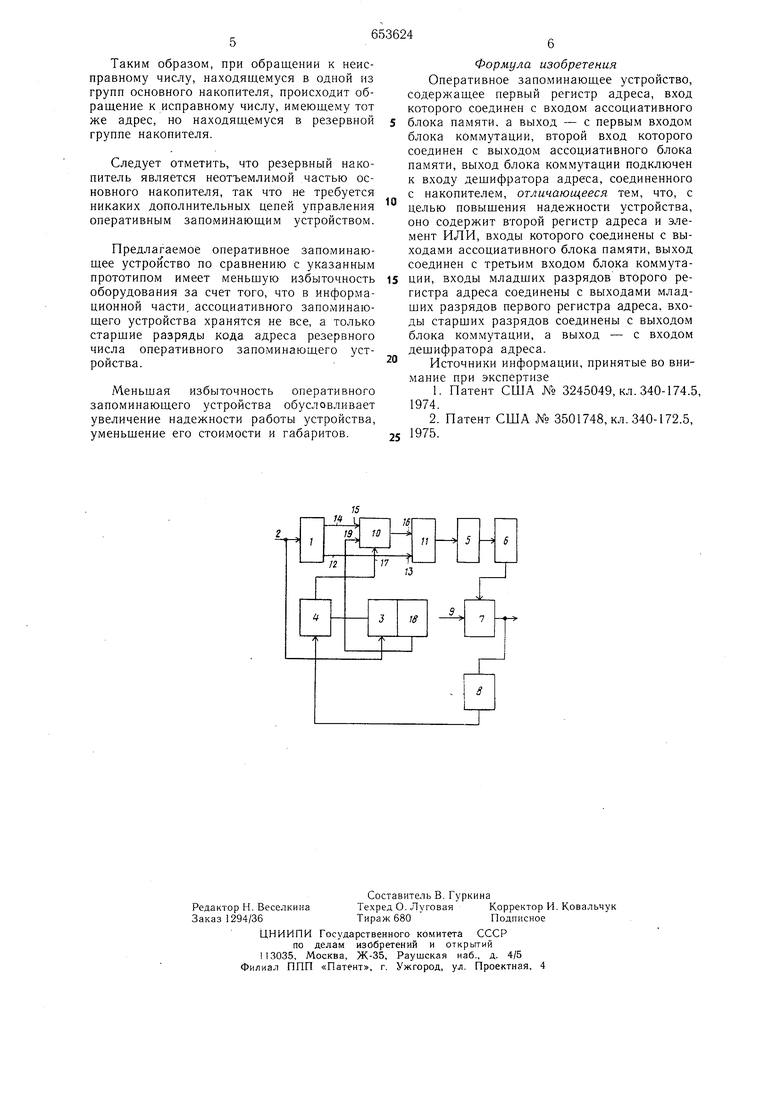

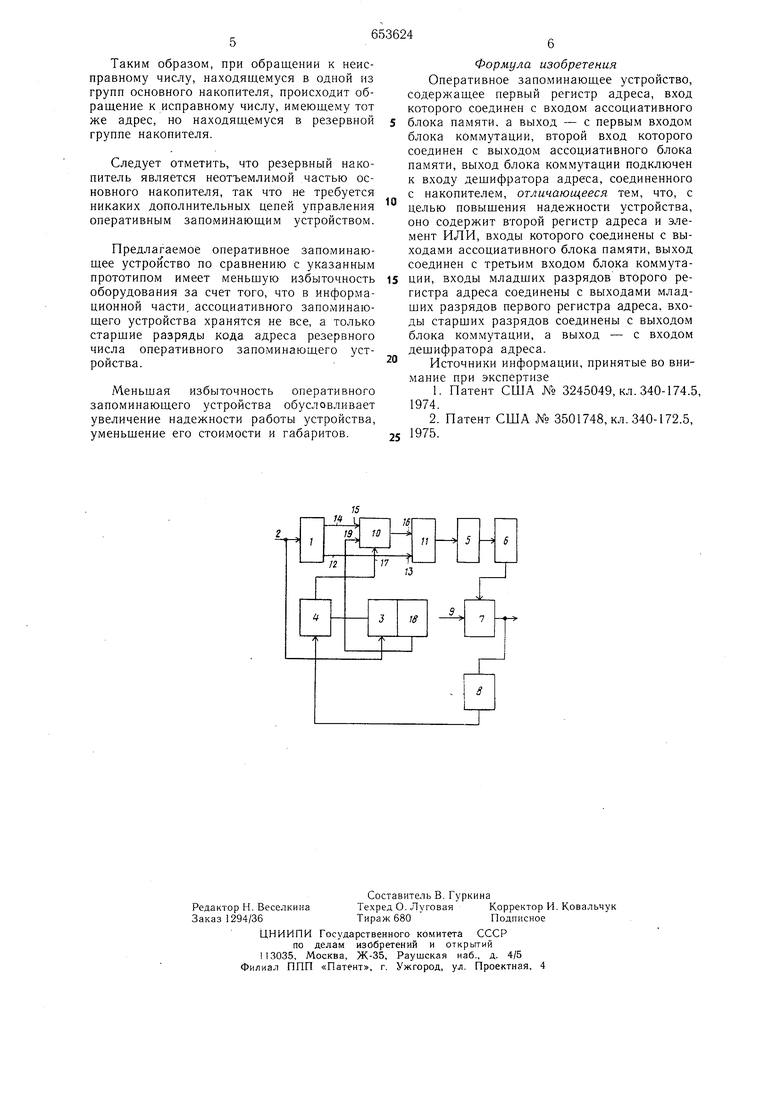

На чертеже представлена блок-схема оперативного запоминающего устройства.

Оперативное запоминающее устройство содержит первый регистр адреса 1, адресный вход 2 которого соединен со входом признаковой части 3 ассоциативного блока памяти, выход которого соединен с устройством управления 4. Выходы дещифратора адреса 5 связаны, со входами блока 6, состоящего из основного и резервного накопителя, выходы которого соединены с блоком разрядных цепей 7, который связан со схемой контроля 8, соединенной с устройством управления 4. На информационный вход 9 блока разрядных цепей 7 подается код числа записываемый в оперативное запоминающее устройство, кро.ме того, оно содержит блок коммутации 10 и второй регистр адреса 11. Выходы младших разрядов 12 первого регистра адреса 1 соединены со входами младщих разрядов 13 второго регистра адреса 1 1, а выходы старших разрядов 14 первого регистра адреса 1 соединены со входами 15 блока коммутации 10. Выходы блока коммутации 10 связаны со входами старших разрядов 16 второго регистра адреса И. Кроме того, управляющий вход 17 блока коммутации 10 соединен с устройством управления 4, а информационная часть ассоциативного блока памяти 18 соединена со входами 19 блока коммутации 10.

Устройство работает следующим образом Числа оперативного запоминающего устройства блока 6, состоящего из ocHOBHctro и резервного накопителей, разбиваются условно на группы с одинаковым количеством чисел в каждой группе. Старщие разряды кода адреса, подаваемого на первый регистр адреса 1 образуют номер группы, а младшие разряды - номер числа в группе. Таким образом, адреса чисел оперативного за 10минающего устройства повторяются в каждой группе. Часть групп образует основной накопитель, а другая часть - резервный накопитель оперативного запоминающего устройства. В информационной части 18 ассоциативного блока памяти записаны коды адресов резервных групп, т. е. только старшие разряды кода адреса числа.

В режиме «за-пись или «считывание код адреса запрашиваемого числа оперативного запоминающего устройства подается на адресный вход 2 первого регистра адреса 1 и на вход признаковой части 3 ассоциативного блока памяти. Код адреса с выхода второго регистра адреса 11 подается на дещифратор адреса 5, который выбирает требуемое число в блоке 6. При этом в режиме «запись информация поступает на информационный вход 9 и через блок разрядных цепей 7 записывается в выбранное дещифратором число блока 6, а в режиме «считывание, если схема контроля 8 не обнаружила ошибку, из выбранного числа основного накопителя блока 6 инфор.мация считывается через блок разрядных цепей 7.

5В том случае, когда при считывании информации из основного накопителя блока 6 схема контроля 8 обнаружила ошибку, она выдает сигнал на устройство управления 4, которое в свою очередь выдает сигнал на запись кода адреса неисправного числа с адресного входа 2 в признаковую часть 3 ассоциативного блока памяти (признаковая часть 3 ассоциативного блока памяти заполняется неисправными адресами последовательно). Таким образом запоминается

5 код адреса неисправного числа основного накопителя блока 6.

В дальнейшем при обращении по какомулибо адресу к оперативному запоминающему устройству код адреса подается одновременно во все слова признаковой части 3 ассоциативного блока памяти. Если ни один из кодов адреса, хранящихся в признаковой части ассоциативного запоминающего устройства не совпал с пришедши.м кодом адреса, что означает, что обращение произо5 щло к исправному числу оперативного запо.минающего устройства, то устройство управления 4 выдает сигнал на управляющий вход 17 блока коммутации 10 и старшие разряды кода адреса запраиливаемого числа с выхода 14 попадают на вход 15, проходят

0 через блок коммутации 10 и записываются во второй регистр адреса 11. Кроме того, младшие разряды кода адреса запрашиваемого числа тоже перезаписываются по входу 13 во второй регистр адреса П. Таким образом, при обращении к исправному числу код адреса этого числа не из.меняется и дешифратор адреса 5 выбирает это число в основном накопителе блока 6. Если же в одном из чисел признаковой части 3 ассоциативного блока памяти хранящийся и пришедший код адреса совпали, что означает, что обращение произошло к неисправному числу основного накопителя блока 6, то из числа информационной части 18 ассоциативного блока памяти, соответствующего числу его признаковой части 3, в которо.м произощ ло совпадение кодов, производится считывание кода адреса резервной группы. При этом устройство управления выдает сигнал на управляющий вход 17 блока коммутации 10 и со входа 19 код адреса резервной группы

0 проходит через блок коммутации и записывается через входы старших разрядов 16 во второй регистр адреса П.

Младшие разряды кода адреса запрашиваемого числа без изменения перезаписываются из первого регистра адреса 1 во второй регистр адреса 11. С выхода второго регистра адреса 11 измененный код адреса подается на дешифратор адреса 5, который выбирает число из резервного накопителя блока 6

Таким образом, при обращении к неисправному числу, находящемуся в одной из групп основного накопителя, происходит обращение к исправному числу, имеющему тот же адрес, но находящемуся в резервной группе накопителя.

Следует отметить, что резервный накопитель является неотъемлимой частью основного накопителя, так что не требуется никаких дополнительных цепей управления оперативным запоминающим устройством.

Предлагаемое оперативное запоминающее устройство по сравнению с указанным прототипом имеет меньщую избыточность оборудования за счет того, что в информационной части, ассоциативного запоминающего устройства хранятся не все, а только старщие разряды кода адреса резервного числа оперативного запоминающего устройства.

Меньшая избыточность оперативного запоминающего устройства обусловливает увеличение надежности работы устройства, уменьщение его стоимости и габаритов.

Формула изобретения

Оперативное запоминающее устройство, содержащее первый регистр адреса, вход которого соединен с входом ассоциативного блока памяти, а выход - с первым входом блока коммутации, второй вход которого соединен с выходом ассоциативного блока памяти, выход блока коммутации подключен к входу дещифратора адреса, соединенного с накопителем, отличающееся тем, что, с целью повыщения надежности устройства, оно содержит второй регистр адреса и элемент ИЛИ, входы которого соединены с выходами ассоциативного блока памяти, выход соединен с третьим входом блока коммутации, входы младших разрядов второго регистра адреса соединены с выходами младщих разрядов первого регистра адреса, входы старщих разрядов соединены с выходом блока коммутации, а выход - с входом дещифратора адреса.

Источники информации, принятые во вни.мание при экспертизе

1. Патент США № 3245049, кл. 340-174.5 1974.

2. Патент США № 3501748, кл. 340-172.5, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

Авторы

Даты

1979-03-25—Публикация

1975-07-11—Подача