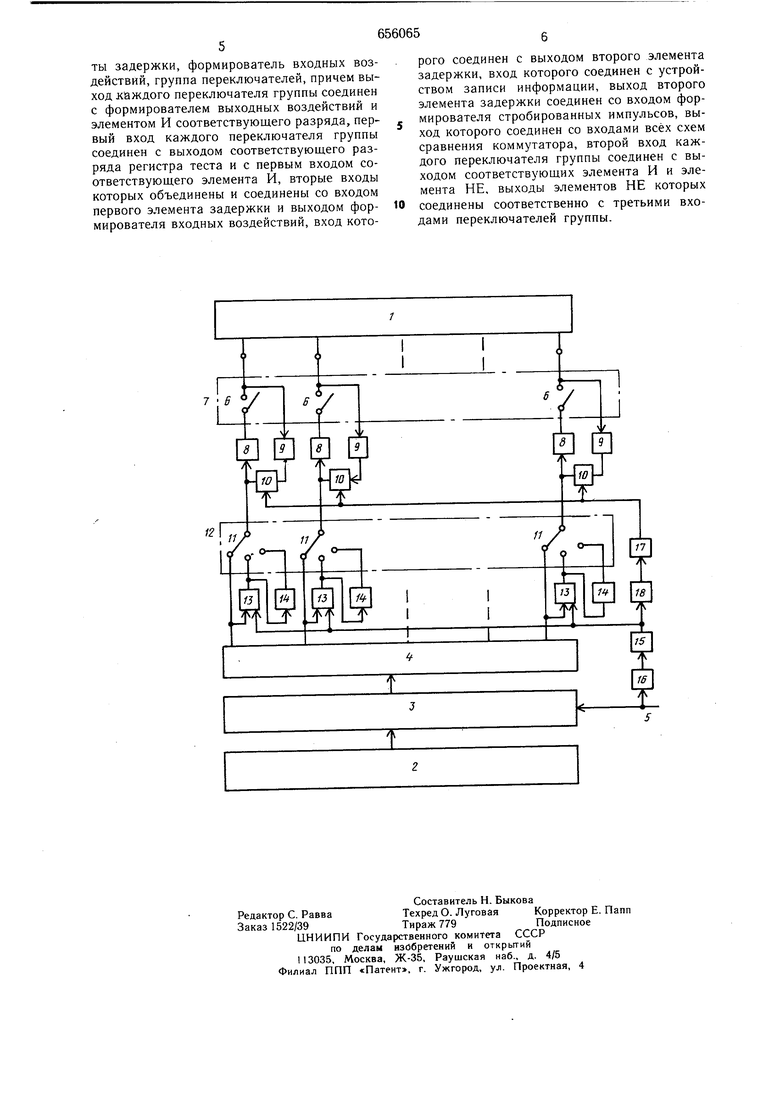

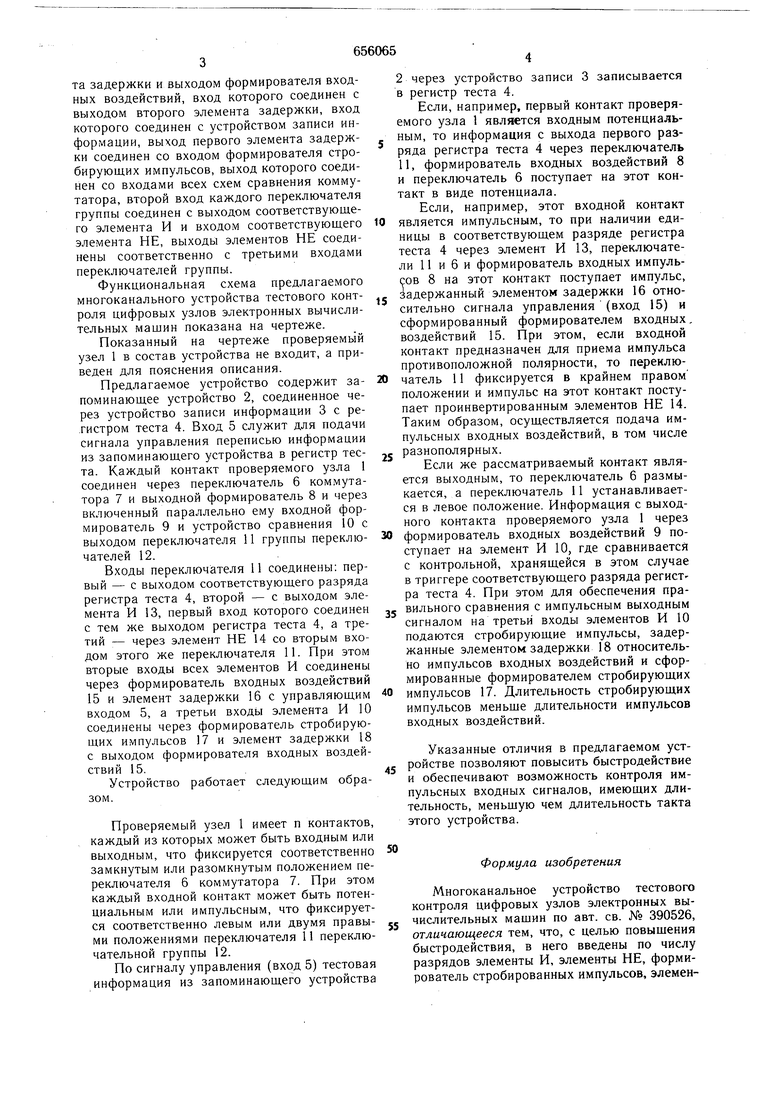

та задержки и выходом формирователя входных воздействий, вход которого соединен с выходом второго элемента задержки, вход которого соединен с устройством записи информации, выход первого элемента задержки соединен со входом формирователя стробирующих импульсов, выход которого соединен со входами всех схем сравнения коммутатора, второй вход каждого переключателя группы соединен с выходом соответствующего элемента И и входом соответствующего элемента НЕ, выходы элементов НЕ соединены соответственно с третьими входами переключателей группы. Функциональная схема предлагаемого многоканального устройства тестового контроля цифровых узлов электронных вычислительных мащин показана на чертеже. Показанный на чертеже проверяемь й узел 1 в состав устройства не входит, а приведен для пояснения описания. Предлагаемое устройство содержит запоминающее устройство 2, соединенное через устройство записи информации 3 с регистром теста 4. Вход 5 служит для подачи сигнала управления переписью информации из запоминающего устройства в регистр теста. Каждый контакт проверяемого узла 1 соединен через переключатель 6 коммутатора 7 и выходной формирователь 8 и через включенный параллельно ему входной формирователь 9 и устройство сравнения 10 с выходом переключателя 11 груцпы переключателей 12. Входы переключателя И соединены; первый - с выходом соответствующего разряда регистра теста 4, второй - с выходом элемента И 13, первый вход которого соединен с тем же выходом регистра теста 4, а третий - через элемент НЕ 14 со вторым входом этого же переключателя 11. При этом вторые входы всех элементов И соединены через формирователь входных воздействий 15 и элемент задержки 16 с управляющим входом 5, а третьи входы элемента И 10 соединены через формирователь стробирующих импульсов 17 и элемент задержки 18 с выходом формирователя входных воздействий 15. Устройство работает следующим образом. Проверяемый узел 1 имеет п контактов, каждый из которых может быть входным или выходным, что фиксируется соответственно замкнутым или разомкнутым положением переключателя 6 коммутатора 7. При этом каждый входной контакт может быть потенциальным или импульсным, что фиксируется соответственно левым или двумя правыми положениями переключателя 11 переключательной группы 12. По сигналу управления (вход 5) тестовая информация из запоминающего устройства 2 через устройство записи 3 записывается в регистр теста 4. Если, например, первый контакт проверяемого узла 1 является входным потенциальным, то информация с выхода первого разряда регистра теста 4 через переключатель 11, формирователь входных воздействий 8 и переключатель 6 поступает на этот контакт в виде потенциала. Если, например, этот входной контакт является импульсным, то при наличии единицы в соответствующем разряде регистра теста 4 через элемент И 13, переключатели 11 и 6 и формирователь входных импульсов 8 на этот контакт поступает импульс, задержанный элементом задержки 16 относительно сигнала управления (вход 15) и сформированный формирователем входных, воздействий 15. При этом, если входной контакт предназначен для приема импульса противоположной полярности, то переключатель 11 фиксируется в крайнем правом положении и импульс на этот контакт поступает проинвертированным элементов НЕ 14. Таким образом, осуществляется подача импульсных входных воздействий, в том числе разнополярных. Если же рассматриваемый контакт является выходным, то переключатель 6 размыкается, а переключатель 11 устанавливается в левое положение. Информация с выходного контакта проверяемого узла 1 через формирователь входных воздействий 9 поступает на элемент И 10, где сравнивается с контрольной, хранящейся в этом случае в триггере соответствующего разряда регист ра теста 4. При этом для обеспечения правильного сравнения с импульсным выходным сигналом на третьи входы элементов И 10 подаются стробирующие импульсы, задержанные элементом задержки 18 относительно импульсов входных воздействий и сформированные формирователем стробирующих импульсов 17. Длительность стробирующих импульсов меньще длительности импульсов входных воздействий. Указанные отличия в предлагаемом устройстве позволяют повысить быстродействие и обеспечивают возможность контроля импульсных входных сигналов, имеющих длительность, меньщую чем длительность такта этого устройства. Формула изобретения Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин по авт. св. № 390526, отличающееся тем, что, с целью повыщения быстродействия, в него введены по числу разрядов элементы И, элементы НЕ, формирователь стробированных импульсов, элементы задержки, формирователь входных воздействий, группа переключателей, причем выход каждого переключателя группы соединен с формирователем выходных воздействий и элементом И соответствующего разряда, первый вход каждого переключателя группы соединен с выходом соответствующего разряда регистра теста и с первым входом соответствующего элемента И, вторые входы которых объединены и соединены со входом первого элемента задержки и выходом формирователя входных воздействий, вход которого соединен с выходом второго элемента задержки, вход которого соединен с устройством записи информации, выход второго элемента задержки соединен со входом формирователя стробированных импульсов, выход которого соединен со входами всех схем сравнения коммутатора, второй вход каждого переключателя группы соединен с выходом соответствующих элемента И и элемента НЕ, выходы элементов НЕ которых соединены соответственно с третьими входами переключателей группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1980 |

|

SU888127A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1012265A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1179346A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Авторы

Даты

1979-04-05—Публикация

1977-04-06—Подача