входов подключены выходы значений младших разрядов произведений блоков 2 умножения (на фиг.З эти выходы блоков 2 показаны справа), а ко второй группе подключены вьгходы значений старших разрядов произведений. Входы младших разрядов второй группы сумматора 3 соединены с выходами блока 5 преобразования. В зависи-

, 130064

Изобретение относится к вычислительной технике и может быть применено для быстрого преобразования двоично-десятичного кода в двоичный и обратно, особенно целесообразно его с использование в процессорах, располагающих средствами быстрого умножения двоичных и десятичных чисел.

Цель изобретения - расширение класса решаемых задач за счет возможное- 10 мости от значения сигнала на входе ти обратного преобразования.настройки сумматора 3 он осуществляет либо десятичное, либо двоичное суммирование.

Коммутатор 4 предназначен для 5 подачи на входы второй группы блоков 2 умножения значения одной из констант. В режиме преобразования двоичло -десятичного кода в двоичный на выходы коммутатора 4 с входа 8 20 первой константы устройства поступает значение двоичного кода величины 10 , где Р 2,3,4,... - число одновременно обрабатываемых десятичных цифр исходного операнда. В резаписи устройства, выход 12 устрой- жиме же преобразования двоичного ства..кода в двоично-десятичный на входы

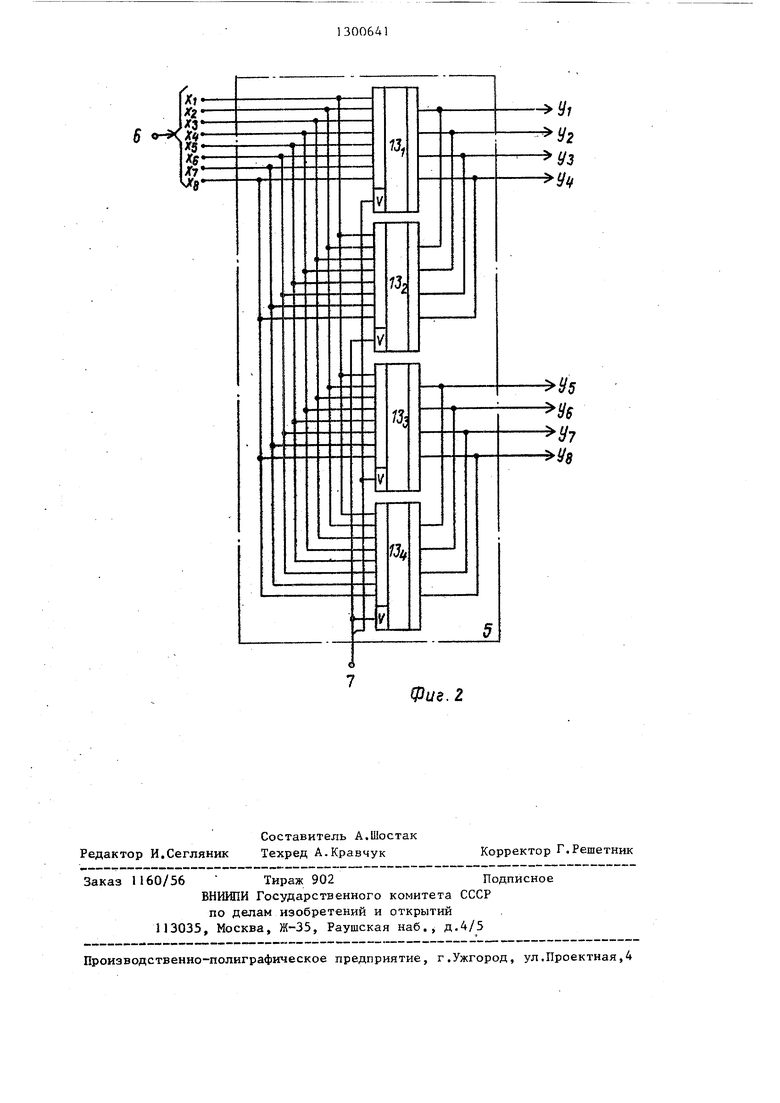

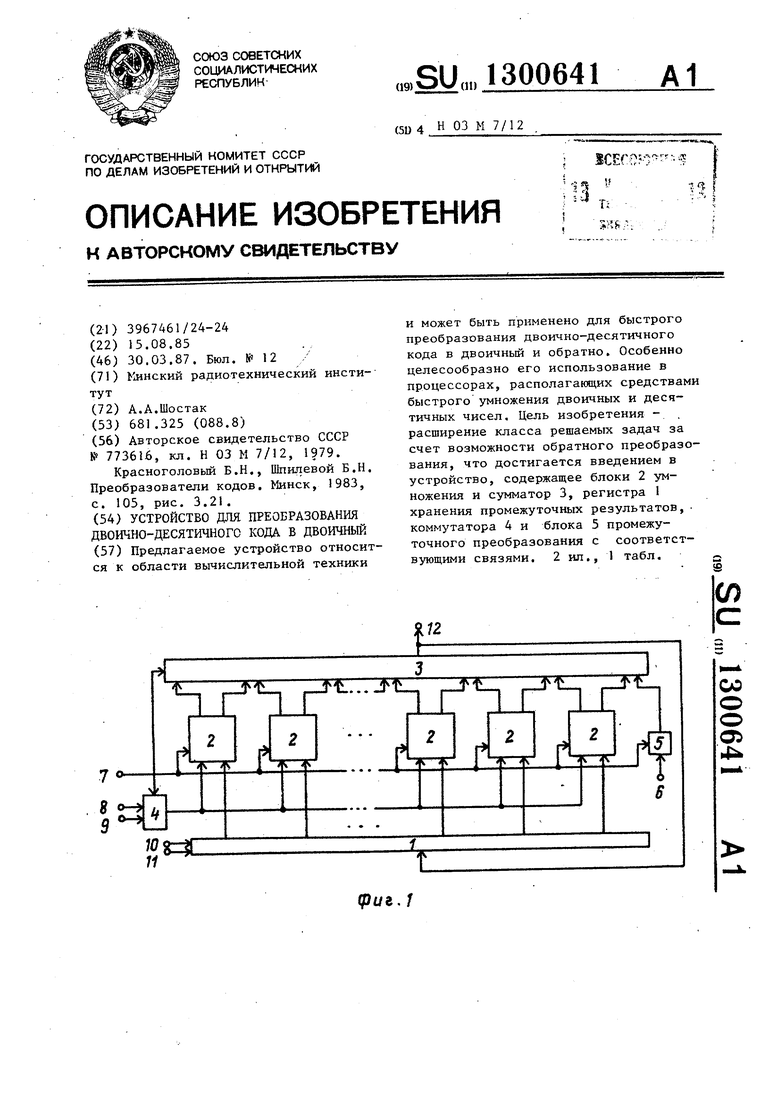

Регистр I предназначен для временного хранения (в течение одного такНа фиг.1 приведена структурная схема предложенного устройства; на фиг.2 - один из вариантов реализации блока 5.

Устройство содержит регистр 1 хранения промежуточных результатов, блок 2 умножения, сумматор 3, коммутатор 4, блок 5 промежуточного преобразования, информационный вход 6 устройства, вход 7 задания режима устройства, первый 8 и второй 9 входы задания констант устройства, вход 10 установки и вход 11 разрешения

коммутатора 4 с входа 9 второй константы устройства подается значение та работы устройства) значений про- двоично-десятичного кода величины межуточных результатов преобразова- 30 2 , где 1 4,5,6,... - число од- ния. Его разрядность зависит от раз- новременно обрабатываемых двоичных рядности преобразуемых чисел. Он может быть реализован на двухтактных синхронных D-триггерах с установочцифр исходного операнда. Число одновременно обрабатываемых цифр, например двоичного операнда, может ными входами, например, на ИС 500 ТМ 35 быть и меньше, чем четыре. Однако,

131.

Блоки 2 умножения комбинационного типа и предназначены для перемноже-- ния малоразрядных сомножителей. В зависимости от сигнала на их входе настройки они осуществляют либо двоичное умножение, либо десятичное. В общем случае эти блоки могут иметь самую разную конфигурацию. Однако 13 дальнейшем предполагается что каждый блок 2 вьшолняет умножение К-разрядных десятичных сомножителей или 4К-ДВОИЧНЫХ разрядных сомножителей, где К 2,3,4,... Блоки умножения обеспечивают достаточно высокую скорость обработки информации.

Сумматор 3 предназначен для быстрого суммирования с учетом весов разрядов произведений, образованных на выходах блоков 2 умножения. Это сумматор двухвходовой и комбинационного типа. К первой группе его

входов подключены выходы значений младших разрядов произведений блоков 2 умножения (на фиг.З эти выходы блоков 2 показаны справа), а ко второй группе подключены вьгходы значений старших разрядов произведений. Входы младших разрядов второй группы сумматора 3 соединены с выходами блока 5 преобразования. В зависи-

мости от значения сигнала на входе настройки сумматора 3 он осуществляв этом случае отпадает надобность применения в устройстве блока 5 преобразования. Коммутатор 4 может быть реализован на логических элементах типа 2И - 2ИЛИ, например, на ИС 5СОЛС118.

Блок 5 комбинационного типа и предназначен для преобразования Р цифр двоично-десятичного кода в двоичный ( режим преобразования двоично- десятичного кода в двоичный) или 1 цифр,двоичного кода в двоично-десятичный код (режим преобразования двоичного кода в двоично-десятичный).

Он может быть выполнен в виде композиции двух узлов: узла преобразования двоично-десятичного кода в двоичный код и узла преобразования двоичного кода в двоично-десятичный,

выходы которых подключены к дьум

группам информационных входов коммутатора, управляющий вход которого соединен с входом 7 задания режима устройства. Каждый из узлов может

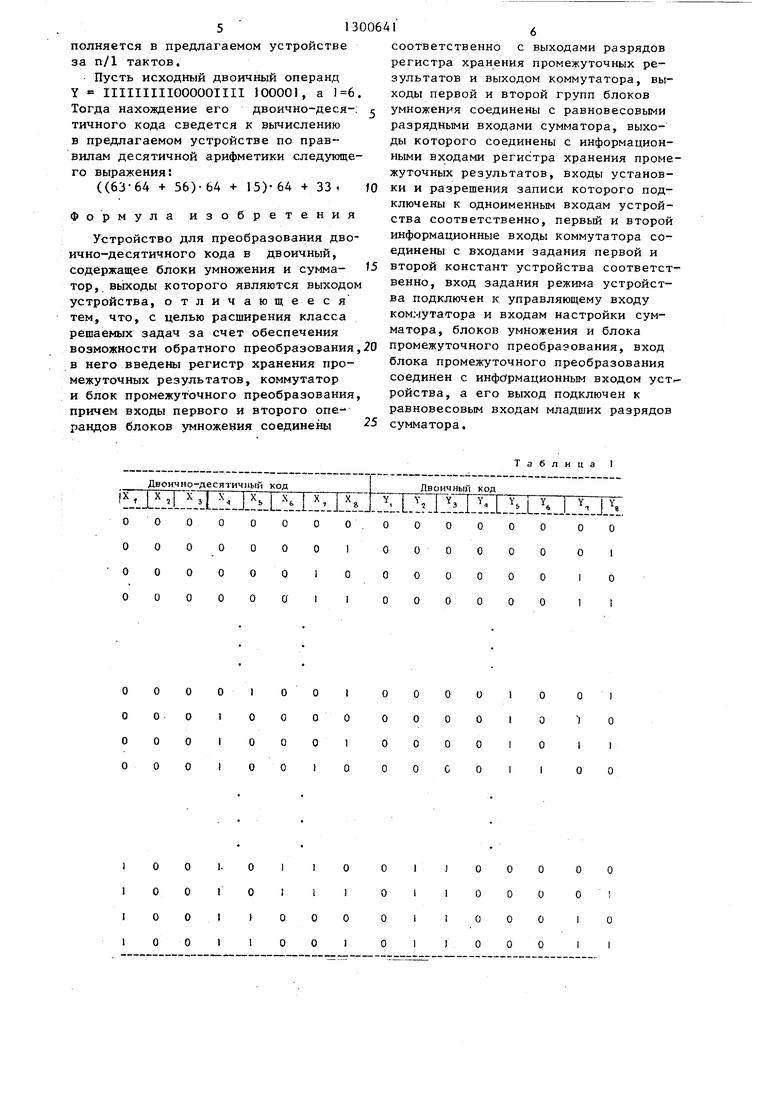

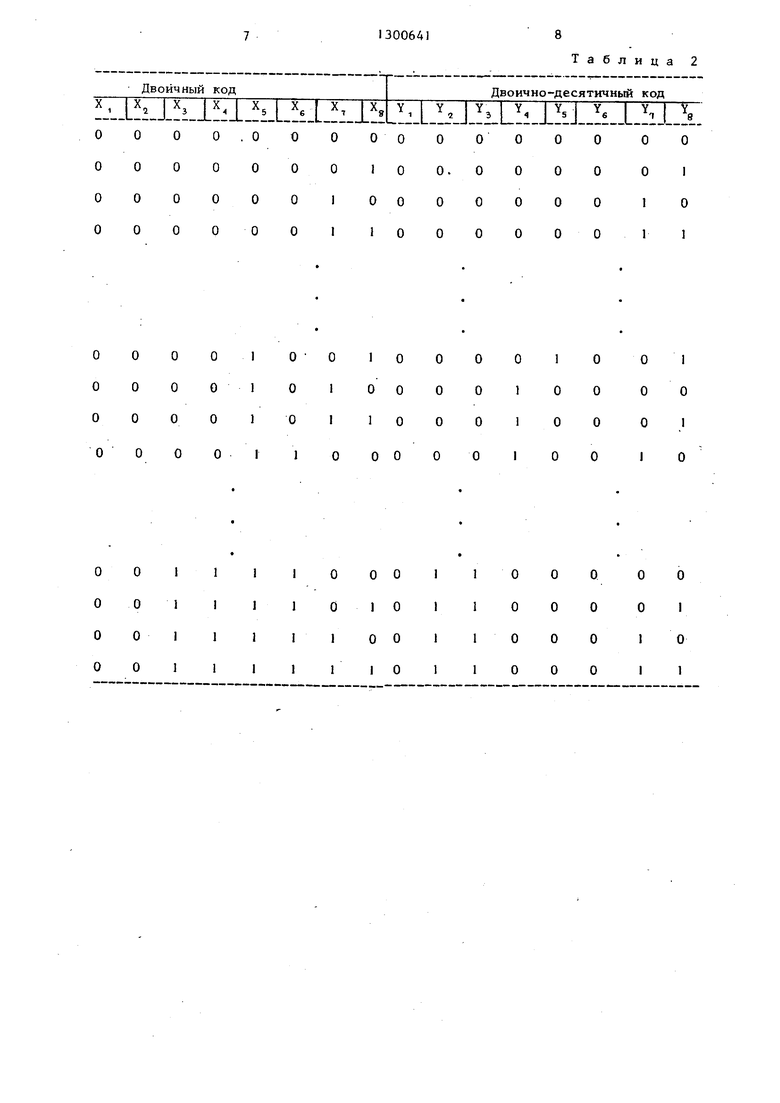

быть реализован любым из известных методов. На фиг.2 в качестве примера показан вариант реализации блока 5 преобразования на ПЗУ для случая, когда в каждом такте работы устройства преобразуются две цифры десятичного операнда и шесть цифр двоичного операнда, т.е. когда Р 2 и 1 6. В качестве ПЗУ применены ИС 500РЕ149 емкостью 256x4. В режиме преобразования двоично-десятичного кода в двоичный с разрешения сигнала на входе 7 устройства выбирается информадия из

ПЗУ 13;, 13

3

а в случае

обратного преобразования - из ПЗУ 13,, 13 , . Выходу ПЗУ 13, 13 и 13 , 13 объединены монтажным ИЛИ. В табл. 1 приведен порядок записи

информации в ПЗУ 13

13,

В третьем Такте, так же как предыдущем, осуществляется умно ние, содержимого регистра 1 на чение первой константы и подсум вание к младшим разрядам получи ся при этом произведения двоичн кода Р следующих десятичных циф исходного операнда. Сформирован на выходах сумматора 3 результа записывается в регистр 1 с разр

в табл.2 - порядок записи информации уп сигнала на входе 11 устройства,

в ПЗУ 13 2 и 13

Работу устройства рассмотрим в двух режимах.

Преобразование двоично-десятичного кода в двоичный. В исходном состо-25 янии на вход 7 задания режима устройства подан управляющий потенциал, который на протяжении всего процесса преобразования настраивает блоки 2 на умножение двоичных чисел, сум- JQ матор 3 - на сложение; двоичных чисел, коммутатор 4 - на пропуск с входа 8 первой кода величины w ,

преобразование Р десятичных-цифр исходного операнда в двоичный код.

В первом такте работы устройства одновременно с записью исходного десятичного операнда в приемный регистр (этот регистр на фиг,1 не д показан, а значение его старших Р (разрядов подается на вход 6 устройства) осуществляется установка регистра 1 в ноль путем подачи импульконстанты двоичного Р

10, а блок 5 - на

35

Так продолжается до тех пор, ка не будет преобразованы все m тичных цифр исходного операнда. Окончательный результат формиру ся на выходах сумматора 3 и пос на выход 12 устройства. Собстве преобразование в устройстве вып няется за т/р тактов.

Б предлагаемом устройстве пр разование организовано фактичес по схеме Горнера. Пусть исходны десятичный операнд X 73521019 а Р 2. Тогда нахождение его д ичного кода сведется к вычисле в предлагаемом устройстве по п вилам двоичной арифметики следу выражения:

((1001001-1100100+110100)1 11001 +1010) 1100100+10011.

Преобразование двоичного ко в двоично-десятичный. В исходно состоянии на вход 7 задания реж устройства подан управляющий по циал, который на протяжении все

са на первый управляющий вход 10 уст-45 процесса преобразования настраивает

ройства. На этом первый такт работы устройства заканчивается.

Во втором такте с помощью блоков 2 и сумматора 3 формируется: произведение содержимого регистра 1 (в 50 этом такте содержимое регистра 1 равно нулю на значение первой константы и подсуммирование к младшим разрядам получившегося при этом произведения двоичного кода Р самых 55 старших десятичный цифр исходного операнда (этот код образуется на выходах блока 5). Сформированный на выходах сумматора 3 результат запиблоки 2 на умножение десятичных чисел, сумматор 3 - на сложение десятичных чисел, коммутатор 4 - на про пуск с входа 9 второй константы двоично-десятичного кода величины 2t а блок 5 - на преобразование 1 двоич ных цифр исходного операнда в двоично-десятичный код.

Далее устройство работает аналогично, как при рассмотрении преобразования двоично-десятичного кода в двоичный. Собственно преобразование п-разрядного двоичного операнда вы

сьшается в регистр 1 с разрешения сигнала на входе II устройства. На зтом второй такт заканчивается. Фактически в течение этого такта осу- осуществляется формирование с помощью блока 5 двоичного кода Р самых старших цифр исходного десятичного операнда и запись его в младшие разряды регистра 1,

В третьем Такте, так же как и в предыдущем, осуществляется умно;в е- ние, содержимого регистра 1 на значение первой константы и подсуммиро- вание к младшим разрядам получившегося при этом произведения двоичного кода Р следующих десятичных цифр исходного операнда. Сформированный на выходах сумматора 3 результат записывается в регистр 1 с разрешения

5

д

5

Так продолжается до тех пор, пока не будет преобразованы все m десятичных цифр исходного операнда. Окончательный результат формируется на выходах сумматора 3 и поступает на выход 12 устройства. Собственно преобразование в устройстве выполняется за т/р тактов.

Б предлагаемом устройстве преобразование организовано фактически по схеме Горнера. Пусть исходный десятичный операнд X 73521019, а Р 2. Тогда нахождение его двоичного кода сведется к вычислению в предлагаемом устройстве по правилам двоичной арифметики следующего выражения:

((1001001-1100100+110100)1 1100100+ +1010) 1100100+10011.

Преобразование двоичного кода в двоично-десятичный. В исходном состоянии на вход 7 задания режима устройства подан управляющий потенциал, который на протяжении всего

процесса преобразования настраивает

блоки 2 на умножение десятичных чисел, сумматор 3 - на сложение десятичных чисел, коммутатор 4 - на пропуск с входа 9 второй константы двоично-десятичного кода величины 2t , а блок 5 - на преобразование 1 двоичных цифр исходного операнда в двоично-десятичный код.

Далее устройство работает аналогично, как при рассмотрении преобразования двоично-десятичного кода в двоичный. Собственно преобразование п-разрядного двоичного операнда выды которого соединены с информационными входами регистра хранения промежуточных результатов, входы установ5 1300641и

полняется в предлагаемом устройствесоответственно с выходами разрядов

за n/l тактов,регистра хранения промежуточных ре Пусть исходный двоичный операндзультатов и выходом коммутатора, выY IIIIIIIIIOOOOOIIII J00001, а .ходы первой и второй групп блоков

Тогда нахождение его двоично-деся-; умножения соединены с равновесовыми

тичного кода сведется к вычислениюразрядными входами сумматора, выхо- в предлагаемом устройстве по прав- вилам десятичной арифметики следующего выражения

((6364 + 56)-64 + 15) 64 +33 fOки и разрешения записи которого подключены к одноименным входам устройФормула изобретенияства соответственно, первьй и второй

Устройство для преобразования дво-информационные входы коммутатора соично-десятичного кода в двоичный,единены с входами задания первой и

содержащее блоки умножения и сумма- 15второй констант устройства соответсттор,. выходы которого являются выходомвенно, вход задания режима устройстустройства, отличающееся ва подключен к управляющему входу

тем, что, с целью расширения классакоммутатора и входам настройки сумрешаемых задач за счет обеспеченияматора, блоков умножения и блока

возможности обратного преобразования,20промежуточного преобразования, вход

в него введены регистр хранения про-блока промежуточного преобразования

межуточных результатов, коммутаторсоединен с инфсУрмадионным входом устг

и блок промежуточного преобразования,ройства, а его выход подключен к

причем входы первого и второго one-равновесовым входам младших разрядов

рандов блоков умножения соединены сумматора.

ды которого соединены с информационными входами регистра хранения промежуточных результатов, входы установразрядными входами сумматора, выхо-

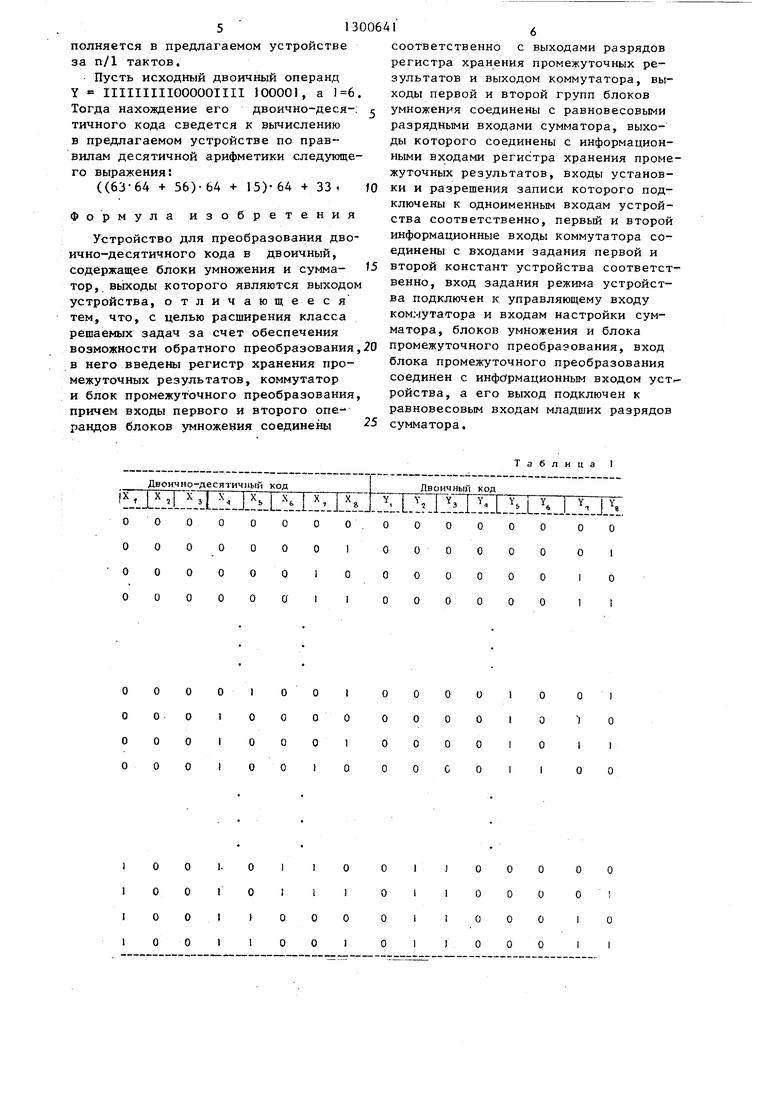

Таблица 1

О О О 01 О О О 01 00001

О

О

о

о I

оо

оо

оо

оо

Таблица 2

Редактор И.Сегляник

Составитель А.Шостак Техред А.Кравчук

Заказ 1160/56 Тираж 902Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фие.г

Корректор Г.Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Реверсивный преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1501278A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1624698A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

Предлагаемое устройство относится к области вычислительной техники и может быть применено для быстрого преобразования двоично-десятичного кода в двоичный и обратно. Особенно целесообразно его использование в процессорах, располагающих средствами быстрого умножения двоичных и десятичных чисел. Цель изобретения - , расширение класса решаемых задач за счет возможности обратного преобразования, что достигается введением в устройство, содержащее блоки 2 умножения и сумматор 3, регистра 1 хранения промежуточных результатов, коммутатора 4 и блока 5 промежуточного преобразования с соответствующими связями. 2 ил., 1 табл. S 05 . (риг, 1

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Красноголовый Б.Н., Шпилевой Б.Н | |||

| Преобразователи кодов | |||

| Минск, 1983, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-30—Публикация

1985-08-15—Подача