(54) ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Аналоговое запоминающее устройство | 1978 |

|

SU680058A1 |

| Сумматор | 1983 |

|

SU1101863A1 |

| Динамический регистр сдвига | 1977 |

|

SU739655A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

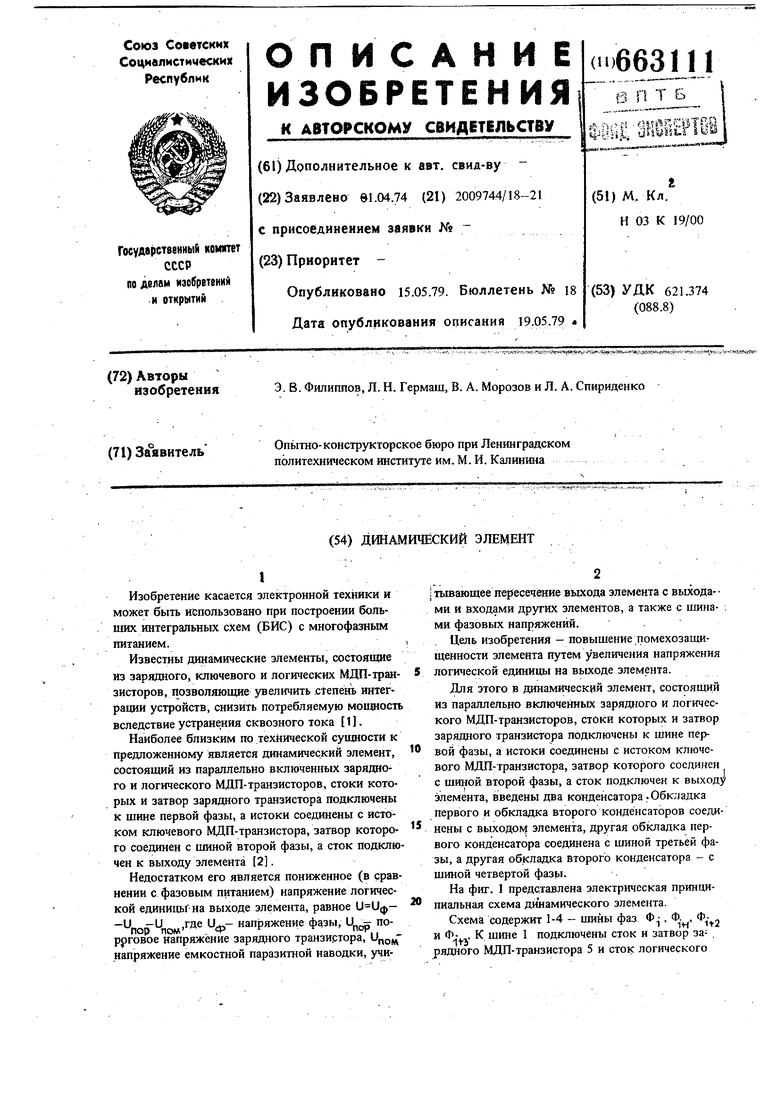

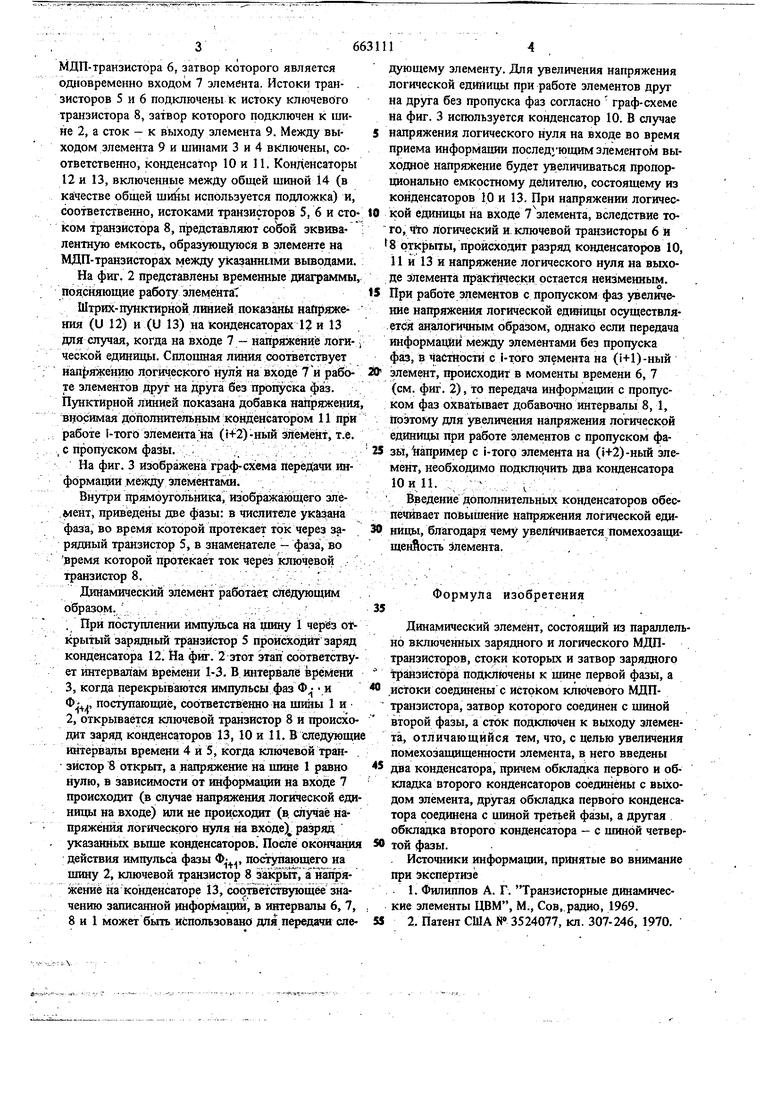

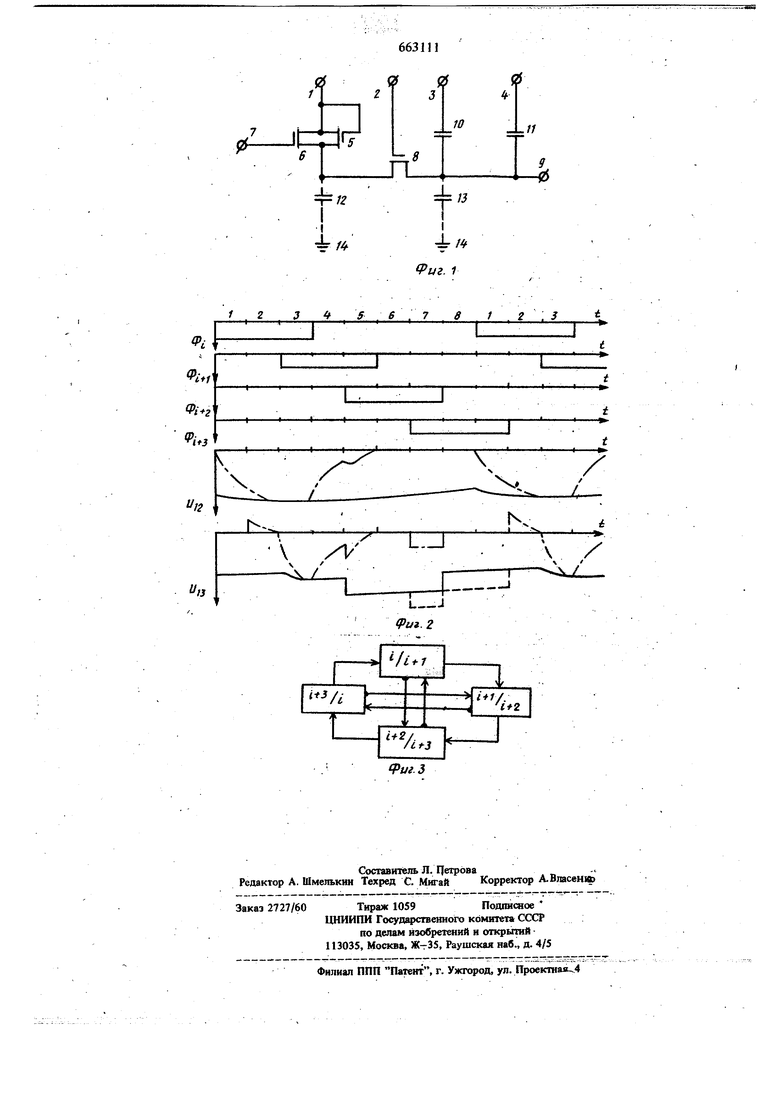

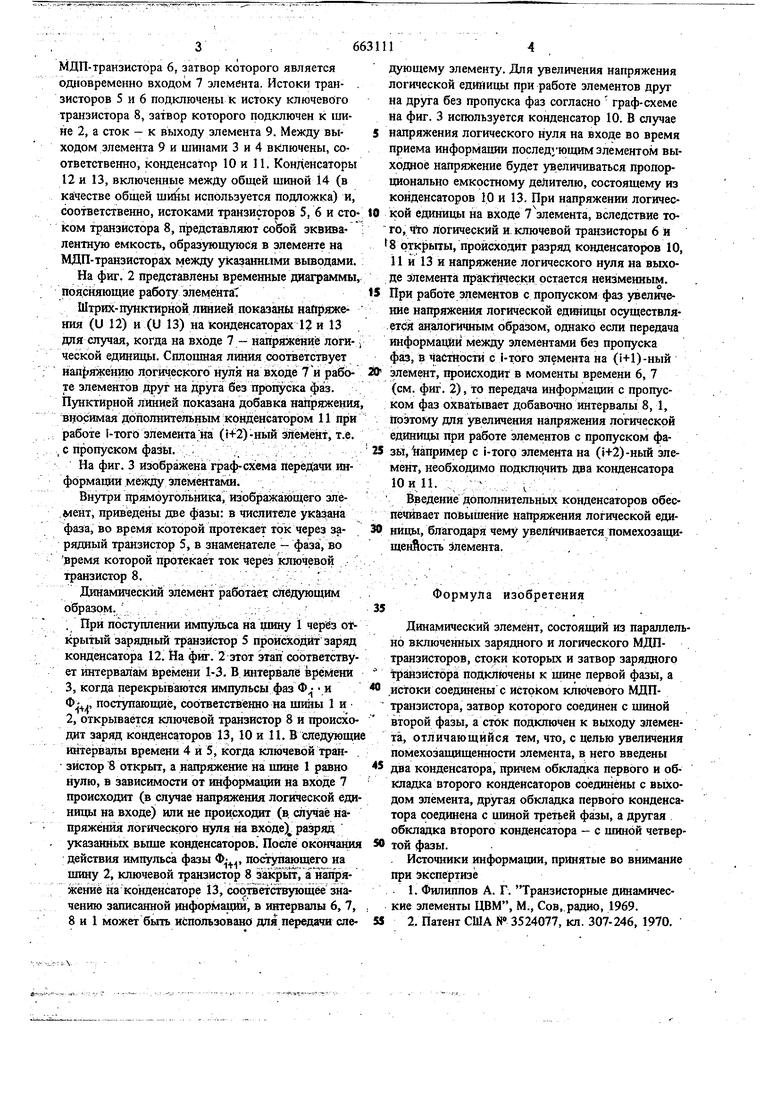

Изобретение касается электронной техники и может быть использовано при построении больших интегральных схем (БИС) с многофазным питанием. Известны динамические элементы, состояидае из зарядного, ключевого и логических МДП-транзисторов, позволяющие увеличить ,ctenem интеграции устройств, снизить потребляемую мощность вследствие устранения сквозного тока 1 . Наиболее близким по технической сущности к предложенному является динамический элемент, состоящий из параллельно включенных зарядного и логического МДП-транзисторов, стоки которых и затвор зарядного транзистора подключены к шине первой фазы, а истоки соединены с истоком ключевого МДП-транзистора, затвор которого соединен с шиной второй фазы, а сток подклю чен к выходу элемента 2. Недостатком его является пониженное (в сравнении с фазовым питанием) напряжение логической единицы на выходе элемента, равное -UnQp-U o,rae напряжение фазы, Ц, поррговое напряжение зарядного транзистора, напряжение емкостной паразитной наводки, учиIтьшающее пересечение выхода элемента с выходами и входами других элементов, а также с шина- . ми фазовых напряжений. . Цель изобретения - повышение помехозащищенности элемента путем увеличения напряжения логической единищз на выходе элемента. Для этого в динамический элемент, состоящий из параллельно включенных зарядного и логического МДП-транзисторов, стоки которых и затвор зарядного транзистора подключены к шине первой фазы, а истоки соединены с истоком ключевого МДП-транзистора, затвор которого соединен с шиной второй фазы, а сток подключен к выходу элемента, введены два конденсатора. Обкладка первого и обкладка второго конденсаторов соединены с выходом элемента, другая обкладка первого конденсатора соединена с шиной третьей фазы, а другая обкладка второго конденсатора - с шиной четвертой фазы. На фиг. 1 представлена электрическая принш пиальная схема динамического элемента. Схема содержит 1-4 - шины фаз Ф , Ф. , Ф- „ IT IT и Ф- . к шине 1 подключены сток и затвор за- . ядного МДП-транзистора 5 и сток логического МДП-транзистора 6, затвор которого является одновременно входом 7 элемента. Истоки транзисторов 5 и 6 подключены к истоку ключевого транзистора 8, затвор которого подключен к шине 2, а сток - к выходу злемента 9. Между выходом элемента 9 и шинами 3 и 4 включены, соответственно, конденсатор 10 и И. Конденсаторы 12 и 13, включенные между общей шиной 14 (в качестве общей шийы используется подложка) и, соответственно, истоками транзисторов 5,6 и сто koM транзистора 8, представляют собой эквивалентную емкость, образующуюся в элементе на МЯП-транзисторС С между указанными вьшодами. На фиг. 2 представлены временные диаграммы поясняющие работу элемента Штрих- пунктирной линией показаны найряжения (и 12) и (и 13) на конденсаторах 12 и 13 для случая, когда на входе 7 - напряжение логической единищ 1. Сплошная линия соответствует иап| яжению логического нуля на входе 7 и работе элементов друг на iapyra без пропуска фаз. Пунктирной линией показана добавка напряжения вносимая дополнительным конденсатором 11 при работе 1-тогЬ элементана 0+2)-ный эЛемёнт, т.е. , с пропуском фазы. ;. На фиг. 3 изображена граф-схема передачи информации между элементами. Внутри прямоугольника, изображающего злемент, приведены две фазы: в числителе указана фаза, во время которой протекает ток через зарядный транзистор 5, в знаменателе - фаза, во время которой протекает ток через ключевой транзистор 8. Динамический злемент риботйп следующим образом...: . При поступлении импульса на щину 1 через открытый зарядный транзистор 5 происходи заряд конденсатора 12. На фиг. 2 этот этап соответству ет интервалам времени 1-3. В интервале времени 3, когда перекрываются импульсы фаз Ф-., постзотающие, соответственно на щи1{ы 1 и 2, открывается ключевой транзистор 8 и происхо дит зарад конденсаторов 13, 10 и 11. В следующи инте рвалы времени 4 и 5, йогда ключевой транзистор 8 открьгг, а напряжение на шине 1 равно нулю, в зависимости от информации на входе 7 происходит (в случае напряжения логической еди на входе) или не происходит (в. случае напряжения логического нуля на входе) разряд указанных вьппе конденсаторов. После окончани действия импульса фазы ., поступающего на шину 2, ключевой транзистор 8 isakpire, анагф:яжёниё на к;окденсаторе 13, соотаётствующее значению записанной информации, в интервалы 6, 7, 8 и 1 может быть использовано для передачи сле дующему элементу. Для увеличения напряжения логической едийицы при работе элементов друг на друга без пропуска фаз согласно граф-схеме на фиг. 3 используется конденсатор 10. В случае напряжения логического нуля на входе во время приема информации последующим элементом выходное напряжение будет увеличиваться пропорционально емкостному делителю, состоящему из конденсаторов 10 и 13. При напряжении логической единицы на входе 7 элемента, вследствие того, что Логический и ключевой транзисторы 6 и 8 открыты, происходит разряд конденсаторов 10, 11 и 13 и напряжение логического нуля на выходе з лемента практически остается неизменным. При работе элементов с пропуском фаз увеличение напряжения логической единицы осуществляете) анздогичным образом, однако если передача информации между элементами без пропуска фаз, в паСтМости с i-Toro элемента на (|+1)-ный элемент, происходит в моменты времени 6, 7 (см. фиг. 2), то передача информации с пропуском фаз oxBatHBaeT добавочно интервалы 8, 1, поэтому для увеличения напряжения логической единицы при работе элементов с пропуском фазы,например с i-того элемента на ((+2)-ный элемент, необходимо подключить два конденсатора 10 и 11. ;.,: ,;г..,.,: .: .;. ... Введение дополнительных конденсаторов обеспечивает повышение напряжения логической единицы, благодаря чему увеличивается помехозащищенйость Злемента., Формула изобретения Динамический элемент, состоящий из параллельно включенных зарядного и логического МДПтранзисторов, стоки которых и затвор зарядного 1)ййзист6ра подключены к шине первой фазы, а истоки соединены с истоком клю чевого МДПтранзистора, затвор которого соединен с шиной второй фазы, а сток подключен к выходу элемента, отличающийся тем, что, с целью увеличения помехозащищенности элемента, в него введены два конденсатора, причем обкладка первого и обКладка второго конденсаторов соединены с выходом элемента, другая обкладка первого конденсатора соединена с шиной третьей фазы, а другая обкладка второго конденсатора - с шиной четвертой фазы. Источники информации, принятые во внимание При экспертизе 1.Филиппов А. Г. Транзисторные динамические элементы ЦВМ, М., Сов, радио, 1969. 2.Патент США 8 3524077, кл. 307-246, 1970.

%/«

Pi

412

11

ф/«

Рнг. 1

Авторы

Даты

1979-05-15—Публикация

1974-04-01—Подача