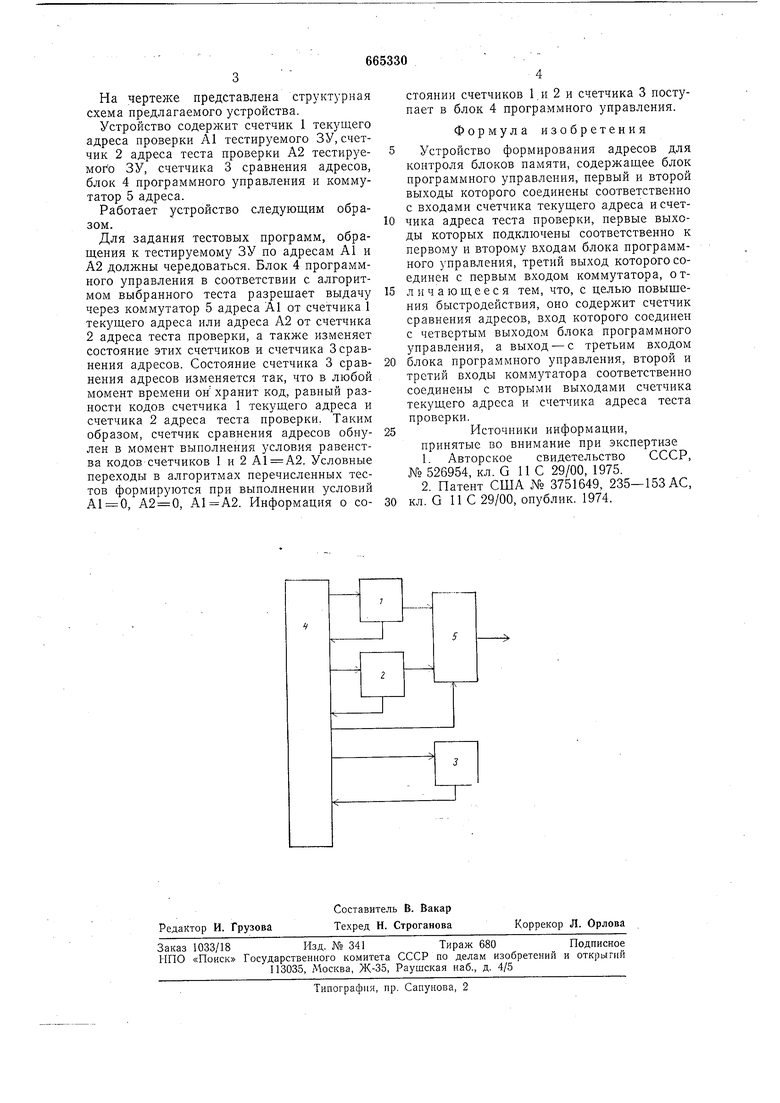

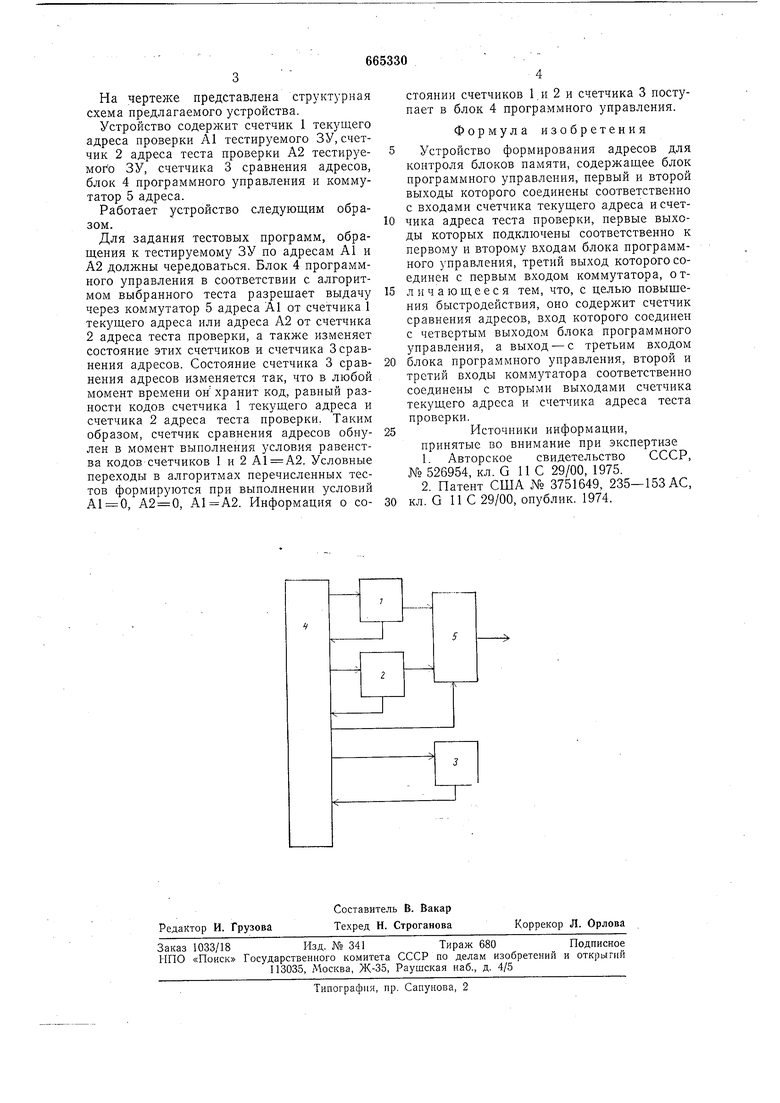

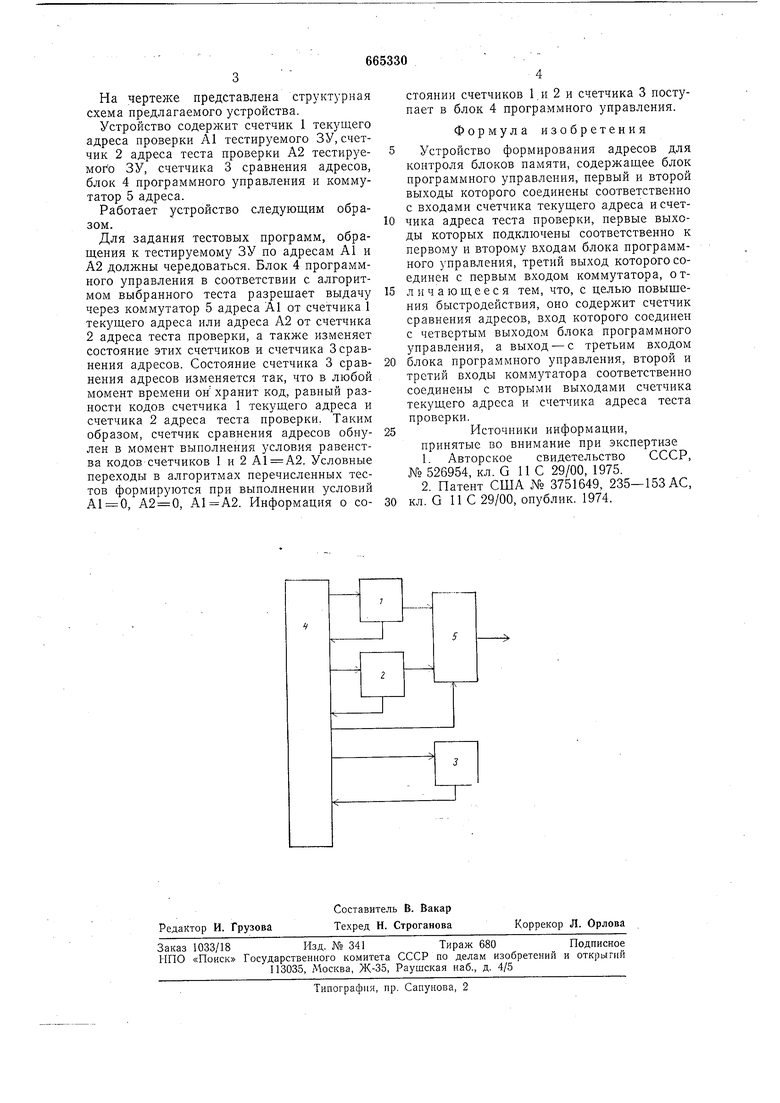

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содерлсит счетчик 1 текущего адреса проверки А1 тестируемого ЗУ, счетчик 2 адреса теста проверки А2 тестируемогЪ ЗУ, счетчика 3 сравнения адресов, блок 4 программного управления и коммутатор 5 адреса.

Работает устройство следующим образом.

Для задания тестовых программ, обращения к тестируемому ЗУ по адресам А1 и А2 должны чередоваться. Блок 4 программного управления в соответствии с алгоритмом выбранного теста разрещает выдачу через коммутатор 5 адреса А1 от счетчика 1 текущего адреса или адреса А2 от счетчика 2 адреса теста проверки, а также изменяет состояние этих счетчиков и счетчика 3 сравнения адресов. Состояние счетчика 3 сравнения адресов изменяется так, что в любой момент времени он хранит код, равный разности кодов счетчика 1 текущего адреса и счетчика 2 адреса теста проверки. Таким образом, счетчик сравнения адресов обнулен в момент выполнения условия равенства кодов счетчиков 1 и 2 . Условные переходы в алгоритмах перечисленных тестов формируются при выполнении условий , А2 0, . Информация о состоянии счетчиков 1.и 2 и счетчика 3 поступает в блок 4 программного управления.

Формула изобретения

Устройство формирования адресов для контроля блоков памяти, содержащее блок программного управления, первый и второй выходы которого соединены соответственно с входами счетчика текущего адреса и счетчика адреса теста проверки, первые выходы которых подключены соответственно к первому и второму входам блока программного управления, третий выход которого соединен с первым входом коммутатора, отличающееся тем, что, с целью повыщения быстродействия, оно содержит счетчик сравнения адресов, вход которого соединен с четвертым выходом блока программного управления, а выход - с третьим входом блока программного управления, второй и третий входы коммутатора соответственно соединены с вторыми выходами счетчика текущего адреса и счетчика адреса теста проверки.

Источники информации,

принятые во внимание при экспертизе

1 Авторское свидетельство СССР, № 526954, кл. G 11 С 29/00, 1975.

2. Патент США № 3751649, 235-153 АС, кл. G 11 С 29/00, опублик. 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1978 |

|

SU711636A1 |

| Многомерный статистический анализатор | 1984 |

|

SU1241259A1 |

| Многопрограммный регулятор температуры | 1983 |

|

SU1136123A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

Авторы

Даты

1979-05-30—Публикация

1977-04-11—Подача