,.-. - - 1

Изобретение относится к вычйспител ной технике н может 0ь1ть использовано для решения дифференциальных уравнений.

Известна аналого Еифровая система, содержащая аналоговую сетку, сопряженную с IIBMJ эта система по; оляет автоматизировать набор и съем решений с аналоговой части iilj.

. Однако при использовании ее для получения решения задач физического поля со сложными условиями или нелинейных дифференциальных уравнений требуется большое время для выполнения последовательных вычислений, поскольку обсчет этих уравнений в узлах производится с помоШ1 ю последовательно действующей ЭВМ Известна также вычислительная систе ма, которая содержит устройство управления, соединенное двухсторонними связями) с устройством ввода-вывода и двухстс нней информационной шиной с коммутато рам, управляющие входы которого сзоединены соответственно с ш 1ходами устройства управления, решающие блоки, квущцлй

из которь-гх включает рё1йстрйгч 1е1айЯ и записи, эпементь И, узел связи, микропроцессор, соединенный двухсторонними связями с запоминающим устройством, выходы которого подалюченБ соб1 ёг12твенно к входам регисг|Е)об чтения и записи, выходь которых через сбогветст-вующие элементы И подключеаы к входам узла связи, выход которого соединен со входом запоминающего устройства, управляющие входы микропроцессора, элементов И, регист ра записи каждого решающего блока соединены с соответствующими вьтходамй устройства управления 2.

Однако указанная системй не может быть иотользована для решения сложных нелинейных дифференциальных уравнений в частных производНьгх с заданными в форме обыкновенных дифференциальньгх урав-, нений условиями в каждом узле.

Целью изобретения является расширение функинональных возможностей путем обеспечения решения нелинейных дифференциальных уравнений в частных производных. Для этого в систему введены блок памяти, мультиплекоэр, узловые процессоры, каждый из которых включает арифметическо-логическое устройство, соединенное управляющим входом с выходом устройства управления, узловой мультиплексор, соединенный двухсторонними связями с арифме тическо-логическим устройством, с регист ром и с регистрами смежных узловых процессов, мультиплексор соединен двухсто-- ронней информационной шиной с устройством управления и двухсторонними связями с арифметическо-логическим устройством каждого узлового процессора, управляющий вход блока памяти соединен с соответствующим выходом устройства управления, выход блока памяти подключен к ВХОДУ арифметическо-логического устрой-ч ства каждого узлового процессора, а в каждь1й из решающих, блоков введены постоянное запоминающее устройство И регистр адреса, соединёйный двухсторонней связью с микропроцессором, выход регист ра адреса подключен к входу постоянного запоминающего устройства, выход которог6 соединен со входом микропроцессора.

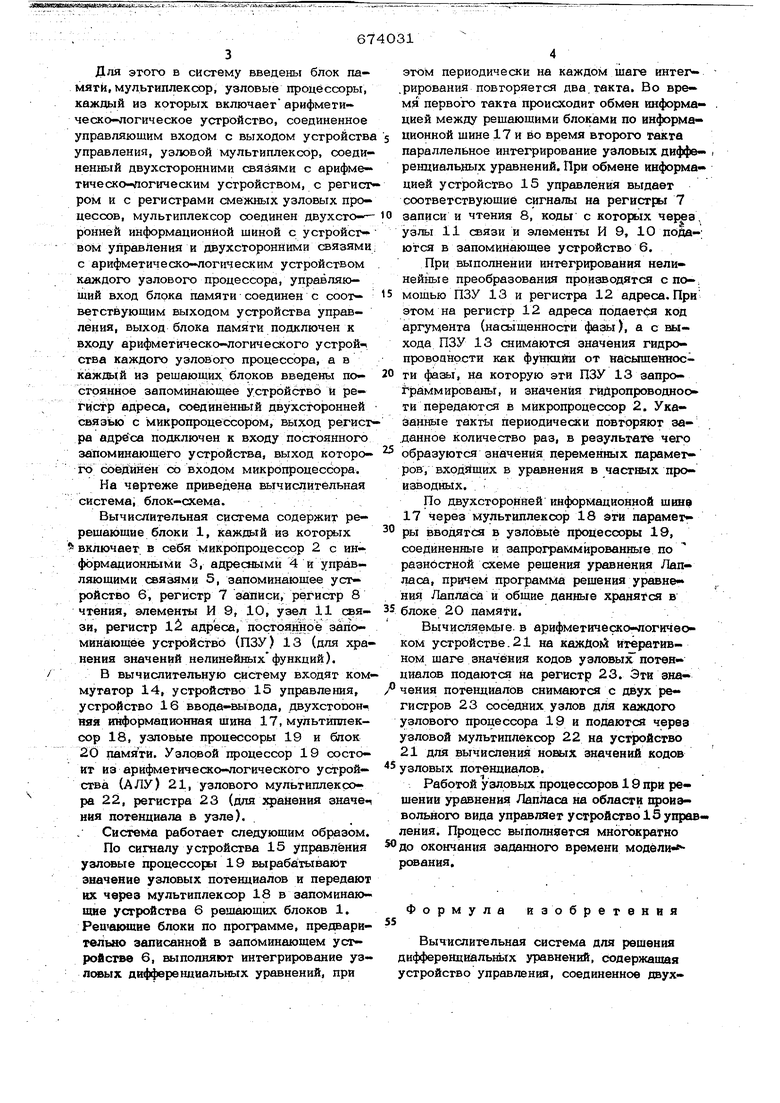

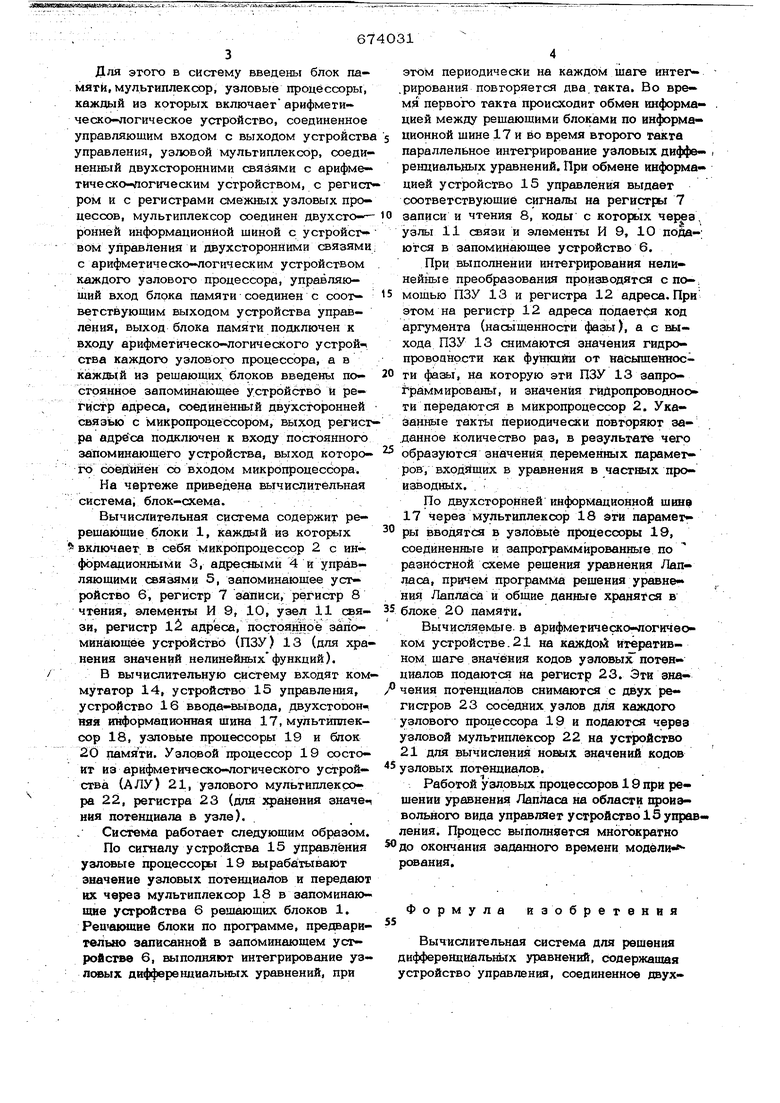

На чертеже приведена вычислительная система, блок-схема.

Вычислительная система содержит ререшающие блоки 1, каждый из KOTOffcix включает в себя микропроцессор 2 с информационными 3, адресными 4 и управляющими связями 5, запоминающее устройство 6, регистр 7 записи, регистр 8 чтения, элементы И 9, 10, узел 11 связи, регистр 1 адреса, постоянное запоминающее устройство (ПЗУ) 13 (для хранения значений нелинейных функций).

В вычислительную систему входят коммутатор 14, устройство 15 управления, устройство 16 ввода-вывода, двухстооонч няя информационная шина 17, мультиплексор 18, узловые процессоры 19 и блок 20 памяти. Узловой процессор 19 состоит из арифметическо-логического устройства (АЛУ) 21, узлового мультиплексора 22, регистра 23 (для хранения значе ния потенциала в узле).

Система работает следующим образом.

По сигналу устройства 15 управления узловые процессоры 19 Ызтрабатывают значение узловых потенциалов и передают их через мультиплексор 18 в запоминающие устройства 6 решающих блоков 1. Реш иошве блоки по программе, предварительно записанной в запоминающем устройстве 6, выполняют интегрирование узлсюых дифференциальных уравнений, при

674031

ров, входйщих в уравнения в частных производных.

По двухсторонней информационной шине 17 через мультиплексор 18 эти параметры вводятся в узло)вые процессоры 19, соединенные и запрограммированные по разностной схеме решения уравнения Лапласа, причем программа решения уравнения Лапласа и общие данные хранятся в

блоке 20 памяти.

Вычисляемые в арифметическо-логкчеоком устройстве .21 на каждой итеративном шаге значения кодов узловых потенциалов подаются на регистр 23. Эти значения потенциалов снимаются с двух регистров 23 соседйих узлов для каждого узлового процессора 19 и подаются через узловой мультиплексор 22 на устройство 21 для вычисления новых значений кодов

узловых потенциалов.

Работой узловых процессоров 19 при решении уравнения Лaпhaca на области пройэвольнозх вида управляет устройство 15 управления. Процесс выполняется многократно

до окончания заданного времени модели рования.

Формула изобретения

Вычислительная система для решения днфференциальнЬгх уравнений, содержащая устройство управления, соединенное двухэтом периодически на каждом шаге интег- рирования повторяется два,такта. Во время первого такта происходит обмен информа- . цией между решающими блоками по информационной шине 17 и во время второго гакта параллельное интегрирование узловых диффе- i ренциальных уравнений. При обмене информацией устройство 15 управления выдает соответствующие сигналы на регистры 7 записи и чтения 8, коды с которых через, узлы 11 связи и элементы И 9, 10 пода-; югся в запоминающее устройство 6. При выполнении интегрирования нели- нейтате преобразования производятся спо-, мощью ПЗУ 13 и регистра 12 адреса. При этом на регистр 12 адреса подается код аргумента (нась1щенности фазы), а с шлхода ПЗУ 13 снимаются значения гидропровоанрсти как функции от насыщенносги , на которую эти ПЗУ 13 запро рйммированьг, и значения гидропроводнооти передаются в микропроцессор 2. Указанные такты периодически повторяют заданное количество раз, в результате чего образуются значения переменных парамет

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1429139A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для управления обменом информации | 1981 |

|

SU1109729A1 |

| СИСТЕМА ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2011 |

|

RU2452125C1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

Авторы

Даты

1979-07-15—Публикация

1977-05-20—Подача