1 .

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении цифровых вычислительных машин, специализированных йычислителей и микрокалькуляторов.

Известен цифровой функциональный преобразователь 1, содержащий группу одноразряднь1Х сумматоров, элементы И, НЕ. Его недостатком является большой объем аппаратурных затрат, суш ественно возрастаюш,ий с повышением требуемой точности преобразований.

Наиболее близким техническим решением к изобретению является цифровой функциональный преобразователь 2, содержащий блок памяти, сумматор, регистр сдвига функции и блок умножения.

Недостатком известного цифрового функционального преобразователя является сложность и малое быстродействие.

Целью изобретения является упрощение и повышение быстродействия цифрового функционального преобразователя.

Поставленная цель достигается тем, что цифровой функциональный преобразователь, содержащий блок памяти, сумматор, регистр сдвига функции, блок управления, причем выход блока памяти подключен к первому входу сумматора, выход которого

подключен ко входу регистра сдвига функции, управляющий вход сумматора и управляющий вход регистра сдвига функции подключены соответственно к первому и второму выходу блока управления, содерлшт регистр сдвига аргумента, реверсивный счетчик и блок формирования дополнительного кода, причем выход регистра сдвига аргумента подключен к первому входу блока управления, к адресному входу блока памяти и через блок формирования дополнительного кода ко второму входу сумматора, выход реверсивного счетчика подключен ко второму входу блока управления, третий и четвертый выходы которого подключены соответственно к управляющему входу регистра сдвига аргумента и к управляющему входу реверсивного счетчика.

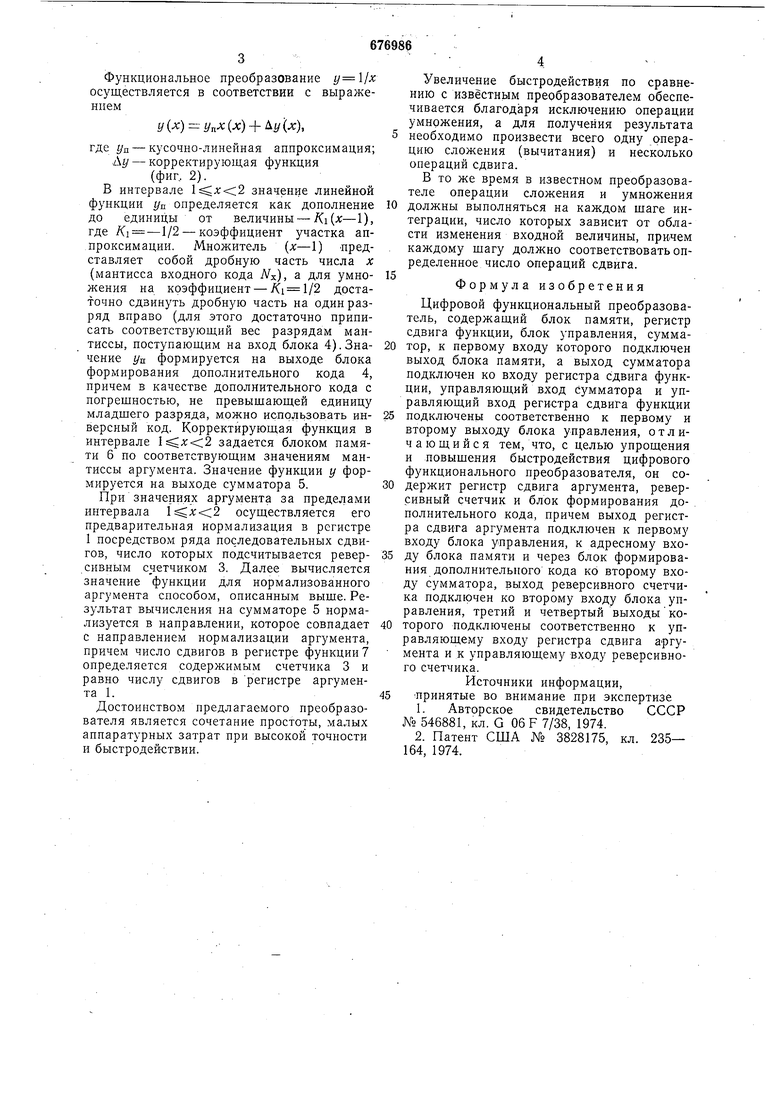

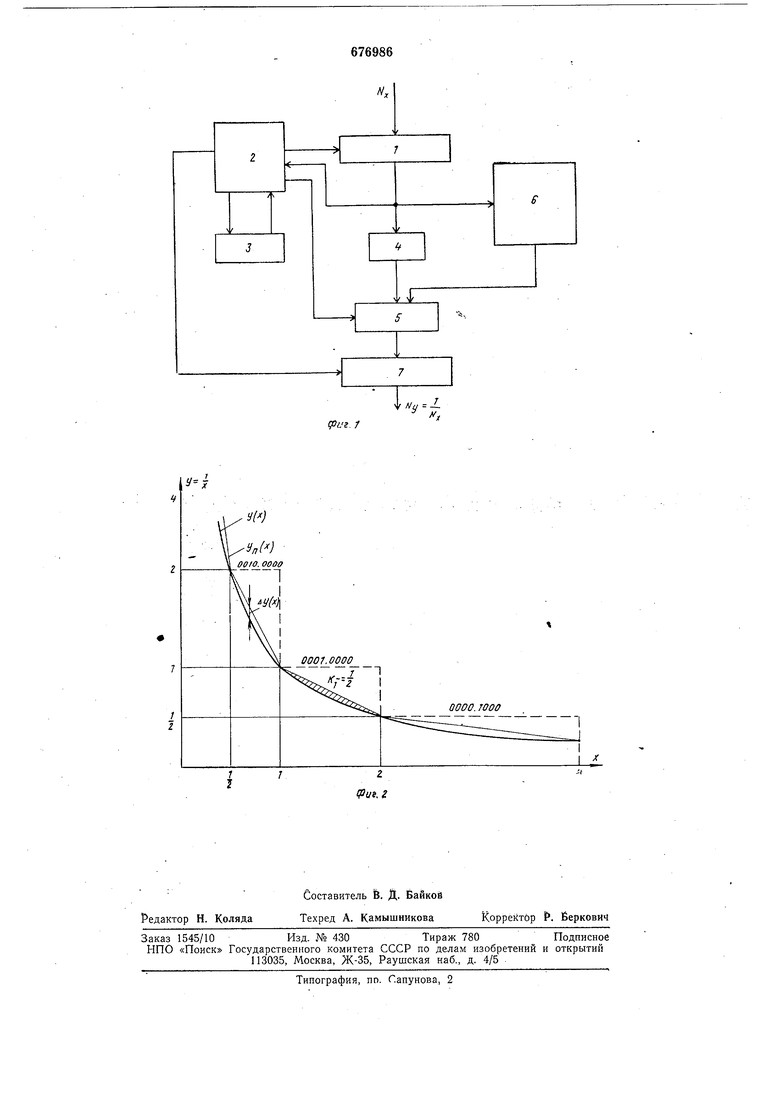

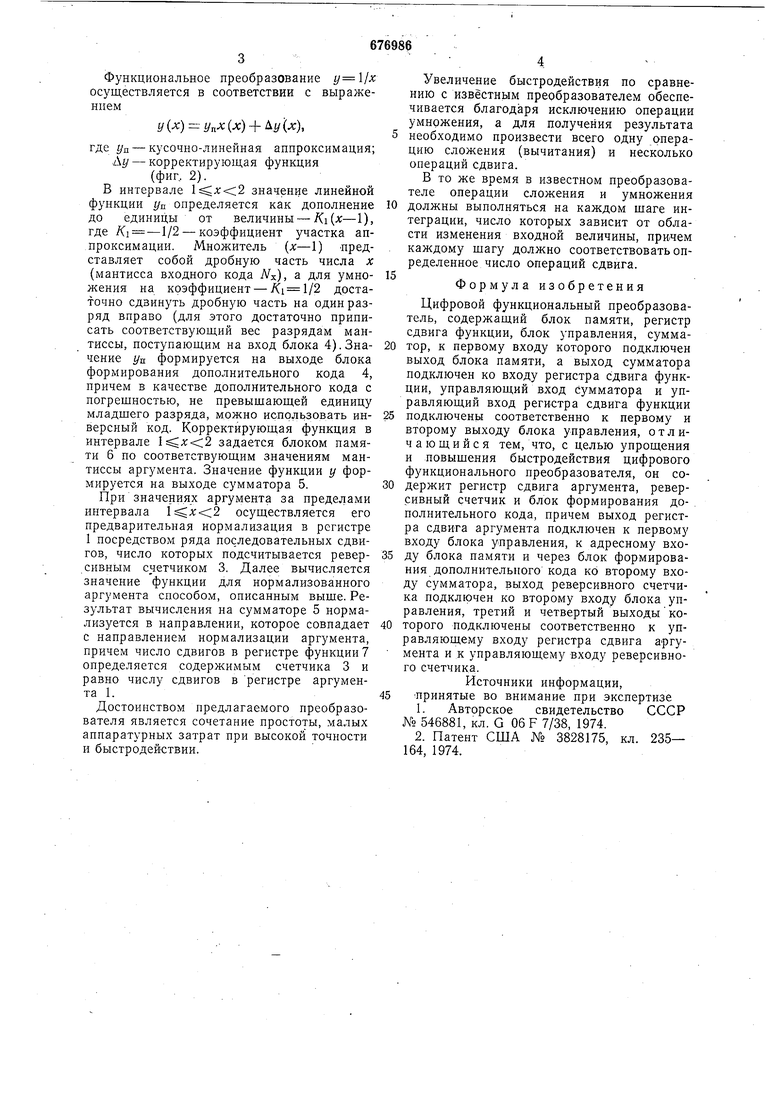

Функциональная схема цифрового функционального преобразователя представлена на фиг. 1; на фиг. 2 - график, иллюстрирующий способ преобразования по закону у 1/х.

Функциональный преобразователь содержит регистр сдвига аргумента 1, блок управления 2, реверсивный счетчик 3, блок формирования дополнительного кода 4, сумматор 5, блок памяти 6, регистр сдвига

функции 7.

Функциональное преобразование осуществляется в соответствии с выражением

у(х ) УпХ(х)(х),

где г/п - кусочно-линейная аппроксимация; Ау - корректирующая функция (фиг,. 2).

В интервале значение линейной функции УН определяется как дополнение до единицы от величины - d (л:-1), где - коэффициент участка аппроксимации. Множитель (х-1) Представляет собой дробную часть числа х (мантисса входного кода NX), а для умножения на коэффициент - /Ci l/2 достаточно сдвинуть дробнзю часть на один разряд вправо (для этого достаточно приписать соответствующий вес разрядам мантиссы, поступающим на вход блока 4). Значение г/п формируется на выходе блока формирования дополнительного кода 4, причем в качестве дополнительного кода с погрешностью, не превышающей единицу младшего разряда, можно использовать инверсный код. Корректирующая функция в интервале задается блоком памяти 6 по соответствующим значениям мантиссы аргумента. Значение функции у формируется на выходе сумматора 5.

При значениях аргумента за пределами интервала осуществляется его предварительная нормализация в регистре 1 посредством ряда последовательных сдвигов, число которых подсчитывается реверсивным счетчиком 3. Далее вычисляется значение функции для нормализованного аргумента способом, описанным выше. Результат вычисления на сумматоре 5 нормализуется в направлении, которое совпадает с направлением нормализации аргумента, причем число сдвигов в регистре функции 7 определяется содержимым счетчика 3 и равно числу сдвигов в регистре аргумента 1.

Достоинством предлагаемого преобразователя является сочетание простоты, малых аппаратурных затрат при высокой точности и быстродействии.

Увеличение быстродействия по сравнению с известным преобразователем обеспечивается благодаря исключению операции умножения, а для получения результата необходимо произвести всего одну операцию сложения (вычитания) и несколько операций сдвига.

В то же время в известном преобразователе операции сложения и умножения должны выполняться на каждом шаге интеграции, число которых зависит от области изменения входной величины, причем каждому шагу должно соответствовать определенное число операций сдвига.

.

Формула изобретения

Цифровой функциональный преобразователь, содержащий блок памяти, регистр сдвига функции, блок управления, сумматор, к первому входу которого подключен выход блока памяти, а выход сумматора подключен ко входу регистра сдвига функции, управляющий вход сумматора и управляющий вход регистра сдвига функции

подключены соответственно к первому и второму выходу блока управления, отличающийся тем, что, с целью упрощения и повышения быстродействия цифрового функционального преобразователя, он содержит регистр сдвига аргумента, реверсивный счетчик и блок формирования дополнительного кода, причем выход регистра сдвига аргумента подключен к первому входу блока управления, к адресному входу блока памяти и через блок формирования дополнительного кода ко второму входу сумматора, выход реверсивного счетчика подключен ко второму входу блока управления, третий и четвертый выходы которого подключены соответственно к управляющему входу регистра сдвига аргумента и к управляющему входу реверсивного счетчика.

Источники информации,

Принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 546881, кл. G 06 F 7/38, 1974.

2.Патент США № 3828175, кл. 235- 164, 1974.

0i. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

/ Л

0000. го 00

I

fput.i

Авторы

Даты

1979-07-30—Публикация

1978-02-22—Подача