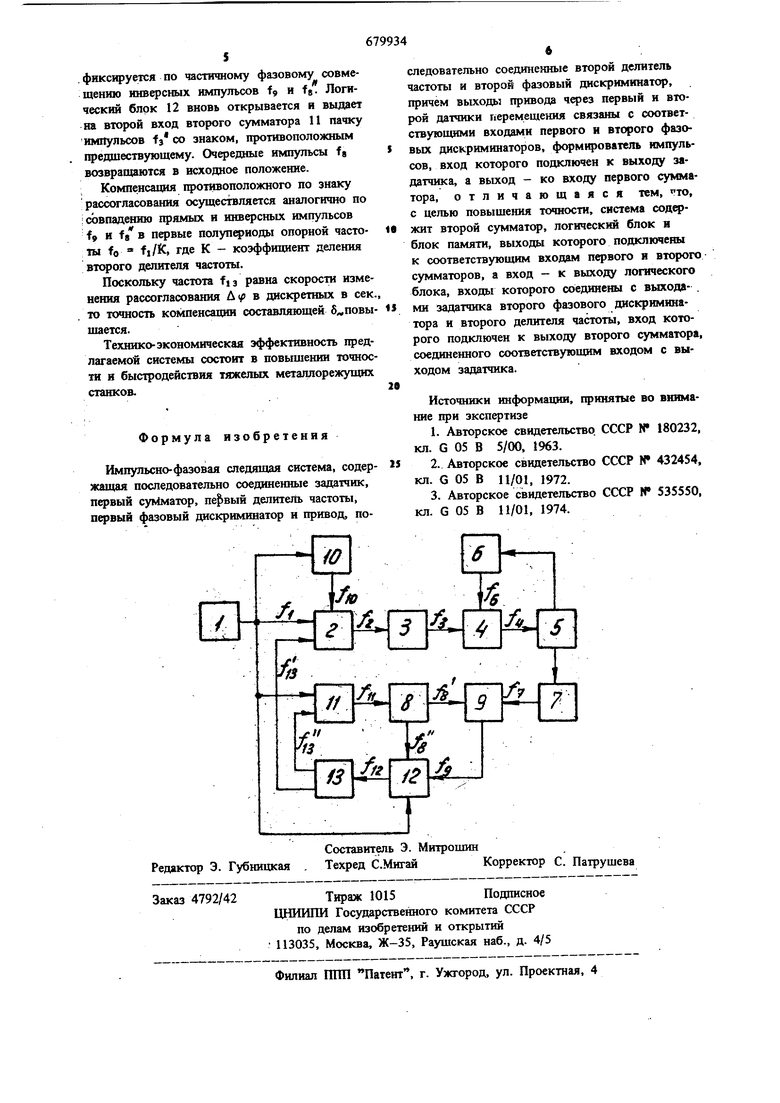

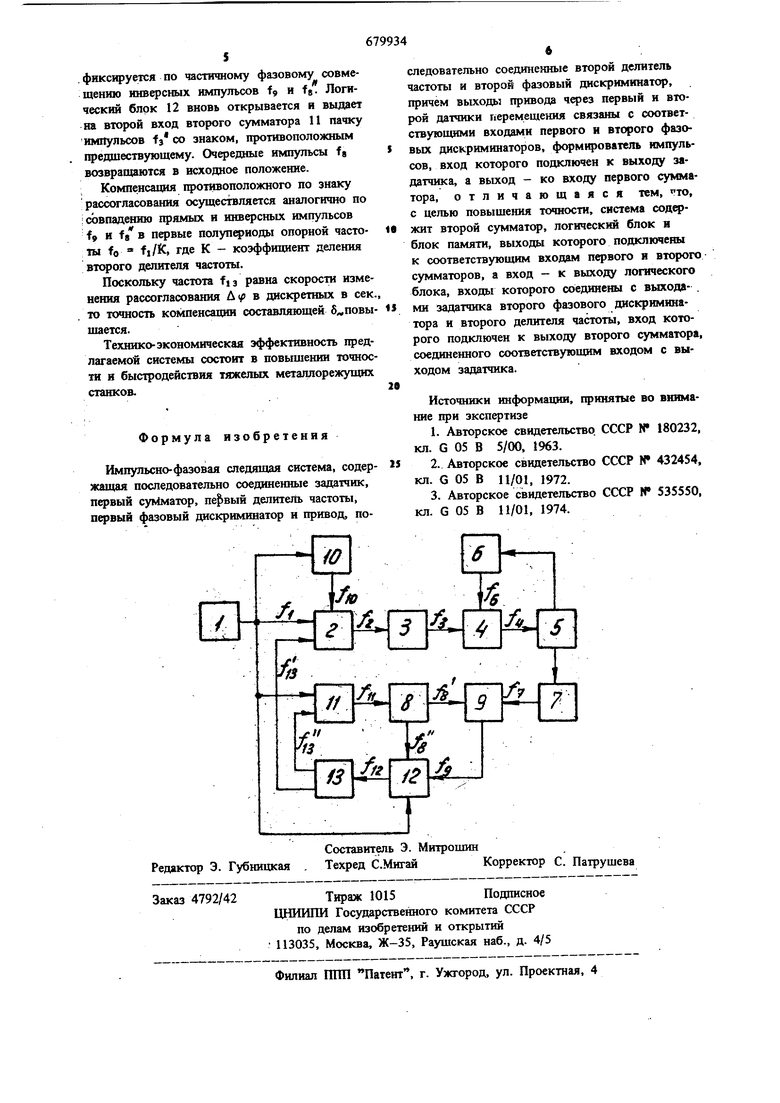

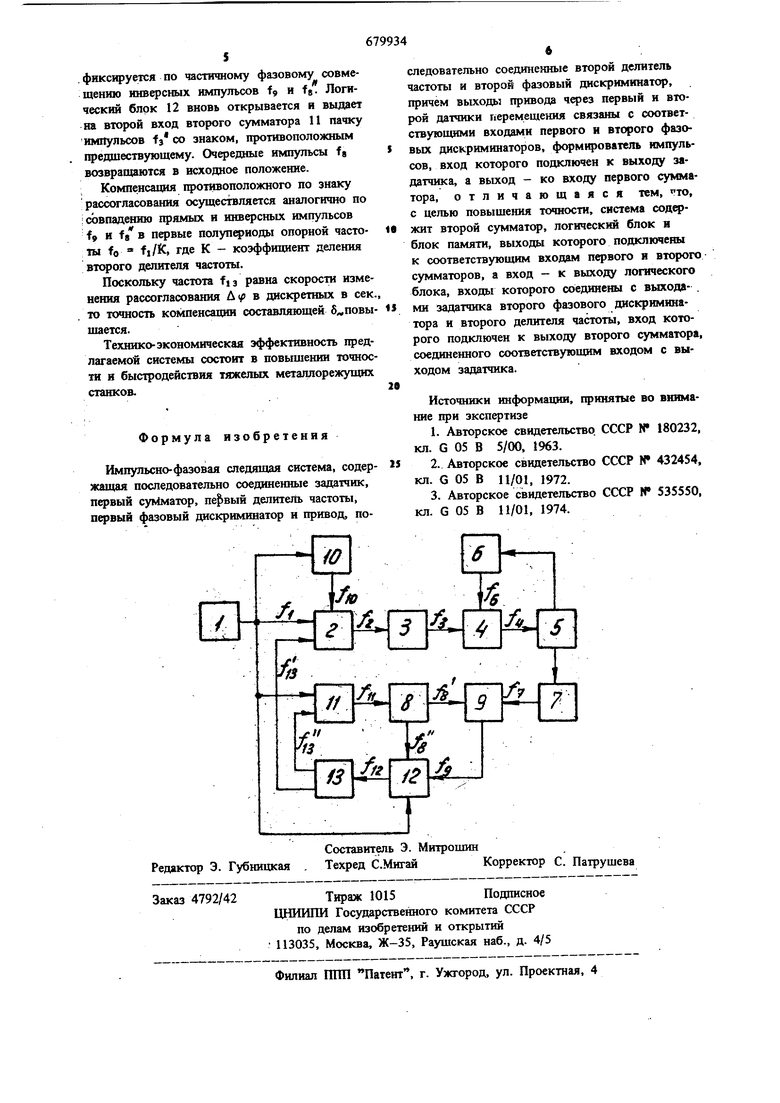

Недостатком системы является низкая точность компенсации переменной составляющей люфта 6 вследствие ее Осуществления с постоянной скоростью независимо от фактической скорости изменения составляющей 5„. Целью изобретения является повыщение точности системы путем компенсации составляющей б со скоростью, равной . Эта цель достигается тем, что следящая сис тема содержит второй сумматор, логический блок и блок памяти, выходы которого подключены к соответствующим входам первого и второго сумматоров, а вход - к выходу логического блока, входы которого соединены с выходами задатчика, второго фазового дискриминатора и второго делителя частоты, вход которого подключен к выходу второго сумматора, соединенного соответствующим вхо дом с выходом задатчика. На чертеже приведена структурная схема следящей системы. Система содержит последовательно соединенные задатчик 1, первый сумматор 2, первый делитель частоты 3, первый фазовый, дискриминатор 4, привод 5 с кинематическим люфто и встроенными до и после люфта соответствен но первым датчиком перемещения 6, выход которого подключен к щ угому входу первого фазового дискриминатора 4, и вторым датчиком , перемещения 7; последовательно соединенные второй делитель частоты 8 и второй фазовый дискриминатор 9, другой вход которого подключен к выходу второго датчика перемещения 7; формирЪватель импульсов 10, вход которого подключен к выходу задатчика 1, а выход - к другому входу первого сумматора 2; второй сумматор 11, вход которого подключен к выходу задатчика 1, а выход - ко входу второго делителя частоты 8; последовательно соещшенные логический блок 12 и блок памяти 13, причем входы логического блока 12 соединены соответственно с выходом задатчика 1, с другим выходом второго делителя частоты 8 и с выходом второго фазового дискриминатора 9, а выхощ 1 блока памяти 13 соединены с соответствующими входами первого сумматора 2 и второго сумматора 11. Здесь приняты условные обозначения: fi - частота задающих импульсов fi Sftfn где fj, ffl - частоты тактовых и программных импульсов; ю.и - частоты импульсов, компенсирую щих постоянную и переменную & составляющие люфта; fs, f - частоты импульсов, модулированных по фазе в функшш частот fio и (или)|| 4. 0 - частоты щиротио-модулированных импульсов} Система работает следующим образом. В исходном состоянии системы импульсы f|v fio отсутствуют, импульсы 1эИ ft, f( и f7. fg и iy находятся в противофазе; скважность импульсов i, fg fg равна 2 и привод S неподвижен при расположении вала двигателя у одной из граннц люфта. При появлении импульсов fn со знаком, противоположным предществующему, включается формирователь импульсов 10 и выдает на второй вход первого сумматора 2 пачку импульсов. Количество и частота импульсов fjo равны соответственно Smin/i и fnmax; здесь Sfnir, минимальная величииа люфта, принятая за постоянную составляющую 5, а I - дискретность системы. В первом сумматоре 2 импульсы fto добавляются к импульсам fi или вычитаются из них в зависимости от нового знака импульсов . fр. Далее изменшие частоты fj преобразуется в пропорциональное изменение фазы импульсов fy и скважности импульсов fio- Привод S форсированно реверсируется. После окончания импульсов fio привод 5 приобретает заданную скорость и направление слежения. Компенсация составляющей д осуществляется по фазовому рассогласованию Д| импульсов fg и fj. Это рассогласование возникает как при реверсе в люфте 5 б (например, в зоне частых реверсов из-за повышенного износа кинематики привода), так и в установившемся режиме слежения (нагфимер, на стыках реек в кинематической цепи шестерня-рейка). При Д(рЯ-й дискреты при перемещении, например, вправо происходит частичное совмеще1ше по фазе импульсов fg и fg. Логический блок 12 открывается и выдает пачку импульсов fit на запись в блок памяти 13. Количество и частота юлпульсов fu равны соответственно Д и f |. С выхода блока памяти 13 эти импульсы с частотой подаются на третий вход первого сумматора 2 и на второй вход второго сумматора 11. Затем преобразуются импульсы f/з так же, как и импульсы fio и привод 5 получает дополнительно Ai)/i дискрет на перемещение вправо. Второй сумматор 11 и второй делитель частоты 8 преобразуют импульсы fis в смещение по фазе очередных импульсов fg иа дискрет вслед за импульсом fg- В результате при последующем появлении импульсов. f9 и fg логический блок 12 остается закрытым, что исключает многократную выдачу импульсов f 12 при одном и том же рассогласовании Д(. После отработки- приводом 5 дискрет, соответствующий по времени импульс возвращается, в заданное положение, которое . фиксируется по частичному фазовому совмещению инверсных импульсов ig и fg. Логический блок 12 вновь открывается и выдает на второй вход второго сумматора 11 пачку импульсов fa со знаком, противоположным предшествующему. Очередные импу7п сы fg возвращаются в исходное положение. Компенсащся 1фотивоположного по знаку рассогласования осуществляется аналогично по : совпадению прямых и инверсных импульсов f9 и f g в первые полуп иоды опорной частоты fo fi/, где К - коэффициент деления втсфого делителя частоты. Поскольку частота fi3 равна скорости изме нения рассогласования Aip в дискретных в сек то точность компенсации составляющей шается. Технико-экономическая эффективность предлагаемой системы состоит в повьпиении точнос ти и быстродействия тяжелых металлорежущих станков. Формула изобретения Импульсно-фазовая следящая система, содер жащая последовательно соединенные задатчик, первый сумматор, первый делитель частоты, первый фазовый дискриминатор и привод, последовательно соединегап 1е второй делитель частоты и второй фазовый дискриминатор, причем выходы привода первый и второй датчики перемещения связаны с соответствующими входами первого и второго фазсь вых дискриминаторов, формирователь импульсов, вход которого подключен к выходу задатчнка, а выход - ко входу первого сумматора, отличающаяся тем, то, с целью повыщения точности, система второй сумматор, логический блок и блок памяти, выходы которого подключены к соответствующим входам первого и второго сумматоров, а вход - к выходу логического блока, входы которого соединены с выхода- . ми задатчика второго фазового дискриминатора и второго делителя частоты, вход которого подключен к выходу второго сумматора, соединенного соответствующим входом с выходом задатчика. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство. СССР N 180232, кл. G 05 В 5/00, 1%3. 2. Авторское свидетельство СССР N 432454, кл. G 05 В 11/01, 1972. 3. Авторское свидетельство СССР И 535550, кл. G 05 В 11/01, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий электропривод с компенсацией люфта | 1985 |

|

SU1273875A1 |

| Фазовая следящая система с комбинированным управлением | 1978 |

|

SU746423A1 |

| Следящая система программного управления станком | 1977 |

|

SU714358A1 |

| Следящий электропривод с компенсацией люфта | 1974 |

|

SU535550A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Следящая система | 1988 |

|

SU1524021A1 |

| Позиционный электропривод | 1984 |

|

SU1270859A1 |

| Электропривод | 1987 |

|

SU1434532A1 |

| Стабилизированный электропривод постоянного тока | 1986 |

|

SU1359879A1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

Авторы

Даты

1979-08-15—Публикация

1977-07-06—Подача