.Изобретение относится к радиотехнике.

Известно устройство для приема информации в системах передачи данных с решающей обратной связью, содержащее последовательно соединенные декодер, .накопитель и элемент И, а также формирователь сигнала обратной связи и блок управления, один из входов которого подключен к выходу декодера, а выход подключен к другому входу элемента И и входу формирователя сигнала обратной связи 1.

Однако в этом устройстве недостаточная пропускная способность..

Цель .изобретения - повышение пропускной способности.

Для этого в устройство для приема информации в системах передачи данных с решающей обратной связью, содержсцдее последовательно соединенные декодер, накопитель и элемент И а также формирователь сигнгша обратной связи и блок управления, один из входов которого подключен к выходу декодера, а выход подключен к другому входу элемента И и входу формировател сигнала обратной связ введен блок памяти, блок блокировки

ключ и блок сравнения, причем входы ключа соединены соответственно с выходами накопителя, блока блокировки, а также и с другим выходом блока управления, второй вход которого соединен с другим В14ходом блока блокировки, а выход ключа соещинен с входом блока памяти, выходы которого соединены с входами блока сравнения, другие входы которого соединены с соответ ;;твующими выходами накопителя, а выход соединен с входом блока блокировки.

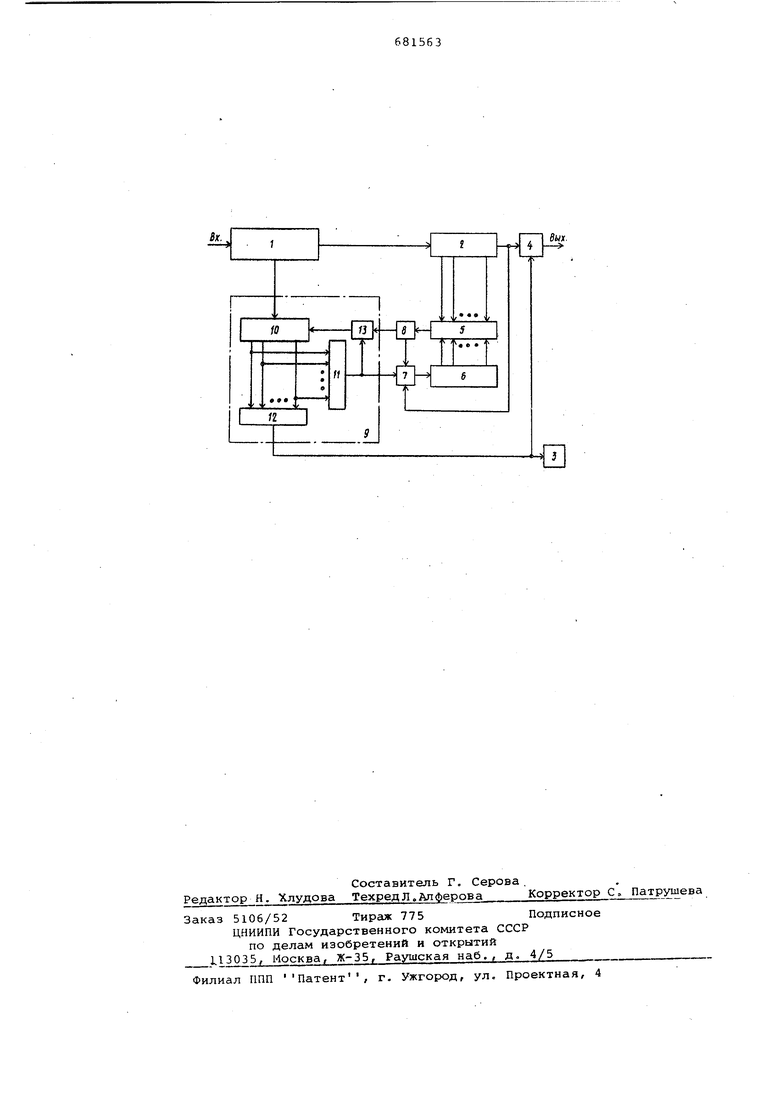

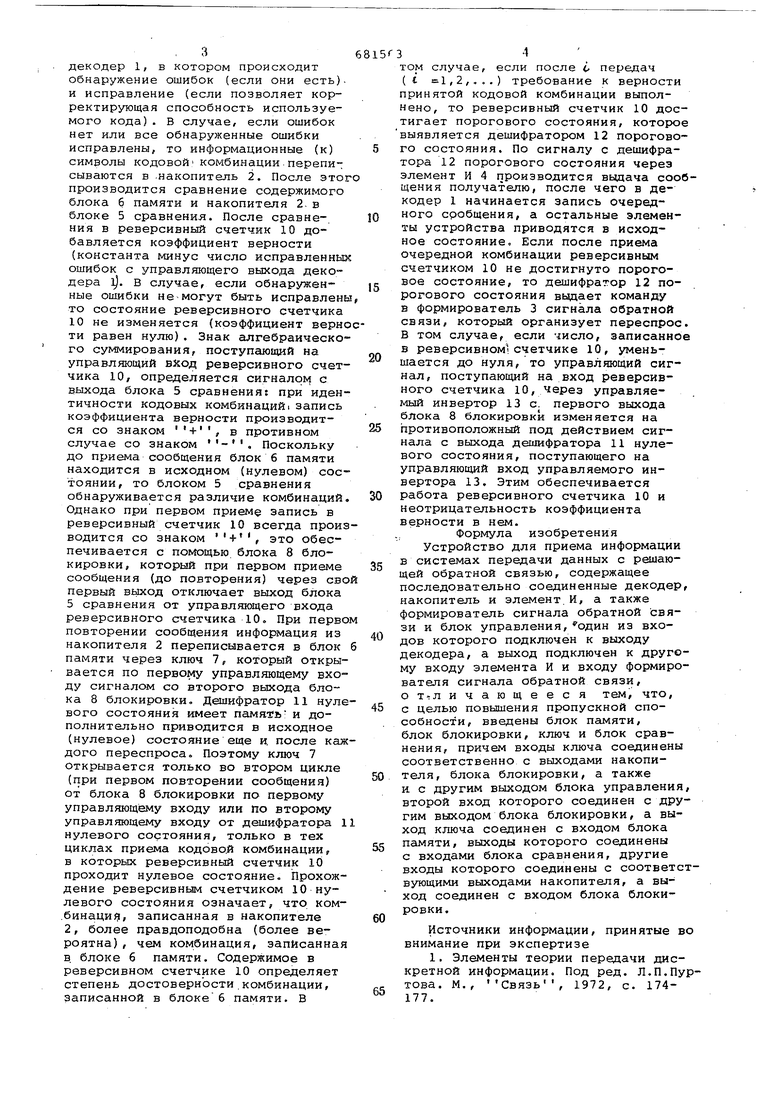

На чертеже изображена структур5ная электрическая схема предлагаемого устройства.

Устройство содержит декодер 1, накопитель 2, формирователь 3 сигнала обратной связи, элемент

0 И 4, блок 5 сравнения, блок 6 памяти, ключ 7, блок 8 блокировки, блок 9 управления, состоящий из реверсивного счетчика 10, дешифратора 11 нулевого состояния, де5шифратора 12 порогового состояния, инвертора 13.

Устройство работает следующим образом.

Двоичные п-элементные символы

0 кодовой комбинации поступают в 3 -декодер 1/ в котором происходит обнаружение ошибок (если они есть)и исправление (если позволяет корректирующая способность используемого кода). В случае, если ошибок нет или все обнаруженные ошибки исправлены, то информационные (к) символы кодовой комбинации.переписываются в .накопитель 2. После этог производится сравнение содержимого блока 6 памяти и накопителя 2- в блоке 5 сравнения. После сравне-. ния в реверсивный счетчик 10 добавляется коэффициент верности (константа минус число исправленных ошибок с управляющего выхода декодера l). в случае, если обнаруженные ошибки не-могут быть исправлены то состояние реверсивного счетчика 10 не изменяется (коэффициент верно ти равен нулю). Знак алгебраического суммирования, поступающий на управляющий вход реверсивного счетчика 10, определяется сигналом с выхода блока 5 сравнения; при идентичности кодовых комбинаций, запись коэффициента верности производится со знаком +, в противном случае со знаком , Поскольку до приема сообщения блок б памяти находится в исходном (нулевом) состоянии, то блоком 5 сравнения обнаруживается различие комбинаций Однако при первом приеме запись в реверсивный счетчик 10 всегда произ водится со знаком +, это обеспечивается с помощью блока 8 блокировки, который при первом приеме сообщения (до повторения) через сво первый вьгход отключает выход блока 5 сравнения от управл5пощего входа реверсивного счетчика 10. При перво повторении сообщения информация из накопителя 2 переписывается в блок памяти через ключ 7, который открывается по первому управляющему входу сигналом со второго выхода блока 8 блокировки. Дешифратор 11 нуле вого состояния имеет память- и дополнительно приводится в исходное (нулевое) состояние еще и, после каж дого переспроса. Поэтому ключ 7 Открывается только во втором цикле (при первом повторении сообщения) от блока 8 блокировки по первому управляющему входу или по второму управляющему входу от дешифратора нулевого состояния, только в тех циклах приема кодовой комбинации, в которых реверсивнвлй счетчик 10 проходит нулевое состояние. Прохождение реверсивным счетчиком 10 нулевого состояния означает, что ком.бинация, записанная в накопителе 2, более правдоподобна (более вероятна) , чем комбинация, записанная в. блоке 6 памяти. Содержимое в реверсивном счетчике 10 определяет степень достоверности.комбинации, записанной в блоке 6 памяти. В 4 том случае, если после 4. передач (t 1,2,,..) требование к верности принятой кодовой комбинации выполнено, то реверсивный счетчик 10 достигает порогового состояния, которое выявляется дешифратором 12 порогового состояния. По сигналу с дешифратора 12 порогового состояния через элемент И 4 производится выдача сообщения получателю, после чего в декодер 1 начинается запись очередного сробщения, а остальные элементы устройства приводятся в исходное состояние. Если после приема очередной комбинации реверсивным счетчиком 10 не достигнуто пороговое состояние, то дешифратор 12 порогового состояния вьадает команду в формирователь 3 сигнала обратной связи, который организует переспрос. В том случае, если число, записанное в реверсивном счетчике 10, уменьшается до нуля, то управляющий сигнал, поступающий на вход реверсивного счетчика 10, через управляемый инвертор 13 с. первого выхода блока 8 блокировки изменяется на противоположный под действием сигнала с выхода дешифратора 11 нулевого состояния, поступающего на управляющий вход управляемого инвертора 13. Этим обеспечивается работа реверсивного счетчика 10 и неотрицательность коэффициента верности в нем. Формула изобретения Устройство для приема информации в системах передачи данных с решающей обратной связью, содержащее последовательно соединенные декодер, накопитель и элемент.И, а также формирователь сигнала обратной связи и блок управления,один из входов которого подключен к выходу декодера, а выход подключен к другому входу элемента И и входу формирователя сигнала обратной связи, о т-гЛ ичающееся тем, что, с целью повышения пропускной способности, введены блок памяти, блок блокировки, ключ и блок сравнения, причем входы ключа соединены соответственно с выходами накопителя, блока блокировки, а также и с другим выходом блока управления, второй вход которого соединен с другим выходом блока блокировки, а выход ключа соединен с входом блока памяти, выходы которого соединены с входами блока сравнения, другие входы которого соединены с соответствующими выходами накопителя, а выход соединен с входом блока блокировки. Источники информации, принятые во внимание при экспертизе 1. Элементы теории передачи дискретной информации. Под ред. Л.П.Пуртова. М., Связь, 1972, с. 174177.

Вых.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для приема сообщений вСиСТЕМАХ пЕРЕдАчи иНфОРМАции C РЕшА-ющЕй ОбРАТНОй СВязью | 1979 |

|

SU849517A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1601754A1 |

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

Авторы

Даты

1979-08-25—Публикация

1978-03-13—Подача