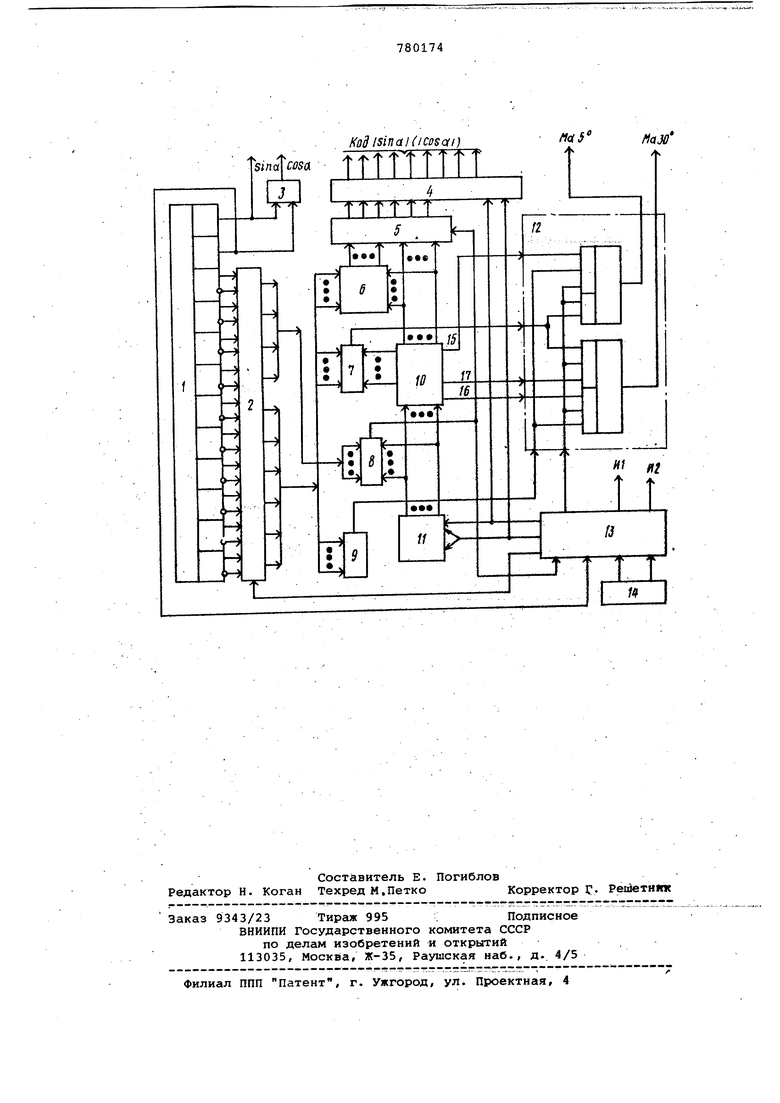

780174 блока формирования меток, выходы бло ка управления соединены также с дополнительными входами накапливакяцего сумматора и блока формирования меток выход второго цифрового компаратора соединен с дополнительными входами соответственно выходного коммутатора кодов и блока управления. На чертеже представлена структурная электрическая схема предложенного преобразователя. Преобразователь содержит датчик 1 прямого и инвертированного кодов, коммутатор 2 кодов, сумматор 3, нака ливакхций сумматор 4, выходной коммутатор 5 кодов, множительный блок б, цифровые компараторы 7 и 8, элемент ИЛИ-НЕ 9, запоминакидий блок 10,счетчик 11, блок 12 формированияметок, блок 13 управления и синхронизатор 1 Преобразователь работает следующим образом. На выходах первой группы запомина ющего блока .10 вырабатывается шестиразрядный код углового коэффициента KJ с весом младшего разряда 2 . На выходах второй группы запоминающего блока 10 вырабатывается, шестиразрядный код угла р & О (вес младшего ра ряда этого кода равен 2S радиан) такой, который дополняет четырехразрядный код на адресных входах запоми нающего блока 10 до кода угла, кото. рому соответствует метка . На выходе 15 запоминающего блока 10 вырабатывается признак метки 5°, (п., 5) которому соответствует комбинация 0000 или 1000 кода на адресных входах запоминающего блока 10. На выходе 16 запоминающего блока 10 вырабатывается признак метки 30® (П.,30°), которому соответствует ком бинация 0000 кода на адресных входах этого блока. На выходе 17 блока 10 вырабатывается с учетом признака П,, 30° призна метки 30° (П.,30°) таким образом, ес ли четырехразрядному коду на адресных входах блока .0 соответствует ме ка 30, то П, ЗО 1, а если нет, то П 30° 0. БЛО.К 13 управления содержит три триггера и.несколько логических комбинационных элементов. Преобразователь по 12-ти разрядно му коду угла d циклически вырабатыва ет 10-ти разрядные коды sinolH cosdl импульсы масштабных угловых меток .SCMitSTi и 30°(MA3Cf), а также формирует импульс конца определения кода sin А и импульс конца определения кода cos dC и выдает эту информацию на выходы. . Старшие разряды у кодов siпсШ cosi знаковые и определяются по двум старшим разрядам датчика 1. Поэтому 12-ый разряд датчика 1 является знаковым разрядом кода , а знаковый разряд кода cosА вырабатывается сумматором 3 как сумма по мбдулю два логических значений двух старших разрядов датчика 1. Определение кодов чисел (и /соsd.1 осуществляется методом кусочнолинейной аппроксимации и испЪльзованием тригонометрических формул приведения. Аппроксимация функций производится в угле от нуля до 90°, который разбит на 16 равных участков, т.е. вычисление функции 151пЛ|или 1со5оЧ производится по приведенному углу Р или , 10-ти разрядный код которого снимается с выходов коммутатора 2 кодов, где: .а приведенный угол. величина которого определяется прямь1м кодом 10-ти младших разрядов датчик а 1, .,,-)« .., . ТИа-- - приведенный угол, величина которого определяется инверсным кодом 10- младших разрядов датчика 1, , 2 - соответственно разрядный и весовой коэффициенты 1-го разряда хода датчика 1. Для преобраз.ования приведенный угол ft (В) разделен на две части: fcj или 6 - управляющую часть, представленную кодом четырех старших разрядов коммутатора 2 кодов, аппр и «ппР - аппроксимирующую часть, представленную кодом шести младших разрядов коммутатора 2 кодов. При этом в устройстве с помощью блока 13 управления коды Isindl и ICOSAI определяются последовательно в Кс1ждом цикле преобразования, состоящем из двух периодов Т1 и Т2. в течение периода Т1 определяется код Isinil, а в течение периода Т2 код Icos ctl. Для этого блок 13 по значению 11--ГО разряда датчика1 вырабатывает на выходе для коммутатора 2 кодов управляющий сигнал таким образом,что если а О,то в течение периода Т с коммутатора 2 снимается код В , а в течение периода Т - код В и наоборот, если а 1. Перед началом цикла преобразования в сумматоре 4 и счётчике 11 содержатся результаты предьщущего цикла преобразования. Для определенности будем считать, что начиная с этого момента и до окончания рассматриваемого цикла преобразования код не изменяется, а а О, т.е. перед началом цикла преобразования с .выходов коммутатора 2 кодов снимается код угла Ъ . Цикл преобразования начинается с приходом от синхронизатора 14 на блок 13 управления старт-импульса.По этому импульсу блок ДЗ вырабатывает сигнал установки в О сумматора 4 и счетчика 11, а затем вырабатывает се рию из N1 импульсов, которые поступа ют на тактовый вход сумматора 4 и счетный вход счетчика 11. Причем N1 j + 1, где: , - номер участка ап1г7проксимации, определяемый кодом Bj , а j может -принимать значения из ря да 0,1,....:.,,15. КЪд 8.J на компараторе 8 сравнива ется с текущим кодом в (t) счетчика 11, поступающим на адресные входы блока 10. В результате этого компаратор 8 вырабатывает логический сигнал F если (t) и F 1, если Ь: в (t) . Сигнал F поступает на управляющи вход выходного коммутатора 2 кодов и на один из входов блоков 13 управления. При этом, если F О, то входы слагаемого сумматора 4 подключены к выходам первой группы блоков 10, на который последовательно будет выраба тываться шестиразрядный код углового коэффициента Кц, К ,. .. ,К ,... ,К. Под К понимается код числа (sin 6 + S i п ) ) , вес младшего разряда которо го равен . Так как преобразователь выполнен на элементной базе, триггера которой переключаются в момент после оконча. ния импульсов на их синхронизирующих (счетных) входах, то после окончания j-ro импульса серии N1 в сумматоре 4 будет содержаться код числа s i п Bj, а сигнёш F будет равен 1. По сигналу Г 1 KONwyraTop 5 подключает на входы слагаемого сумма тора 4 выходы множительного блока 6. На первую группу входов множительного блока 6 поступает код Йдппр на входы второго - код . Поэтому на входы слагаемого сумма тора 4 будет поступать код числа oinnp 3 Под ЬОППР выражении 6о,пп« - K-j пони мается число между О и 1, опреде ляемое шестью младшими разрядами кода 8 . После окончания последнего импульса серии N1. с выходов сумматора 4 будет сниматься код числа .j + Ьс,п„.- К.) г. , ,,,. Так как при F 1 Ь e(t), то в этот момент на адресные входы блок 10 поступает код угла bj . Следовательно, при F i - на выходе 15 блока 10 вырабатывается признак метки 5 () кот рому соответствует комбинация 0000 или 1000 кода 6 , -на выходе 16блока 10 вырабатывается признак метки 30 (), ;которому соответствует комбинация 0000 кода B.J , -на выходе 17 блока 10 вырабатывается с учетом П.,30° признак метки 30° (П,, 30). -на второй группе выходов блока 10 вырабатывается код угла .О такой величины, который дополняет код угла Б, до кода угла, которому соответствует метка 5®. КодБ сравнивается с кодом компаратором 7, на выходе которого вырабатывается логический сигнал Fa. О, если Ь, и F,j 1, если - «ппр КодВаппр поступает на входы элемента ИЛИ-НЕ 9,. на выходе которого вырабатывается логический сигнал F 1 , если Ьаппр О, и Fj О, если ВОЩПР О. .Логические сигналы , П 30 , 30°, F и FJ поступают на входы блока 12 формирования меток. Так как с выходов коммутатора 2 кодов снимается код 6 , то по сигналу F 1 и очереднсму тактовому импульсу блок 13 управления генерирует импульсы опроса. По импульсу опроса, совпадгиощему с последним импульсом серии N1, блок 12формирования меток вырабатывает импульсы метки 5 {MdS), если 5°. FI VFj . 1 и вырабатывает импульсы метки 30° (Md, 30) ,. если П., )jV F,- 30° 1После этого блок 12 управления подключает на входы коммутатора 2 кодов код В и генерирует на выход устройства импульс окончания периода Т преобразования, по которому с в ыходов устройства снимается код slnd.. На этом период Т заключается и начинается период Т, , в котором блок 13управления вновь генерирует сигнал установки в нуль сумматора 4 и счетчика 11, а затем вырабатывает серию из N2 импульсов, поступающих на тактовый вход сумматора 4 и счетный вход счетчика 11. Примем N J + 1 , . где .2 номер участка аппрок )7 симации, определяемый кодом Bj . Так как в периоде Т вычисление /соsd)производится по приведенному углу В , то по сигналу F 1 блок 13 управления импульс опроса не вырабатывает. После окончания последнего импульса серии N2 по управляющему сигналу с блока 13 управления коммутатор 2 кодов подключает на выходы код угла Ь .. Затем блок 13 управления генерирует импульс конца преобразования, ПО которому с выходов устройства может сниматься код числа cosd.На этом цикл вычислений заканчивается а следующий цикл начнется только с прихЬдом на блок 13 управления от синхронизатора 14 очередного старт-импульса. Таким образом, импульсы меток MdS и MdLSO будут вырабатываться по послед нему импульсу серии N1, если а О, или по последнему импульсу серии N2, если а 1,а длительность цикла преобразования будет величиной постоянной и определяется выражением (), где t-., - период частоты следования тактовых импульсов синхрони затора 14. Следовательно, в общем случае дли тельность времени цикла преобразования составляет разрядность датчика 1, число участков аппроксима ции, число младших разрядов да чика 1, по которым произв дится аппроксимация функции на J-M участке. Формула изобретения Цифровой синусно-косинусный преоб разователь, содержащий датчик прямог и инвертированного кодов, к соответс вующим выходам которого подключен ко мутатор кодов и сумматор/ запоминающий блок, адресные входы которого со динены с выходами счетчика, синхрони затор, выходы КОТОРОГО соединены с блоком Управления, выход старшего ра ряда датчика прямого и инвертированного кодов соединен с соответствующим входом блока управления , один из выходов которого соединен с дополнительным входом коммутатора кодов, а два других - с входами счетчика, первая группа выходов запоминающего блока соединена с первой группой входов множительного блока и выходного коммутатора кодов, вторая группа входов которого соединена с группой выходов множительного блока, о т л и ч а ющ и и с я тем, что, с целью увеличения быстродействия, введены накапливающий сумматор, два цифровых компаратора, элемент ИЛИ-НЕ и блок формирования меток, при этом входы элемента ИЛИ-НЕ соединены с второй группой входов множительного блока, с входами первого кода первого цифрового компаратора и с выходами К младших разрядов коммутатора кодов, остальные выходы которого соединены с входами первого кода второго компаратора,входы второго кода которот-о соединены с выходами счетчика и адресными входами запоминающего блока, вторая группа выходов которого соединена с входами второго кода первого цифрового компаратора, входы слагаемого накапливающего сумматора соединены с выходами выходного коммутатора кодов, выходы первого цифрового компаратора элемента ИЛИ-НЕ и дополнительные выходы запоминающего блока соединены с соответствующими входами блока формирования меток, выходы блока управления соединены также с дополнительными входами накапливающего сумматора и блока формирования меток, выход второго цифрового компаратора соединен с дополнительными входами соответственно выходного коммутатора кодов и блока управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке 2440317,кл Н 03 К 5/156, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой синусно-косинусный преобразователь | 1978 |

|

SU800923A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Функциональный преобразователь кода угла и дальности | 1981 |

|

SU1008734A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Формирователь импульсов углового положения коленчатого вала | 1981 |

|

SU1030823A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

Авторы

Даты

1980-11-15—Публикация

1977-09-12—Подача