(54) МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В УГЛОВОЕ ПЕРЕМЕЩЕНИЕ ВАЛОВ

защиты соединен с первым входом формирователя последовательности импульсов, с выходом дешифратора и с первым входом элемента И, ко второму входу которого подключен второй выход число-импульсного пре образователя. Выход блока защиты соединен со вторым входом формирователя управляющих сигналов, третий вход которого соединен с выходом блока контроля и с пятым входом блока памяти. Первый выход формирователя управляющих сигналов подключен ко второму входу формирователя последовательности импульсов, а его второй выход подключен к формирователю сигнала отказа. Первый вход блока контроля соединен с выходом триггера, второй - с выходом элемента И, а третий - со вторым входом число-импульсного преобразователя и с вь1ходом формирователя сигналов обратной связи.

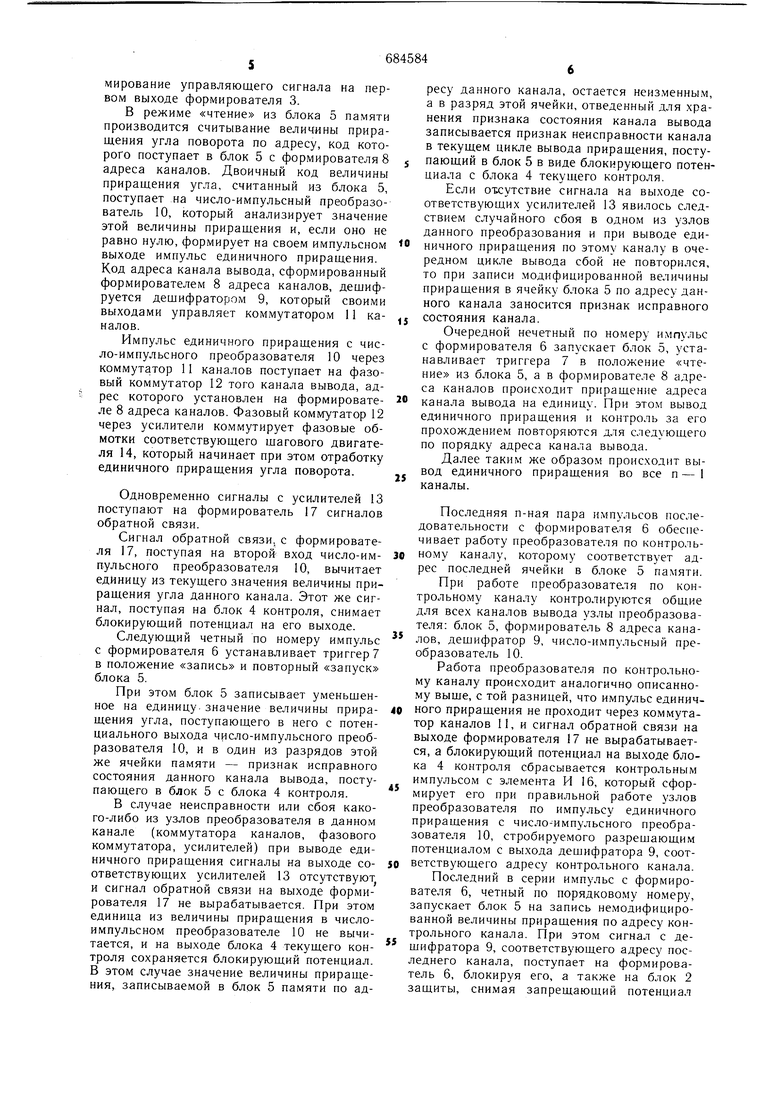

На фиг. 1 приведена структурная электрическая схема многоканального преобразователя кода в угловое перемещение валов; на фиг. 2 изображена временная диаграмма работы устройства.

Преобразователь содержит генератор 1 тактовых импульсов, соединенный с первыми входами блока 2 защиты и формирователя 3 управляющих сигналов, второй вход которого соединен с выходом блока 2 защиты, а третий - с выходом блока 4 контроля и с первым входом блока 5 памяти, связанного соответственно вторым, третьим и четвертым входами с выходами последовательно соединенных формирователя 6 последовательности импульсов, триггера 7 и формирователя 8 адреса каналов, выход которого также соединен со входом дещифратора 9. Пятый вход и выход блока 5 памяти соответственно подключены к потенциальным выходу и входу числоимпульсного преобразователя 10, импульсный выход которого через коммутатор 11 каналов, фазовые коммутаторы 12 и усилители 13 связан с фазовыми обмотками шаговых двигателей 14. Выход дещифратора 9 подключен к потенциальному входу коммутатора 11 каналов, ко второму входу блока 2 защиты и к первому входу формирователя 6 последовательности импульсов, второй вход которого соединен с первым выходом формирователя 3 управляющих сигналов, соединенного вторым выходом со входом формирователя 15 сигналов отказа.

Выход триггера 7 подключен к первому входу блока 4 контроля, второй вход которого соединен с выходом элемента И 16, связанного входами с выходом дещифратора 9 и с импульсным выходом число-импульсного преобразователя 10, а третий вход - с выходом формирователя 17 сигнала обратной связи, соединенного входами с выходами усилителей 13, причем выход формирователя 17 сигнала обратной связи подключен также ко второму входу числоимпульсного преобразователя 10. Соответствующие выходы и входы формирователя 15 сигнала отказа и блока 4 контроля подключены к управляющей системе (УС).

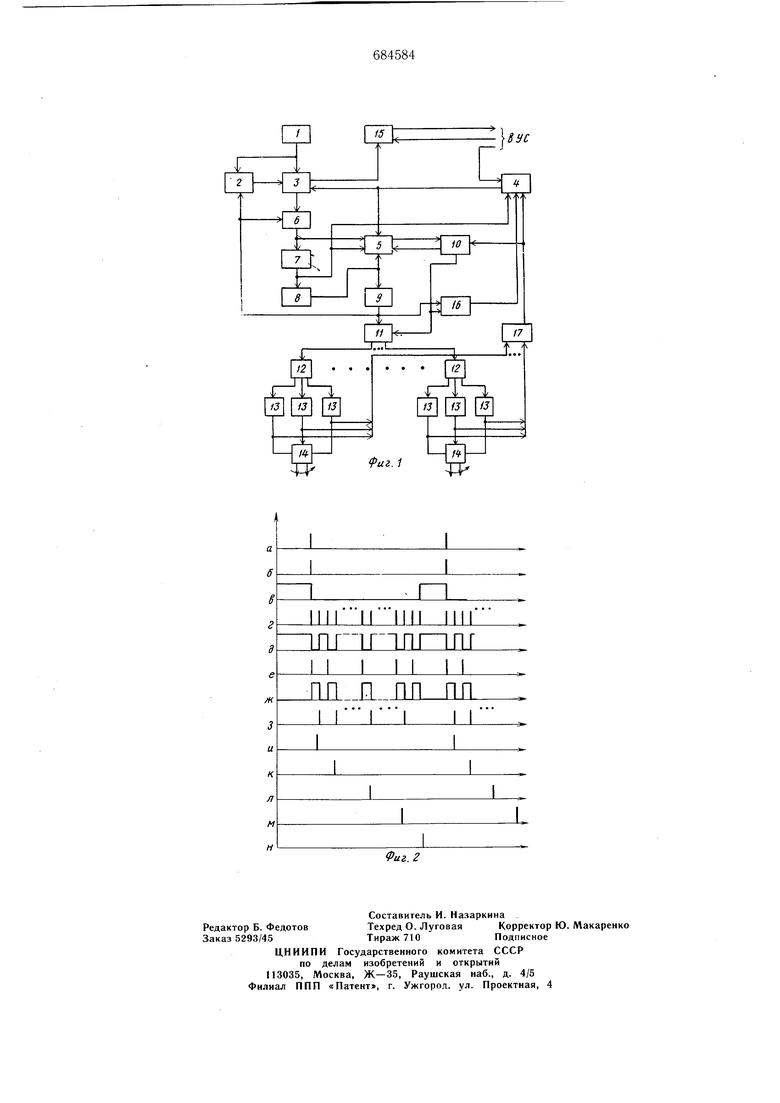

На фиг. 2 обозначены:

а - сигналы на выходе генератора 1 тактовых импульсов; б - сигналы на выходе формирователя 3 управляющих сигналов; в - сигналы на выходе блока 2 защиты; г - сигналы на выходе формирователя 6

последовательности импульсов; д - сигналы на единичном выходе триггера 7; е - сигналы на импульсном выходе число-импульсного преобразователя 10; ж - сигналы на выходе блока 4 контроля; з - сигналы на выходе формирователя 16 сигналов обратной связи; и - сигналы на первом выходе коммутатора 11 каналов; к - сигналы на втором выходе коммутатора 11 каналов; л - сигналы на i-том выходе коммутатора 11 каналов; м - сигналы на п-1

выходе коммутатора 11 каналов; н - сигналы на выходе элемента И 16 (п-ный контрольный канал).

Преобразователь работает следующим образом.

Под воздействием тактовых импульсов, формируемых генератором 1 с частотой, равной предельно допустимой частоте управляющих импульсов щаговых двигателей 14, запускается формирователь 3 управляющих сигналов. На первом его выходе при наличии разрещающих потенциалов на втором и третьем входах формируется управляющий сигнал, запускающий формирователь 6 последовательности импульсов. По сигналу генератора 1 тактовых импульсов запускается также блик 2 защиты, на выходе которого вырабатывается запрещающий потенциал, блокирующий повторный запуск формирователя 3 управляющих сигналов.

При запуске формирователя 6 на его выходе вырабатывается последовательность

импульсов. Количество импульсов в каждой последовательности равно 2п, где п - число каналов вывода преобразователя, из них п-I каналы обслуживают исполнительные щаговые двигатели; 14, а п-ный канал

является контрольным.

Импульсы формирователя 6 поступают на блок 5 памяти и на триггер 7, устанавливая его поочередно в положения, соответствующие режимам работы блока 5 -

«чтение или «запись. Каждый нечетный по порядковому номеру импульс последовательности устанавливает триггер в положение, задающее режим работы блока 5 «чтение, каждый четный - в положение, задающее режим «запись.

Сигнал с триггера 7 при установке его в положение «чтение запускает блок 4 контроля, на в э1ходе которого вырабатывается потенциал, блокирующий повторное формирование управляющего сигнала на первом выходе формирователя 3.

В режиме «чтение из блока 5 памяти производится считывание величины приращения угла поворота по адресу, код которого поступает в блок 5 с формирователя 8 адреса каналов. Двоичный код величины приращения угла, считанный из блока 5, поступает на число-импульсный преобразователь 10, который анализирует значение этой величины приращения и, если оно не равно нулю, формирует на своем импульсном выходе импульс единичного приращения. Код адреса канала вывода, сформированный формирователем 8 адреса каналов, дещифруется дещифратором 9, который своими выходами управляет коммутатором 11 каналов.

Импульс единичного приращения с число-импульсного преобразователя 10 через коммутатор 11 каналов поступает на фазовый коммутатор 12 того канала вывода, адрес которого установлен на формирователе 8 адреса каналов. Фазовый коммутатор 12 через усилители коммутирует фазовые обмотки соответствующего щагового двигателя 14, который начинает при этом отработку единичного приращения угла поворота.

Одновременно сигналы с усилителей 13 поступают на формирователь 17 сигналов обратной связи.

Сигнал обратной связи, с формирователя 17, поступая на второй вход число-импульсного преобразователя 10, вычитает единицу из текущего значения величины приращения угла данного канала. Этот же сигнал, поступая на блок 4 контроля, снимает блокирующий потенциал на его выходе.

Следующий четный по номеру импульс с формирователя 6 устанавливает триггер 7 в положение «запись и повторный «запуск блока 5.

При этом блок 5 записывает уменьщенное на единицу.значение величины приращения угла, поступающего в него с потенциального выхода число-импульсного преобразователя 10, и в один из разрядов этой же ячейки памяти - признак исправного состояния данного канала вывода, поступающего в блок 5 с блока 4 контроля.

В случае неисправности или сбоя какого-либо из узлов преобразователя в данном канале (коммутатора каналов, фазового коммутатора, усилителей) при выводе единичного приращения сигналы на выходе соответствующих усилителей 13 отсутствуют и сигнал обратной связи на выходе формирователя 17 не вырабатывается. При этом единица из величины приращения в числоимпульсном преобразователе 10 не вычитается, и на выходе блока 4 текущего контроля сохраняется блокирующий потенциал. В этом случае значение величины приращения, записываемой в блок 5 памяти по адресу данного канала, остается неизменным, а в разряд этой ячейки, отведенный для хранения признака состояния канала вывода записывается признак неисправности канала в текущем цикле вывода приращения, поступающий в блок 5 в виде блокирующего потенциала с блока 4 текущего контроля.

Если отсутствие сигнала на выходе соответствующих усилителей 13 явилось следствием случайного сбоя в одном из узлов данного преобразования и при выводе единичного приращения по этому каналу в очередном цикле вывода сбой не повторился, то при записи модифицированной величины приращения в ячейку блока 5 по адресу данного канала заносится признак исправного

СОСТОЯНИЯ канала.

Очередной нечетный по номеру импульс с формирователя 6 запускает блок 5, устанавливает триггера 7 в положение «чтение из блока 5, а в формирователе 8 адреса каналов происходит приращение адреса канала вывода на единицу. При этом вывод единичного приращения и контроль за его прохождением повторяются для следующего по порядку адреса канала вывода.

Далее таким же образом происходит вывод единичного приращения во все п - 1

каналы.

Последняя п-ная пара импульсов последовательности с формирователя 6 обеспечивает работу преобразователя по контрольному каналу, которому соответствует адрес последней ячейки в блоке 5 памяти. При работе преобразователя по контрольному каналу контролируются общие для всех каналов вывода узлы преобразователя: блок 5, формирователь 8 адреса каналов, дешифратор 9, число-импульсный преобразователь 10.

Работа преобразователя по контрольному каналу происходит аналогично описанному выще, с той разницей, что импульс единичного приращения не проходит через коммутатор каналов II, и сигнал обратной связи на выходе формирователя 17 не вырабатывается, а блокирующий потенциал на выходе блока 4 контроля сбрасывается контрольным импульсом с элемента И 16, который сформирует его при правильной работе узлов преобразователя по импульсу единичного приращения с число-импульсного преобразователя 10, стробируемого разрешающим потенциало.м с выхода дешифратора 9, соответствующего адресу контрольного канала. Последний в серии импульс с формирователя 6, четный по порядковому номеру, запускает блок 5 на запись немодифицированной величины приращения по адресу контрольного канала. При этом сигнал с дешифратора 9, соответствующего адресу последнего канала, поступает на формирователь 6, блокируя его, а также на блок 2 защиты, снимая запрещающий потенциал

со ихода формирователя 3. Следующая серия импульсов на выходе формирователя 6 формируется с приходом управляюыдего сигнала формирователя 3.

Таким образом, по каждому управляюпюму сигналу формирователя 3 происходит вывод единичного приращения последовательно во все каналы и контроль за его прохождением до фазовых обмоток шаговых двигателей 14.

В случае неисправности какого-либо из узлов преобразователя: блока 5 памяти, формирователя 8 адреса каналов, дешифратора 9, число-импульсного преобразователя 10, при работе контрольного канала преобразователя контрольный импульс на выходе элемента И 16 не вырабатывается, и на выходе блока 4 текушего контроля сохраняется блокируюший потенциал. В этом случае с приходом очередного тактового импульса генератора 1 формирователь 6 не запускается,а на втором выходе формирователя 3 управляюш.их сигналов формируется сигнал, запускаюший формирователь 15 сигнала отказа. При этом на выходе формирователя 15 формируется сигнал отказа, поступающий в управляющую систему и сигнализируюший о неисправности преобразователя. Сброс формирователя 15 и блока 4 текушего контроля 4 происходит по сигналам из управляющей системы.

Сбои в работе преобразователя могут возникать также в результате повышения частоты тактовых импульсов генератора 1 или понижения частоты импульсов формирователя 6 за допустимые пределы. В этом случае время, необходимое для вывода единичных приращений во все каналы вывода, может превысить период следования импульсов тактового генератора 1. Защита от такого рода сбоев выполняется блоком 2 загциты, который блокирует запуск формирователя 3 управляюших сигналов до тех пор, пока не закончится цикл вывода единичного прирашения в последний канал, и сигнал с дешифратора 9, соответствующий адресу последующего канала, не снимает блокируюший потенциал на выходе блока 2 защиты.

Формула изобретения

Многоканальный преобразователь кода в угловое перемешение валов, содержаший

генератор тактовых импульсов, формирователь последовательности импульсов, выход которого соединен с входом триггера и с первым входом блока памяти, ко второму входу которого подключены выход триггера и вход формирователя адреса кода, выход которого соединен с третьим входом блока памяти и со входом дешифратора, четвертый вход блока памяти соединен с первым выходом число-импульсного преобразователя, второй выход которого соединен с первым входом коммутатора каналов, ко второму входу которого подключен выход дешифратора, выход блока памяти соединен с первым входом число-импульсного преобразователя, выходы коммутатора каналов через фазовые коммутаторы и усилители подключены к шаговым двигателям и ко входам формирователя сигналов обратной связи, отличающийся тем, что, с целью повышения надежности устройства, в него введены формирователь управляюших сигналов, формирователь сигналаотказа, блок контроля, элемент И и блок защиты, один вход которого соединен с генератором тактовых импульсов и с первым входом формирователя управляющих сигналов, другой вход блока защиты соединен с первым входом формирователя последовательности импульсов, с выходом д.ешифратора и с первым входом элемента И, ко второму входу которого подключен второй выход число-импульсного преобразователя, выход блока защиты соединен

0 со вторым входом формирователя управляющих сигналов, третий вход которого соедиас с выходом блока контроля и с пятым входом блока памяти, первый выход формирователя управляюших сигналов подключен ко второму входу формирователя последовательности импульсов, а его второй выход подключен к формирователю сигнала отказа, первый вход блока контроля соединен с выходом триггера, второй вход - с выходом элемента И, а третий вход блока контроля

0 соединен со вторым входом число-импульсного преобразователя и с выходом формирователя сигналов обратной связи.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 463134, G 08 С 19/28, 1973.

2.Авторское свидетельство СССР № 574805, G 08 С 11/00, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь кода в угловое перемещение | 1975 |

|

SU547805A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1800380A1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1798719A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

Авторы

Даты

1979-09-05—Публикация

1977-04-06—Подача