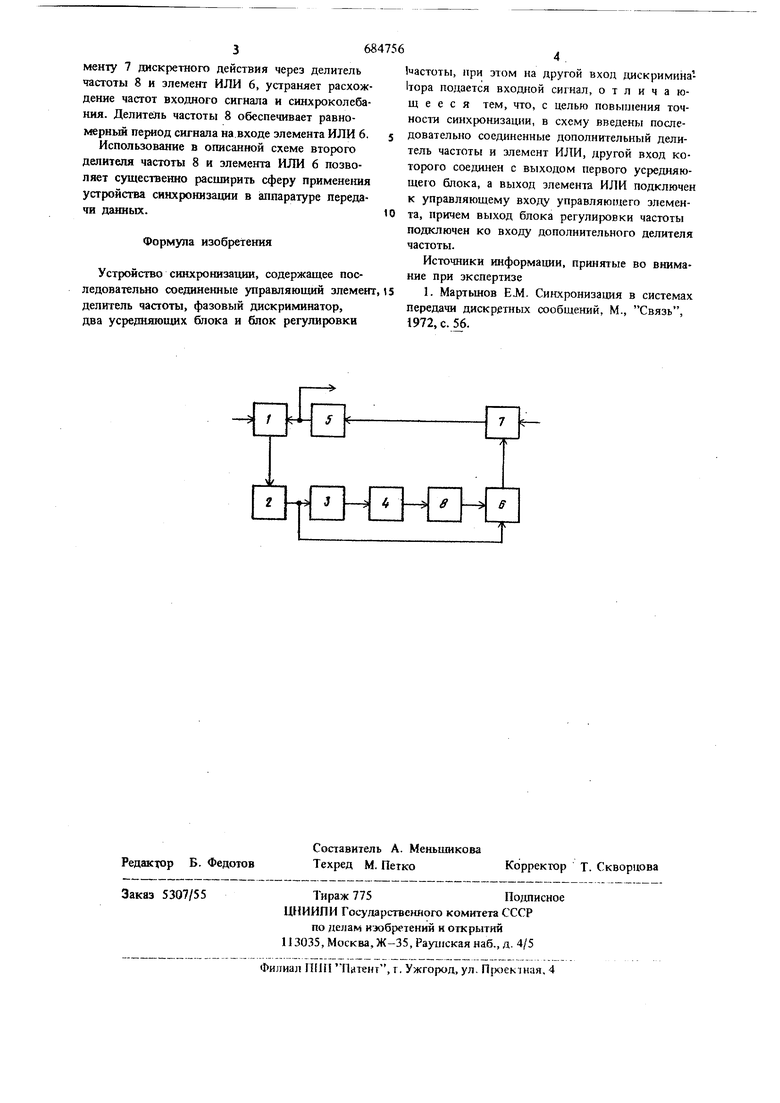

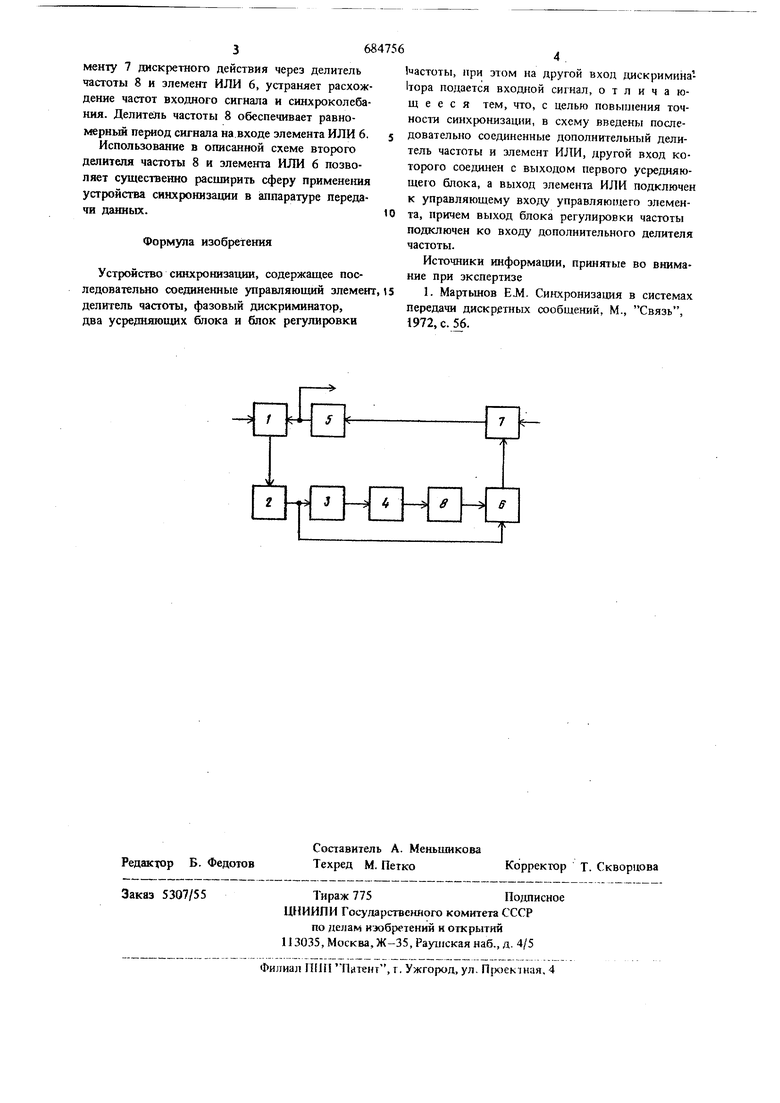

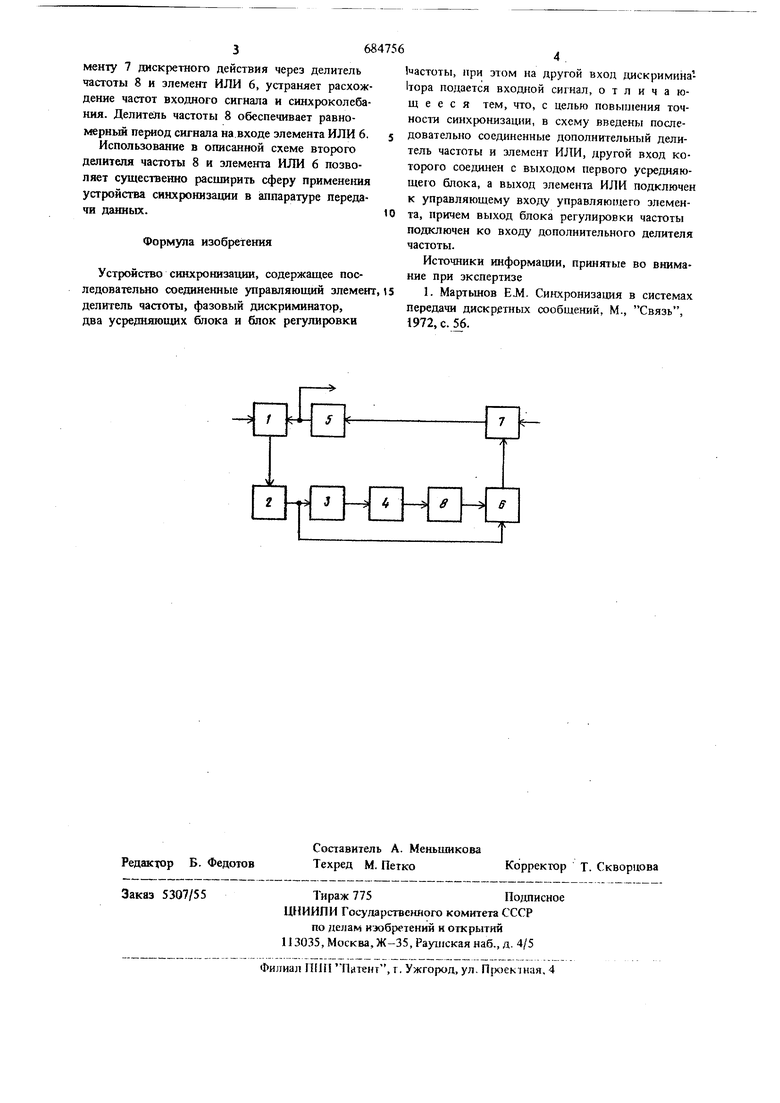

Изобретете относится к радиотехнике, может использоваться в радиотехнических устройствах jaanHMHoro назначения. Известно .устройство синхронизации, содержащее последовательно соединеш1ые управляющий элемент, делитель частоты, фазовый дискри минатор, два усрещшгощих блока и блок регулировки частоты; при этом на другой вход фазового дискриминатора подается входной сигнал 1. Орнако известное устройство не позволяет получить высокой точности подстройки синхроколебания. Цель изобретения - повышение точности синх ронизации., Для этого в устройство синхронизации, содер жащее последовательно соединенные зшравляющий элемент, делитель частоты, фазовый дискри минатор, два усредняющих блока и блок регулировки частоты, причем на другой вход фазов го дискриминатора подается входной сигнал, введены последовательно соединегшые дополнительный делитель частоты и элемент ИЛИ, другой вход которого соединен с выходом первого усредняющего блока, а выход элемента ИЛИ подключен к управляющему входу управляющего элемента, причем выход блока регулировки частоты подключен ко входу дополнительного делителя частоты. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство синхронизации содержит фазовый дискриминатор 1, усредняюпше блоки 2 и 3, блок регулировки частоты 4, делитель частоты 5, элемент ИЛИ 6, управляющий элемент 7, делитель частоты 8. Устройство работает следующим образом. Усредне1шый знак рассогласования фазы входного сигнала и вьщеленного синхроколебания поступает с фазового дискриминатора 1 через усредняющий блок 2 и элемент ИЛИ 6 на управляющий элемент 7 дискретного действия, чем обеспечивается точное отслеживание изменения фазы входного сигнала. С другой стороны усредненный знак рассогласования после дополнительного усре,анеш)я в блоке 3 управляет работой блока регули1ювки частоты 4. Блок 4 подключенный к управляющему злементу 7 дискретного действия через делитель частоты 8 и элемент ИЛИ 6, устраняет расхождение частот входного сигнала и синхроколебания. Делитель частоты 8 обеспечивает равномерньш период сигнала на входе элемента ИЛИ 6. Использование в описанной схеме второго деяятеля частоты 8 и элемента ИЛИ 6 позволяет существенно расширить сферу применения устройства синхронизации в аппаратуре передачи данных. Формула изобретения Устройство синхронизащш, содержащее последовательно соединенные управляющий злемен делитель частоты, фазовый дискриминатор, два усредняющих блока и блок регулировки 1 астоты, при этом на другой вход дискримина1тора подается входной сигнал, отличающееся тем, что, с дельго повышения точности синхронизадии, в схему введены последовательно соединенные дополнительный делитель частоты и злемент ИЛИ, другой вход которого соединен с выходом первого усредняющею блока, а выход элемен1а ИЛИ подключен к управляющему входу управляющего элемента, причем выход блока регулировки частоты подключен ко входу дополнительного делителя частоты. Источники информации, приня1ые во внимание при экспертизе 1. Мартьшов ЕМ. Синхронизация в системах передачи дискретных сообщений, М., Связь, {912, с. 56.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU856028A2 |

| Устройство синхронизации с дискретным управлением | 1974 |

|

SU562935A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| Устройство для тактовой синхронизации и регенерации дискретных сигналов | 1975 |

|

SU536610A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1415446A1 |

| Устройство для тактовой синхронизации | 1973 |

|

SU489242A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1984 |

|

SU1215185A1 |

| Устройство синхронизации | 1979 |

|

SU873440A1 |

-5

Авторы

Даты

1979-09-05—Публикация

1977-05-03—Подача