Изобретение о 1 Носится к электросвязи и может быть использовано в системах передачи дискретной информации для обеспечения тактовой синхро- низации приемной части аппаратуры.

Цель изобретения - повышение точности синхронизации в условиях помех без снижения быстродействия.

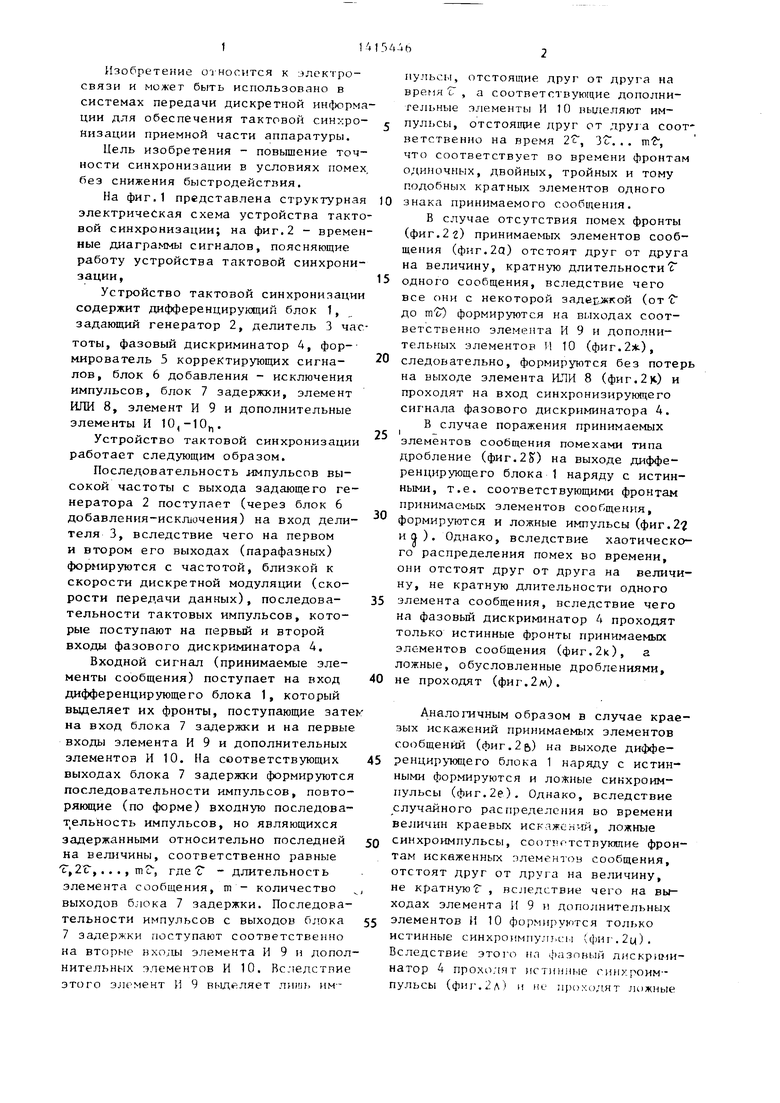

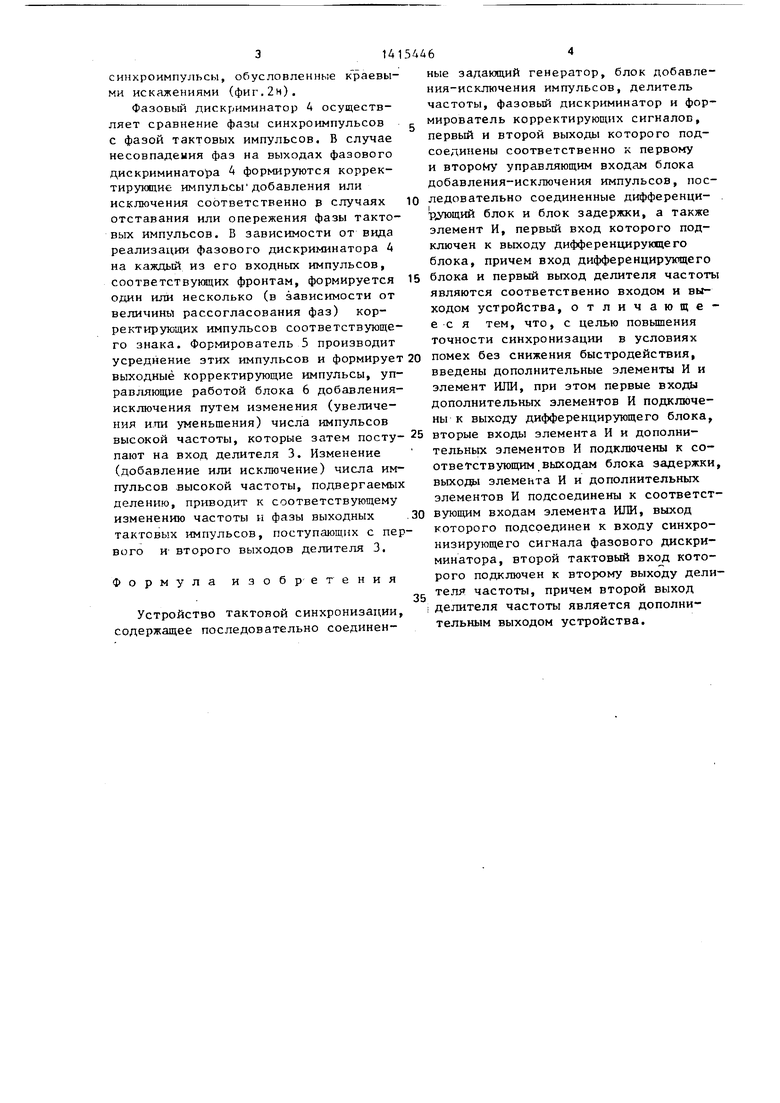

На фиг.1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг.2 - временные диаграммы сигналов, поясняющие работу устройства тактовой синхронизации,

Устройство тактовой синхронизации содержит дифференцирующий блок 1, задающий генератор 2, делитель 3 частоты, фазовый дискриминатор 4, формирователь 5 корректирующих сигна- лов, блок 6 добавления - исключения импульсов, блок 7 задержки, элемент ИЛИ 8, элемент И 9 и дополнительные элементы И 10,-10.

Устройство тактовой синхронизации работает следующим образом.

Последовательность 1мпульсов высокой частоты с выхода задающего генератора 2 поступает (через блок 6 добавления-исключения) на вход дели- теля 3, вследствие чего на первом и втором его выходах (парафазных) формируются с частотой, близкой к скорости дискретной модуляг и (скорости передачи данных), последова- тельности тактовых импульсов, которые поступают на первый и второй входы фазового дискриминатора 4.

Входной сигнал (принимаемые элементы сообщения) поступает на вход дифференцирующего блока 1, который выделяет их фронты, поступающие зате на вход блока 7 задержки и на первые входы элемента И 9 и дополнительных элементов И 10. На соответствующих выходах блока 7 задержки формируются последовательности импульсов, повторяющие (по форме) входную последова- т ельность импульсов, но являющихся задержанными относительно последней на величины, соответственно равные Г, 2Г,. . . , m с, где Т - длительность элемента сообщения, m - количество выходов блока 7 задержки. Последовательности импульсов с выходов блока 7 задержки поступают соответственно на вторые входы элемента И 9 и дополнительных элементов И 10. Вследствие этого элемент И 9 выделяет лИ1иь импульсы, отстоящие друг от друга на время Г , а соответствующие дополни- rejHjHbie элементы И 10 пьщеляют импульсы, отстоящие друг от друт-а соот ветственно на время 2 ЗсГ. . . т, что соответствует во времени фронтам одиночных, двойных, тройных и тому подобных кратных элементов одного знака принимаемого сообщения.

В случае отсутствия помех фронты (фиг.22) принимаемых элементов сообщения (фиг.2а) отстоят друг от друга на величину, кратную длительности одного сообщения, вследствие чего все они с некоторой задесл кой ( до т бО формируются на выходах соответственно элемента И 9 и дополнительных элементов И Ю (фиг.2), следовательно, формируются без потер на выходе элемента ИЛИ 8 (фиг.2к) и проходят на вход синхронизирующего сигнала фазового дискриминатора 4.

В случае поражения принимаемых элементов сообщения помехами типа дробление (фиг.2В ) на выходе дифференцирующего блока 1 наряду с истинными, т.е. соответствующими фронтам принимаемых элементов сообщения, формируются и ложные импульсы (фиг.2 г и а). Однако, вследствие хаотического распределения помех во времени, они отстоят друг от друга на величину, не кратную длительности одного элемента сообщения, вследствие чего на фазовый дискриминатор 4 проходят только истинные фронты принимаемых элементов сообщения (фиг.2к), а ложные, обусловленные дроблениями, не проходят (фиг.2м).

Анало1 ичным образом в случае краевых искажений принимаемых элементов сообщений (фиг.2ь) на выходе дифференцирующего блока 1 наряду с истинными формируются и ложные синхроимпульсы (фиг.2е). Однако, вследствие случайного распределения во времени величин краевых искажений, ложные синхроимпульсы, соотяотстпукяпие фронтам искаженных элементов сообщения, отстоят друг от друга на величину, не кратную Г , вследствие чего на выходах элемента И 9 и дополнительных элементов И 10 формируются только истинные синхроимпулт.сы (фиг-.2ц), Вследствие этого на фазовый дискриминатор 4 прохолят истиилые синхроимпульсы (фи1 .2л) и не проходят ложные

синхроимпульсы, обусловленные к раевы- ми искажениями (фиг.2н).

Фазовый дискриминатор 4 осуществляет сравнение фазы синхроимпульсов с фазой тактовых импульсов. В случае несовпадеыия фаз на выходах фазового дискриминато эа 4 формируются корректирующие импульсы добавления или исключения соответственно р случаях отставания или опережения фазы тактовых импульсов. В зависимости от вида реализации фазового дискриминатора 4 на каждый из его входных импульсов, соответствующих фронтам, формируется один или несколько (в зависимости от величины рассогласования фаз) корректирующих импульсов соответствующего знака. Формирователь 5 производит

154Д64

ные задающий генератор, блок добавления-исключения импульсов, делитель частоты, фазовьй дискриминатор и формирователь корректирующих сигналов, первый и второй выходы которого подсоединены соответственно к первому и второму управляющим входам блока добавления-исключения импульсов, пос10 ледовательно соединенные дифференци- . р,ующий блок и блок задержки, а также элемент И, первый вход которого подключен к выходу дифференцирующего блока, причем вход дифференцирующего

15 блока и первый выход делителя частоты являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повьшения точности синхронизации в условиях

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Фазовый дискриминатор | 1982 |

|

SU1027799A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU1043832A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1099403A1 |

Изобретеяие относится к области электросвязи и м.б. использовано в системах передачи дискретной информации. Цель изобретения - повышение точности синхронизации в условиях помех без снижения быстродействия. Устр-во содержит дифференцирующий блок (ДБ) 1, задающий г-р 2, делитель 3 частоты, фазовый дискриминатор (ФД) 4, формирователь 5 корректирующих сигналов, блок добавления- исключения 6 импульсов, блок задержки (БЗ) 7, элемент И 9. В устр-во введены элемент ИЛИ 8 и дополнительные элементы И 10,-10„. Фронты эле- ментов сообщения с выхода ДБ 1 поступают на вход БЗ 7 и первые входы элемента И 9 и дополнительных элементов И 10, на вторые входы которых поступают фронты входных элементов, задержанные на длительность, кратную одному элементу сообщения. Фронты неискаженных элементов сообщения с выхода элемента ИЛИ 8 поступают на вход ФД 4. Формирователь 5 производит усреднение импульсов и формирует выходные корректирующие импульсы, управляющие работой блока добавления- исключения 6 путем изменения кол-ва импульсов, поступающих на вход делителя 3. 2 ил. S (/: с

усреднение этих импульсов и формирует 20 помех без снижения быстродействия, выходные корректирующие импульсы, управляющие работой блока 6 добавления- исключения путем изменения (увеличения или уменьшения) числа импульсов высокой частоты, которые затем посту- 25 пают на вход делителя 3. Изменение (добавление или исключение) числа импульсов высокой частоты, подвергаемых делению, приводит к соответствующему изменению частоты и фазы выходных .30 тактовых импульсов, поступающих с первого и- второго выходов делителя 3.

введены дополнительные элементы И и элемент ИЛИ, при этом первые входы дополнительных элементов И подключе ны к выходу дифференцирующего блока вторые входы элемента И и дополнительных элементов И подключены к со ответствующим .выходам блока задержк выходы элемента И и дополнительных элементов И подсоединены к соответс вующим входам элемента ИЛИ, выход которого подсоединен к входу синхро низирующего сигнала фазового дискри минатора, второй тактовый вход кото рого подключен к второму выходу дел теля частоты, причем второй выход делителя частоты является дополнительным выходом устройства.

Формула изобретения

Устройство тактовой синхронизации, содержащее последовательно соединенпомех без снижения быстродействия,

введены дополнительные элементы И и элемент ИЛИ, при этом первые входы дополнительных элементов И подключены к выходу дифференцирующего блока, вторые входы элемента И и дополнительных элементов И подключены к соответствующим .выходам блока задержки, выходы элемента И и дополнительных элементов И подсоединены к соответствующим входам элемента ИЛИ, выход которого подсоединен к входу синхронизирующего сигнала фазового дискриминатора, второй тактовый вход которого подключен к второму выходу делителя частоты, причем второй выход делителя частоты является дополнительным выходом устройства.

| Устройство выделения тактовых импульсов | 1982 |

|

SU1062880A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| 0 |

|

SU282404A1 | |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-08-07—Публикация

1985-12-29—Подача