t

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных машинах, работающих в избыточной двоичной системе счисления.

Известно устройство для сложения нескольких п- разрядных двоичных чисел 11, содержащее m рядов одноразрядных двоичных сумматоров в каждом из п блоков суммирювания.

В этом устройстве производится сложение чисел только в .цвоичной системе счисления, т.е. это устройство не позволяет выполнять суммирование нескольких чисел в избыточной двоичной системе счисления.

В известном устройстве (2, содержащем в каждом из п разрядов сумматор в избыточной двоичной системе счисления, первый и второй выходы которого подключены к выходным шинам устройства, .суммируются только два числа в избыточной двоичной системе счисления.

Наиболее близким к данному изобретению является устройство для сложения в избыточной двоичной системе счисления (31, содержащее в каждом из п разрядов два двоичных сумматора и сумматор в избыточной двоичной системе счисления, в котором переносы распространяются от старших разрядов к младимм, что дает некоторый выигрыш в быстродействии устройства.

Недостатком этого устройства является наличие сложного сумматора в избыточной двоичной системе счисления, который содержит четыре од0но{}азрядных двоичнЕзК суьвиатора и два элемента запрета.

Целью изобретения является упрющение устройства.

Для достижения этой цели в уст5ройстве, содержащем в каждом из п разрядов первый и второй двоичные сумматоры, первая группа входов которых соединена с шинами соответственно отрицательных и положитель0ных значений соответствующего разряда слагаемых, и первый и второй элементы запрета, выходы которых подключены к выходным шинам соответствующего разряда устройства,в каж5дом из его разрядов выход младшего разряда первого двоичного сумматора подключен ко входу первого элемента запрета и к управляющему входу второго элемента запрета, выход

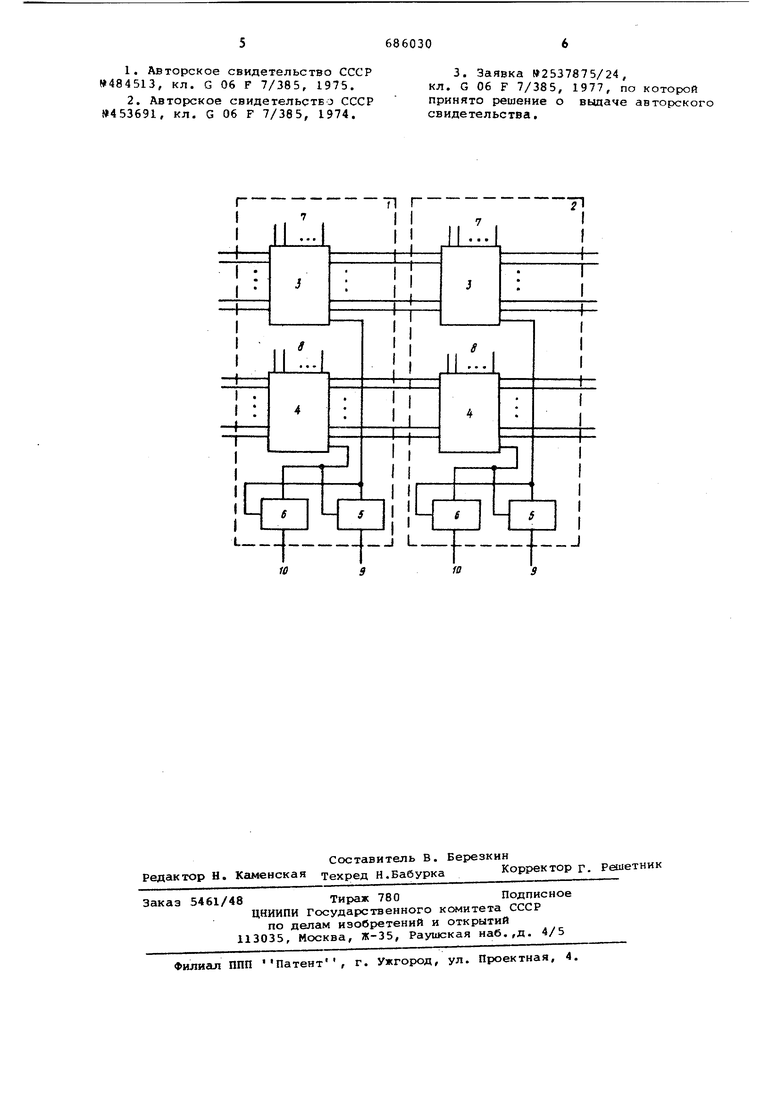

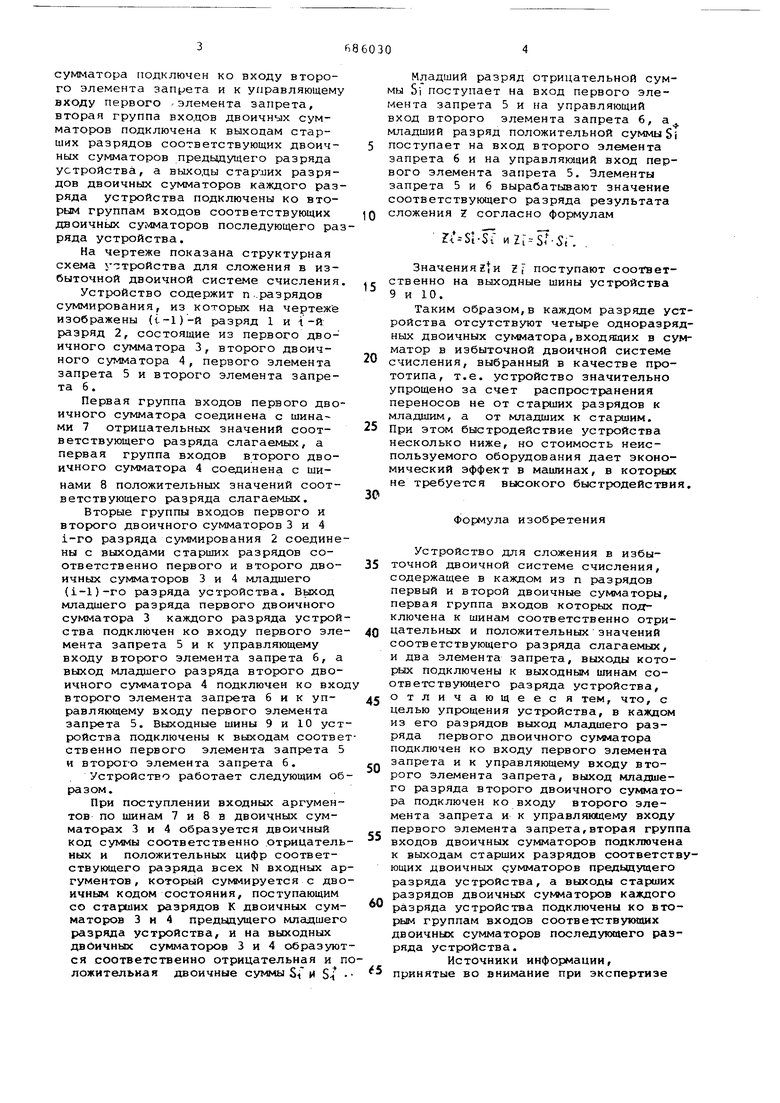

0 младшего второго двоичного сумматора подключен ко входу второго элемента запрета и к управляющему входу первого -элемента запрета, вторая группа входов двоичных сумматоров подключена к выходам старших разрядов соответствующих двоичных сумматоров предыдущего разряда устройства, а выходы стариих разрядов двоичных сумматоров каждого раз ряда устройства подключены ко вторым группам входов соответствующих двоичных сумматоров последующего ра ряда устройства. На чертеже показана структурная схема устройства для сложения в избыточной двоичной системе счисления Устройство содержит п .разрядов суммирования, из которых на чертеже изображены (1-1)-fi разряд 1 и i-и разряд 2, состоящие из первого дноичного сумматора 3, второго двоичного сумматора 4, первого элемента запрета 5 и второго элемента запрета 6. Первая группа входов первого дво ичного сумматора соединена с шинами 7 отрицательных значений соответствующего разряда слагаемых, а первая группа входов второго двоичного сумматора 4 соединена с шинами 8 положительных значений соответствующего разряда слагаемых. Вторые группы входов первого и второго двоичного сумматоров 3 и 4 1-го разряда суммирования 2 соедине ны с выходами старших разрядов соответственно первого и второго двоичных сумматоров 3 и 4 младшего (i-l)-ro разряда устройства. Вькод младшего разряда первого двоичного сумматора 3 каждого разряда устрой ства подключен ко входу первого эле мента запрета 5 и к управляющему входу второго элемента запрета б, а выход младшего разряда второго дво ичного сумматора 4 подключен ко вх второго элемента запрета 6 и к управляющему входу первого элемента запрета 5. Выходные шины 9 и 10 ус ройства подключены к выходам соотв ственно первого элемента запрета и второго элемента запрета 6. Устройство работает следующим о разом. При поступлении входных аргумен тов по шинам 7 и 8 в двоичных сумматорах 3 и 4 образуется двоичный код суммы соответственно отрицател ных и положительных цифр соответствующего разряда всех N входных а гументов , который су1 я 1ируется с дв ичным кодом состояния, поступающим со старших разрядов К двоичных сум маторов 3 и 4 предыдущего младшег разряда устройства, и на выходных двйичных cyм aтopoв 3 и 4 образую ся соответственно отрицательная и ложительная двоичные Si И S Младший разряд отрицательной сумы Si поступает на вход первого элеента запрета 5 и на управляющий ход второго элемента запрета б, а ладший разряд положительной суммы Si оступает на вход второго элемента запрета б и на управляющий вход перого элемента запрета 5. Элементы запрета 5 и б вырабатывают значение оответствующего разряда результата ложения г согласно формулам г -зЬзТ n2L-sT-5,. . Значенияг{и 21 поступают соогветственно на выходные шины устройства 9 и 10. Таким образом,в каждом разряде устройства отсутствуют четыре одноразрядных двоичных сумматора,входящих в сумматор в избыточной двоичной системе счисления, выбранный в качестве прототипа, т.е. устройство значительно упрощено за счет распространения переносов не от старших разрядов к младшим, а от младших к старшим. При этом быстродействие устройства несколько ниже, но стоимость неиспользуемого оборудования дает экономический эффект в машинах, в которых не требуется высокого быстродействия. Формула изобретения Устройство для сложения в избыточной двоичной системе счисления, содержащее в каждом из п разрядов первый и второй двоичные су виаторы, первая группа входов которых подключена к шинам соответственно отрицательных и положительных значений соответствующего разряда слагаемьк, и два элемента запрета, выходы которых подключены к выходным шинам соответствующего разряда устройства, отлнчающеес я тем, что, с целью упрощения устройства, в каждом из его разрядов выход младшего разряда первого двоичного сумматора подключен ко входу первого элемента запрета и к управляющему входу второго элемента запрета, выход младшего разряда второго двоичного сумматора подключен ко входу второго элемента запрета и к управляющему входу первого элемента запрета,вторая группа входов двоичных сумматоров подключена к выходам старших разрядов соответствующих двоичных думматоров предьщущего разряда устройства, а выходы старших разрядов двоичных сумматоров каждого разряда устройства подключены ко вторяз1М группам входов соответствующих двоичных сумматоров последующего разряда устройства. Источники информации, принятые во внимание при экспертизе

иио11с, свидетельство СССР №484513, кл. G 06 Р 7/385, 1975.

..г торское свидетельство СССР W453691, кл. G 06 F 7/385, 1974.

3. Заявка №2537875/24 кл. G 06 F 7/385, 1977, по которой

STni.ZT.T: ° --

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

| Устройство для сложения в избыточной двоичной системе | 1978 |

|

SU860064A2 |

| Устройство для сложения чисел в избыточной двоичной системе счисления | 1978 |

|

SU769538A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

Г

.- -Ilpj Ljlp

f 9fa,

Т I71

II7|

Авторы

Даты

1979-09-15—Публикация

1978-04-11—Подача