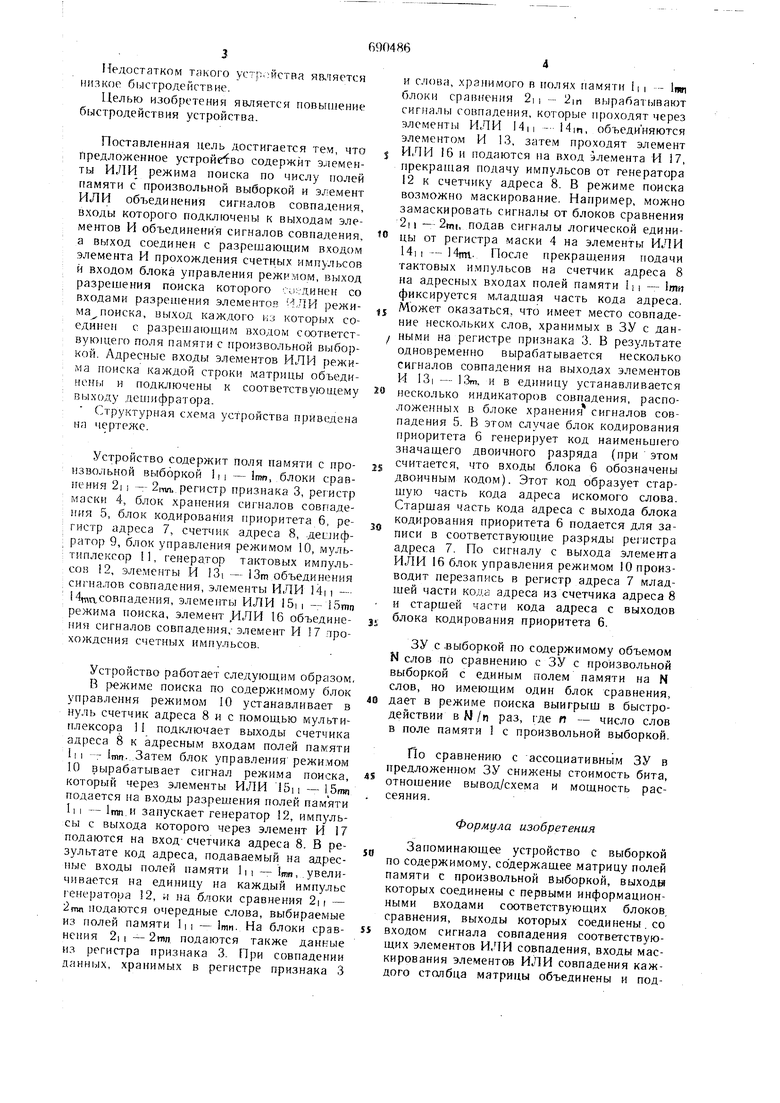

Недостатком такого устройства является низкое быстродействие. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что ПредлС1женное устройе -во содержит элементы ИЛИ режима поиска по числу полей памяти с произвольной выборкой и элемент ИЛИ объединения сигналов совпадения, входы которого подключены к выходам элементов И объединения сигналов совпадения, а выход соединен с разрешающим входом элемента И прохождения счётных импульсов и входом блока управления режимом,выход разрешения поиска которого соединен со входами разрешения элементов ИЛИ режима поиска, выход каждого из которых соединен с разрешаюш.им входом соответствующего поля памяти с произвольной выборкой. Адресные входы элементов ИЛИ режима поиска каждой строки матрицы объединены и подключены к соответствующему выходу дешифратора. Структурная схема устройства приведена на чертеже. Устройство содержит поля памяти с произвольной выборкой 111 - Iron, блоки сравнения 2| I - 2tTOT.. регистр признака 3, регистр маски 4, блок хранения сигналов совпадения 5, блок кодирования приоритета 6, регистр адреса 7, счетчик адреса 8, .дешифратор 9, блок управления режимом 10, мультиплексор 11, генератор тактовых импульсов 12, элементы И 13i - 13т.объединения, сигналов совпадения, элементы ИЛИ l4i i 14тп,совпадения, элементь ИЛИ 15ii - 15то режима поиска, элемент ,ИЛИ 16 объединения сигналов совпадения,-элемент И 17 прохождения счетных импульсов. Устройство работает следующим образом, В режиме поиска по содержимому блок управления режимом ГО устанавливает в нуль счетчик адреса 8 и с помощью мультиплексора 11 подключает выходьГ счетчика адреса 8 к адресным входам полей памяти III - Imn...Затем блок управлениярежимом 10 вырабатывает сигнал режима поиска, который через элементы ИЛИ 15i i - подается на входы разрешения полей памяти 1м - ItTin.и запускает генератор 12, импульсы с выхода которого через элемент И 17 подаются на вход- счетчика адреса 8. В результате код адреса, подаваемый на адресные входы полей памяти 111 - IBM , увеличивается на единицу на каждый импульс генератора 12, и на блоки сравнения 2 i - 2nm подаются очередные слова, выбираемые из долей памяти lii - Imn... На блоки сравнения 2м - . подаются также данные из регистра признака 3. При совпадений данных, хранимых в регистре признака 3 и слова, хранимого в полях памяти In - 1пи блоки сравнения 2i i - 2in вырабатывают сигналы совпадения, которые проходят через элементы ИЛИ 14м - 14т, объединяются элементом И 13, затем проходят элемент ИЛИ 16 и подаются на вход элемента -И 17, прекращая подачу импульсов от генератора 12 к счетчику адреса 8. В режиме поиска возможно маскирование. Например, можно замаскировать сигналы от блоков сравнения 2м -2tni, подав сигналы логической единицы от регистра маски 4 на элемент-ы ИЛИ 14|1-14пп. После прекращения подачи тактовых импульсов на счетчик адреса 8 на адресных входах полей памяти 1м - 1тя фиксируется младшая часть кода адреса. Может оказаться, что имеет место совпадение нескольких слов, хранимых в ЗУ с данными на регистре признака 3. В результате одновременно вырабатывается несколько сигналов совпадения на выходах элементов И 13 - 13т, и в единицу устанавливается несколько индикаторов совпадения, расположенных в блоке хранения сигналов совпадения 5. В этом случае блок кодирования приоритета 6 генерирует код наименьщего значащего двоичного разряда (при этом считается, что входы блока 6 обозначены двоичным кодом). Этот код образует старшую часть кода адреса искомого слова. Старшая часть кода адреса с выхода блока кодирования приоритета 6. подается для записи в соответствующие разряды регистра адреса 7. По сигналу с выхода элемента ИЛИ 16 блок управления режимом 10 производит перезапись в регистр адреса 7 младщей части кода адреса из счетчика адреса 8 и старшей части кода адреса с выходов блока кодирования приоритета 6. .ЗУ с .выборкой по содержимому объемом N слов по сравнению с ЗУ с произвольной выборкой с единым полем памяти на N слов, но имеющим один блок сравнения, дает в режиме поиска выигрыш в быстродействии вМ/г раз, где п - число слов а поле памяти 1 с произвольной выборкой. По сравнению с ассоциативном ЗУ в предложенном ЗУ снижены стоимость бита, отношение вывод/схема и мощность рассеяния. Формула изобретения Запоминающее устройство с выборкой по содержимому, содержащее матрицу полей памяти с произвольной Выборкой, ВЫХОД{Я которых соединены с первыми информационными входами соответствующих блоков, сравнения, выходы которых соединены. со входом сигнала совпадения соответствующих элементов ИЛИ совпадения, входы маскирования элементов ИЛИ совпадения каждого сталбца матрицы объединены и подключены к соответствующему выходу регист ра маски, вход которого подключен ко входу маски устройства, вход признака которого соединен со входом регистра признака, группы выходов которого соединены со вторыми информационными входами блоков сравнения соответствующего столбца матрицы, выходы элементов ИЛИ совпадения каждой строки матрицы соединены с соответствующими входами элементов И о6ъелит мня сигналов совпадения, выходы которых чо;нз блок хранения сигналов совпадения соединены со входами блока кодировэния приоритета, выходы которого соединены со входами старщих разрядов регистра адреса, входы младщих разрядов которого подключены к выходам счетчика адреса, которые соединены с одной группой входов мультиплексора другая группа входов которого подключена к выходам младших разрядов регистра адреса, выходы старших разрядов которого соединены со входами дешифратора, одноименные адресные входы полей памяти с произвольной выборкой объединены и подключены к соответствующему выходу мультиплексора, а управляющие выходы блока управления режимом соединены с управляющими входами регистра адреса, счетчика адреса, мультиплексора и генератора тактовых импульсов, выход которого соединен с импульсным входом элемента И прохождения счетных импульсов, выход которого соединен со счетным входом счетчика адреса, отличающееся тем, что, с целью повышения

быстродействия устройства, оно содержит элементы ИЛИ режима поиска по числу полей памяти с произвольной выборкой и элемент ИЛИ объединения сигна;)ов совпадения, входщ которого подключены к выходам элементов И объединения сигналов совпадения, а выход соединен с разрещающим входом элемента И прохождения счетных импульсов и входом блока управления режимом, выход разрешения поиска которого соединен со входами разрешения элементов ИЛИ режима поиска, выход каждого из которых соединен с разрешающим входом соответствующего поля памяти с произвольной выборкой, адресные входы элементов ИЛИ режима поиска каждой строки матрицы объединены и подключены к соответствующему выходу дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3.540.002, кл. 340- 72.5. 1970.

2.Computer Design, January, 1971, с. 79

(прототип).

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное запоминающее устройство | 1990 |

|

SU1805497A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для преобразования кодов с одного языка на другой | 1985 |

|

SU1275471A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Авторы

Даты

1979-10-05—Публикация

1977-03-22—Подача