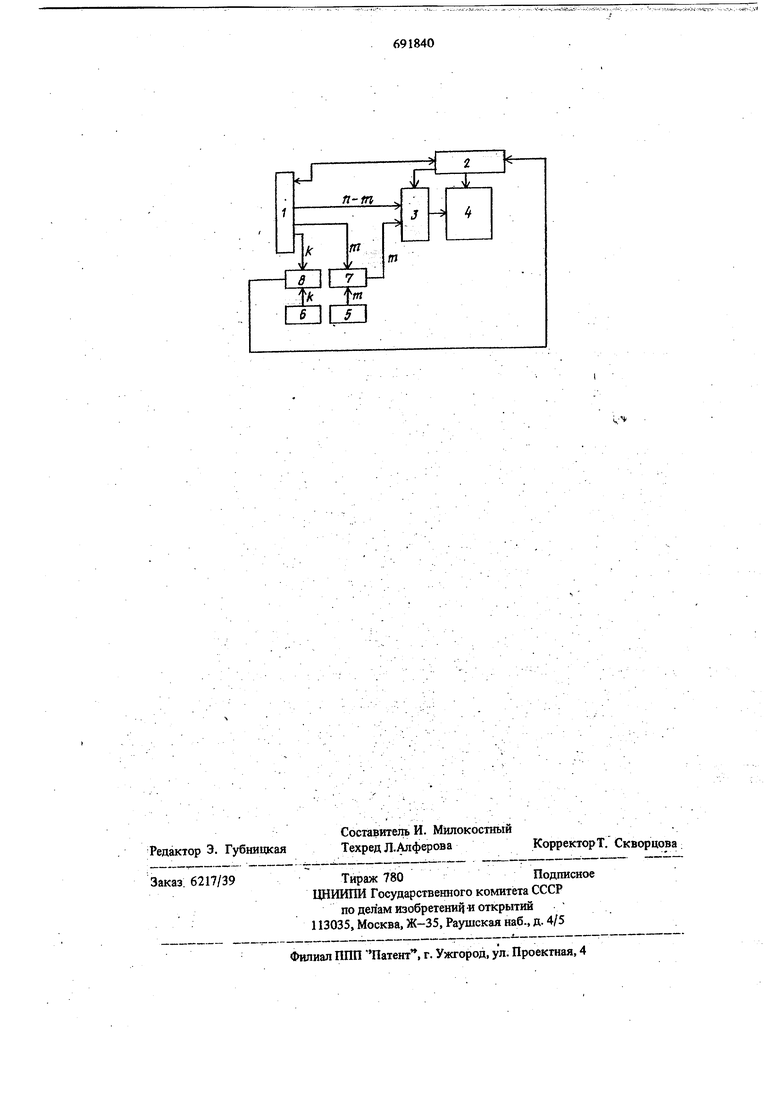

(54) КАНАЛ ПРЯМОГО ДОСТУПА К ПАМЯТИ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ управляющих сигналов, блок управления 2, блок 3 формирования адреса памяти, память 4 генераторы констанг 5, 6, сумматоры 7, 8. Блок 1 имеет п выходов цепей передачи данных, причем m старших разрядов указанных цепей соединены с m входами первого сумматора 7, щ)угие m входов которого соединень с m выходами первого генератора кон,стант 5. Дополнительно k выходов старших разрядов цепей передачи данНь1Х блока 1 соединены с k входами второго сумматора 8, дру гие k входов которого соединены с k выходами второго генератора, констант 6. Младшие n-m разрядов цепей передачи данных блока 1 соединил с n-m входами младших разрядов блока 3, а m входов старших разрядов блока 3 соединяются с m выходами первого сумматора 7. Цепи управления блока 1 соединены с со ответствующими входами и выходами блока управления 2, ко входу разрешения регистрации которого подключен выход переполнения второго сумматора 8. Выходы блока зправления 2. соединены с соответствующими входами блока 3 и с паматью 4. Канал; работает следующим образом. Код числа через блок 1 передается в блок формирования адреса памяти 3, причем m стар ших разрядов зтого числа предварительно поступают на вход сумматора 7, где происходит сложение этих разрядов с константой, которая поступает на вход сумматора с первого генератора констант 5. После сложения код с выхода первого сумматора поступает на входы старших разрядов блока формирования адреса памяти 3. Таким образом, на входы блока форм ровашш адреса памяти 3 поступил код, отличающийся от кода, пост ающего в блок 1 на величину константы А. Это позволяет выбрать начало зоны регистрации в любом месте. Одновременно с поступлением m старших разрядов кода на вход первого сумматора 7 k старц1их разрядов этогоОже кода поступают на вход второго сумматора 8, где складывается с константой В. Константа В определяет верхнюю границу зоны {зегйстрации и образуется вторым генератором констант 6. Причем константа В представляет собой дополнительный код верхней границы зоны регистрации. Если поступающий на вход блока 1 код больше, чем код, определяющий верхнюю границу зоны регистрации, то при сложейвга старших разрядов зтого кода с дополнительнь1м кодом верхней границы зоны регистрации произойдет пе)реполнение второго сумматора 8 и сигнал переполнения по шине управления регистрацией поступит на вход блока управления и произойдет затоет регистрации данного кода. Это позволяет защитить y4actoK памяти, лежащий выше верхней границы зоны регистрации. Если же поступающий код меньше константы В, то блок управления 2, не получив по шине управления регистрацией запрещающего сигнала, разрешает регистрацию кода, поступившего, на входы блоа 3.. Таким образом достигается выбор зоны для регистрации информации от входного преобразующего блока (на чертеже не показан). Введение новых элементов позволяет зыби- . рать любые участки памяти с заданной кратностью в любом месте памяти и защищать участки памяти, не используемые для регистрации , при этом время формирования адреса определяется быстродействием сумматоров, что определяет повьциение пропускной способности канала. Формула изобретения Канал доступа к памяти злектронной вычислительной мащины, содержащий блок передачи данных и управляющих сигналов, блок управления, соединенные двухсторонней связью, блок формирования адреса памяти, память, первый и второй генераторы констант, причем первая группа информациошп 1Х выходов блока передачи данных и управляющих сигналов соединена с первой группой входов блока формирования адреса памяти, первый и второй выходы блока управления соединены соответственно с управляющими входами блока формирования адреса памяти и памяти, группа выходов блока формирования адреса памяти соединена с группой адресных входов памяти, отличающийся тем, что, с целью повьпиения пропускной способности, он содержит первый и второй сумматоры, причем вторая и третья группы информационных выходов блока передачи данных и управляющих сигналов соединены соответственно с первыми входами первого и второго q MMaTopoB, вторые входы которых соединены соответственно с выходами первого и второго генераторов констант, группы выходов первого и второго сумматоров соединены соответственно со второй гр Ш1ой входов блока формирования адреса памяти и с группой входов блока управления. Истйчники информации, принятые во внимание при зкспертизе 1.Комплекс управляющий вычислительный М-600р(ТУ-25-01-7), 1974. 2.Авторское свидетельство СССР № 408308. кл G 06 F 9/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для ввода аналоговой информации | 1986 |

|

SU1377848A1 |

| Генератор случайных чисел | 1981 |

|

SU1008738A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

Авторы

Даты

1979-10-15—Публикация

1977-01-07—Подача