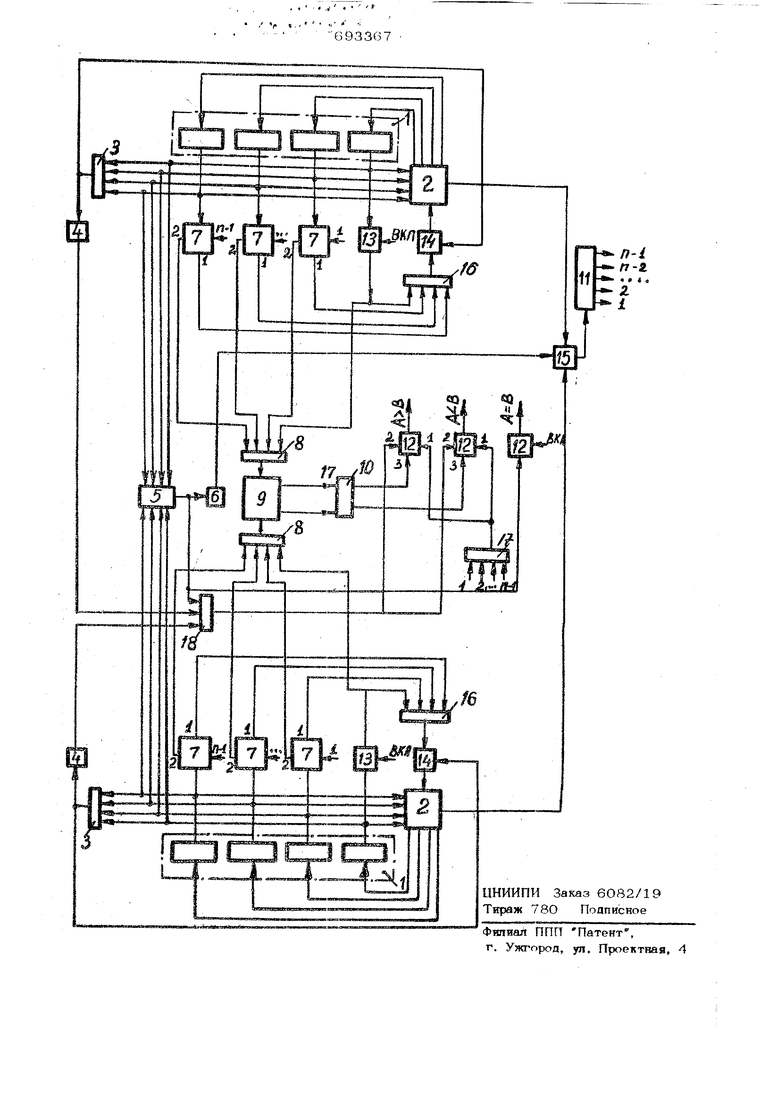

(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ И BTopotx регистров подключены ко входам первой и второй групп бпоков преобразования соответственво, вьисоды регистров подклкяены к соответствуюшйм входам схемы сравнения на равенстйо, выход которой соединен с Первым входом третьетх эпёмента ИЛИ, второй и третий входы которого через первый и второй эпементат НЕ подкпючены к вь,1ходам первого и второго aiiieментов ИЛИ соответственно, третьего эйемента ИЛИ с 5бдинев с первым четвёртого в пятого эпемзэнтов И, BTOpt ie етойй которьгх подкяючё Ш д KjixOHat триггера, а третьи - к выходу четвертого эпемецта ИЛИ, входы кото- соедййейы с вькодами расирёдепитепй сигналов, вход которого поДклкяей .к выходу первого элемента И, трезйй КС од Которого через третий элемент НЕ средйкен с выходом схемы срабневия на равенство ,выход которой подключенк перйому входу шеетого элемента И, вто рой вход ззоторого соединен с шиной управления, соответствующие BJbKOflbi блоков, преобразования первой груипь шэдклК)чей1л ко входам пятого и шестого эпемевтов ИЛИ, ко входам которьи подвтайёв та&же выход второго элеweii та И, второй вход которого соединен с йдаой утгравпеняя, а соответствукшие ВЫХОД, блрЕов преобразования второй rpyni&i пря;кй|Ьчеда ко- седьмого н-йосьмого э пементоБ ИЛИ, ко входам которых подгслючен также выход третьего элемента И, второй вход которого соединён е шшой управлшЕя, вь1ходы пятого и седьмого элемевтов ИЛИ поДKnkweiOji )кй входём одноразрядной схеш сравнений, йыхогва которой соединены, со триггера/ а Bbixo jiraecTOix и восьмого элем€гнтов ИЛИ прдкгаочены к первым входам четвертого и пятого элементов И входы которьк соединензЕ, с вьяодами первого и второг ёВекгонтов И1Ш соответственно, выходы растфбдвпятелй сягнйлов иЬдкйючевьг вювхойам соответствующих бловов прёобрёфоваЕНя первой и второй rpjnin, Блок-схемй предложенного устройств прёдставлевй на чертеже, Ус-фойство содержит регистры 1, сумматоры 2, э фменты ИДИ 3 с эЛементамн НЕ 4, схему 5, сравнения на равенство с элементом НЕ 6, блоки 7 прво6разованйЯ| элементы ИЛИ S, одноразрядную схему 9 сравнения, трнггер 10, распределитель 11 сигналов, элементы И 12-15 элементы ИЛИ 16-18. Устройство работает следующим образом. На регистрах 1 записаны сравниваемые числа. Исходное состояние элементов схемы Зависит от соотношения значений сравниваемых чисел. В том случае. . если сравниваел«ле числа равны, на выходе схемы 5 сравнения на равенство и, следовательно, на входе элемента И 12, фиксирукмпего равенство чисел, имеется сигнал, а на входе элемента И 15 сигнал отсутствует. Положение триггера 10 произвольно. Сигналы на выходе распределители 11 сигналов отсутствуют, .,., С появлением импульса на шине управйения в случае А В сигнал появляется на выходе упомянутого элемента .И 12. В случае А#Вс включением схемы значения oC-f, и Р) поступают с выходов, элементов И 13 через элементы ИЛИ 8 на вход одноразрядной схемы 9 сравнения, сигвалом с вькода которой триггер 10 устанавливается в состояние А В или А В. Значение Ъ через элементы ИЛИ 16 и И 14 тюступают также на входы сумматоров 2, где происходит вычитание А-of-ii и В - с . перезаписью результатов операции в регистры 1. Сигнал обнуления сумматоров через элемент И 15 поступает на вход распределителя 11 сигналов, в результате чего fta его первом выходе появляется единичный сигнал. С появлением этого сигнала блоки 7 преобразования { h -)-« разрйДов определяют значения вычитаемых по величине остатков данных разрядов. Значения вычитаемых поступают на входы схемы 9. В зависимости от соотношения между этими значениями триггер 10 устанавливается в соответствующее состояние. Одновремевво значения вычитаемых поступают на входы своЕК сумматоров 2, где выполняется операция, аналогичная описанной выше. В том случае, если после окончания результаты срамятся между собой, т.е. на вьясоде схемы 5 : появится сигаал, либо сдан из результатов вь чита11ия обратится в нуль, т.е. на выходе одвЬй иа схем 4 появится сигнал, появитсй сигиап на выходе элемента 6, в результате его откроется один из элементов 12, фиксвруюших А В, А В. В npoTftBHOM случае сигнал обнуления с выходов сумматоров 2 переводит распредепитепь сигналов 11 в состояние, при котором на его следующем выходе появляется сигнал. Процесс вычитания продолжится до появления оа ного из рарсмотренных выше сл гчаев. Данное схемное решение позволяет повысить бьютродействие устройства сравнения чисед noir сравнению с извест ными техническими решениями этой задачи. Ф о р м у л а и 3 о б р е те ни Устройство для сравнения чисел, содержащее два регистра, два су шатора элементы И, ИЛИ, НЕ, триггер, бяаора рядную схему сравнения, rpymibi бтЬков преобразования, распредепитепь сиг налов, схему сравнения на равенство, причем выходь первого регистра соединены со входами первого 9|юмента ИЛИ, первого сумматора, инфоркаапион- ные выгсощ, воторого иодклкйены ко входай первого рёгист| й, а управпяюшйй вьвсод первого сумматора соедини с nepBijfM входом пёрвотхз элемёнфа И, выходы второго регистра тюдключеаь ко входам второго элемента ИЛИ, второго сумматора, информационные %ссоф1 которого соедшюны со входами второго регистра, а управляющий вход второго сумматора подключен ио второму входу первого элемента И, о т л и ч а ю щ е е с я тем, что, с целью повышеви быстродействия в нем выходы старших: разрядов пер;вотх) и второго |регистров соединены с первыми входами второго и третьего элементов И соответствешю а вьЕкоды остальных разрядов первого и второго регистров подключень ко входам гюрвой и второй групп блоков преобразова Ия соответственно, выходы регистров подключены к соответствующим входам схемы сравнения на раеенство, выход которой соединен с первым набдо третьего элемейта ИЛИ, второй и трети входы которого через первый и второй элементы НЕ подключевЬ к выходам 676 первого и второго элементов ИЛИ соот ветственно, выход третьего элемента ИЛИ соединен с первыми входами четвертого и пятого элементов И, вторые входы которых подключеюы к выходам триггера, а третьи - к илходу четвертого элемента ИЛИ, входы которого соединены с вьрсодами распреяелитепя , сигналов, вход подкшочев k вькоду первого этемевта И, третий вход KQTopotx) через элемент НЕ соединен с выходом схемы на раведство, выход к( пбдкгаочен к первому BStoflyimfecwИ, второй вход которого соедивев с швяой управления, соответствующее выходы бяоков нреобрааовавия первой группы подкпючейы ко входам пятого и шестого эпемейтов ИЛИ, Ю входам которых тгодключе также выход второго элемента И, второй вход иотррого соединен с ШИВОЙ управлений, а сснугветствуюшие выходы блсжов тфеобразования второй грутщы тюдключеиы ко входам седьмого и восьмого элементов ИЛИ, ко входам которых тк якл1р« ен также в{лсод третьего элемента И, второй вход которого Ьоедивен с шивой управления, выходы пятого .и седьмого элементов ИЛИ подклкйювы ко входам одвораврядвой схемы сравнения, выходы которой соедиввйы со юсодаМй TpHrrepia, а млхойл Шестого и восьмого эпемевтов ИЛИ подключены к первым вхойам четвертого и вятого эиеМввтов И, вторые входы которых соединены с вькадами пбрвото в второго элементов ИЛИ соо ветствевво, выхот растфеделв епй cBTBianoB поюслючевы ко входам соответствукяавх блоков преобраэовави первой в второй r-pyrm. Источвикв информации, принятые во ЕЯвкшЕтё при 1,Авторское свидетельство СССР J 24 2495, кп. G06 f 7/О4, 12.OS.67. 2.Авторсюое сввдетепьстйо СССР №234003, кл. ОО6 F 7/34, 26.О7 66 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Авторы

Даты

1979-10-25—Публикация

1976-05-24—Подача