(5«) УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ

ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

Изобретение относится к цифровой вьочислительной технике и может быть использовано для аппаратного вычисления элементарных функций.

По основному авт. св. 553612 устройство для вычисления элементарных функций содержит четыре одноразрядных сумматора-вычитаталя, четыре сдвигающих регистра (четвертый регистр является блоком сдвига), блок памяти,блок анализа знака и .блок управления. Первые выходы первого, второго и третьего регистров соединены соответственно с первыми входами первого, второго и четвертого сумматоров-вычитателей, выходы которых соединены соответственно с первыми входами этих регистров. Второй выход первого регистра соединен с первым входом блока анализа, на второй вход которого подсоединен второй выход третьего регистра. Второй выход второго регистра соединен с входом четвертого сдвигающего регистра. Первый выход блока памяти соединен с вторыми входами первого и второго сумматоров-вычитателей. На второй вход третьего сумматора-В1лчитателя подсоединен первый выход четвертого сдвигшощего регистра. На управляющие входы первого, второго и третьего сумматоров-вычитателей подсое-. динен первый быход блока ангшиэа, второй выход которого соединен с управлякмцим входом четвертого сумматора-вычитателя. Выход третьего сумматора-вычитателя соединен со вторым входом четвертого сумматора-вычитателя. Выходы блока управления сое10динены соответственно с управляющими входами (входами сдвига) всех регистров и входом блока памяти.

Такое выполнение известного уст15ройства позволяет производить вычисления квадратного корня или квадрата аргумента в одной структуре без перестройки с относительно высоким ;быстродействием по сравнению с дру20гими тождественными устройствами при аналогичных аппаратурных затрпт. Время вычисления одной из указанных функций равно в тактах

Т « п (п + m + 2) .

25

где п - число двоичных разрядов аргумента , m - число защитных дополнительных разрядов для компенсации погрешности усечения чисел при сдвиге. Цикл вычисления состоит

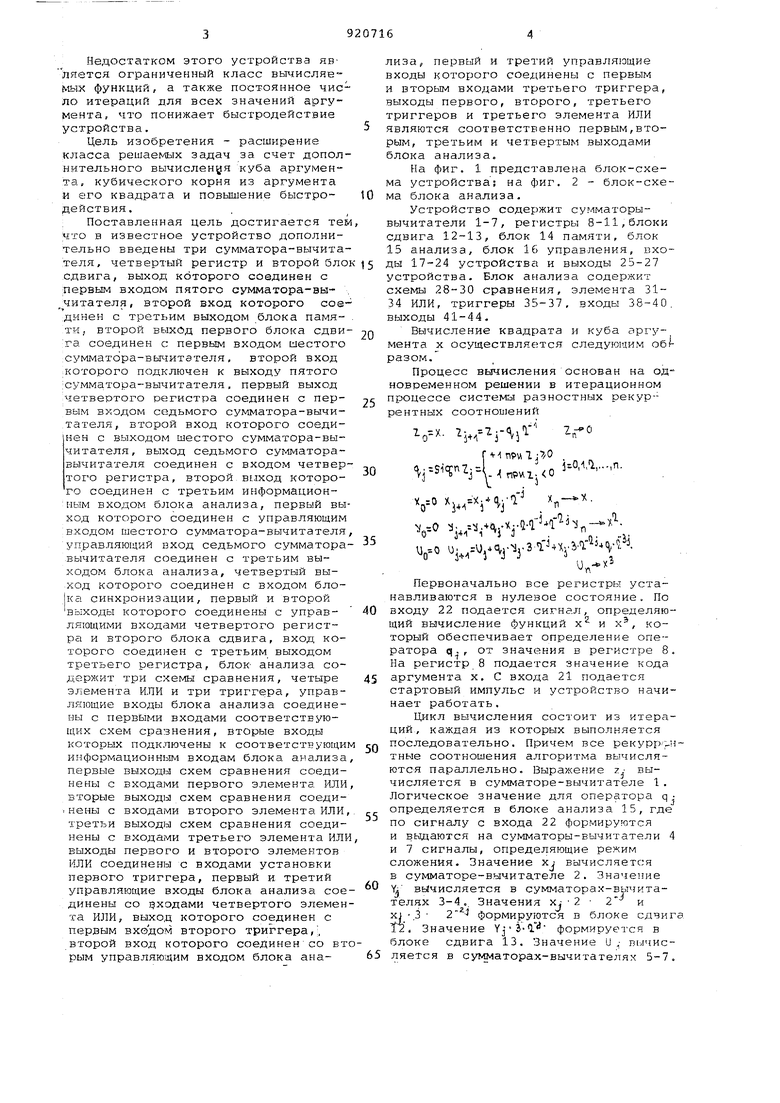

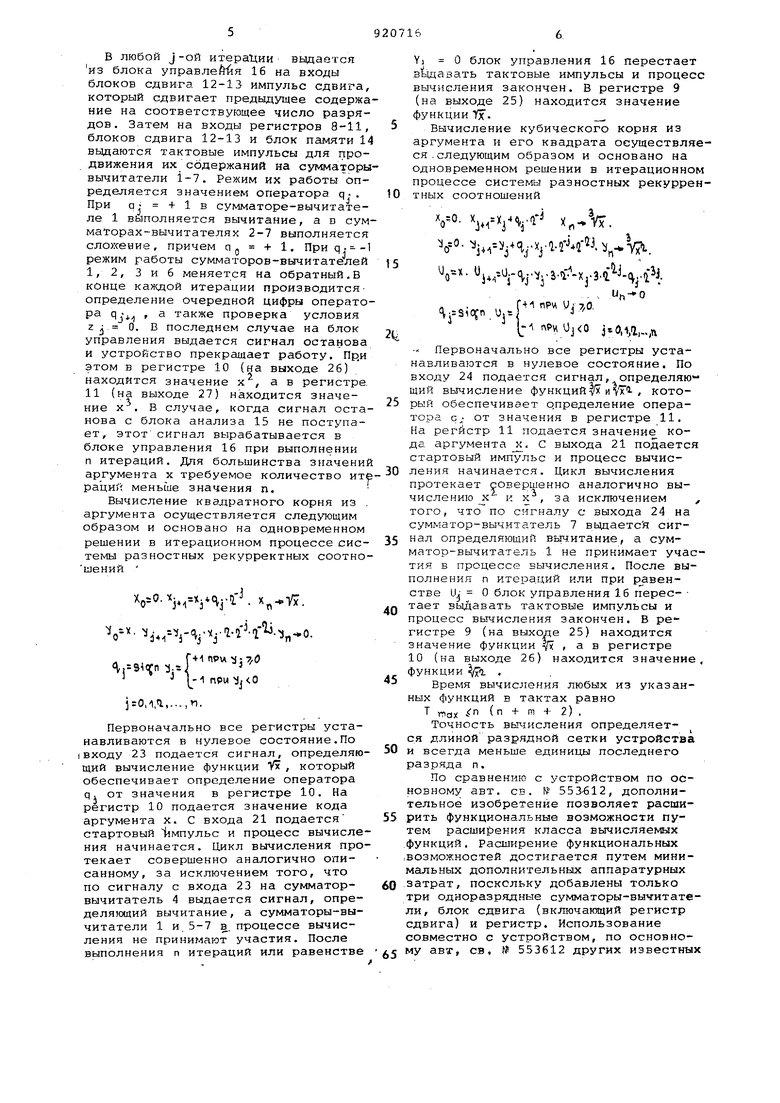

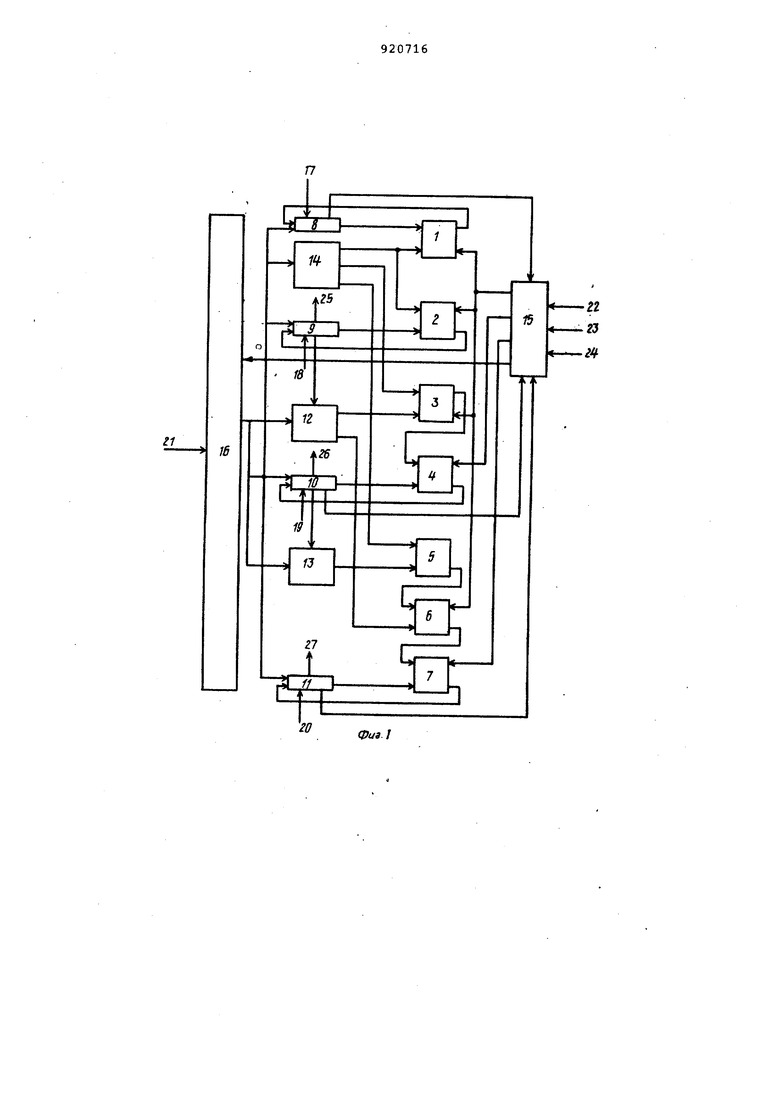

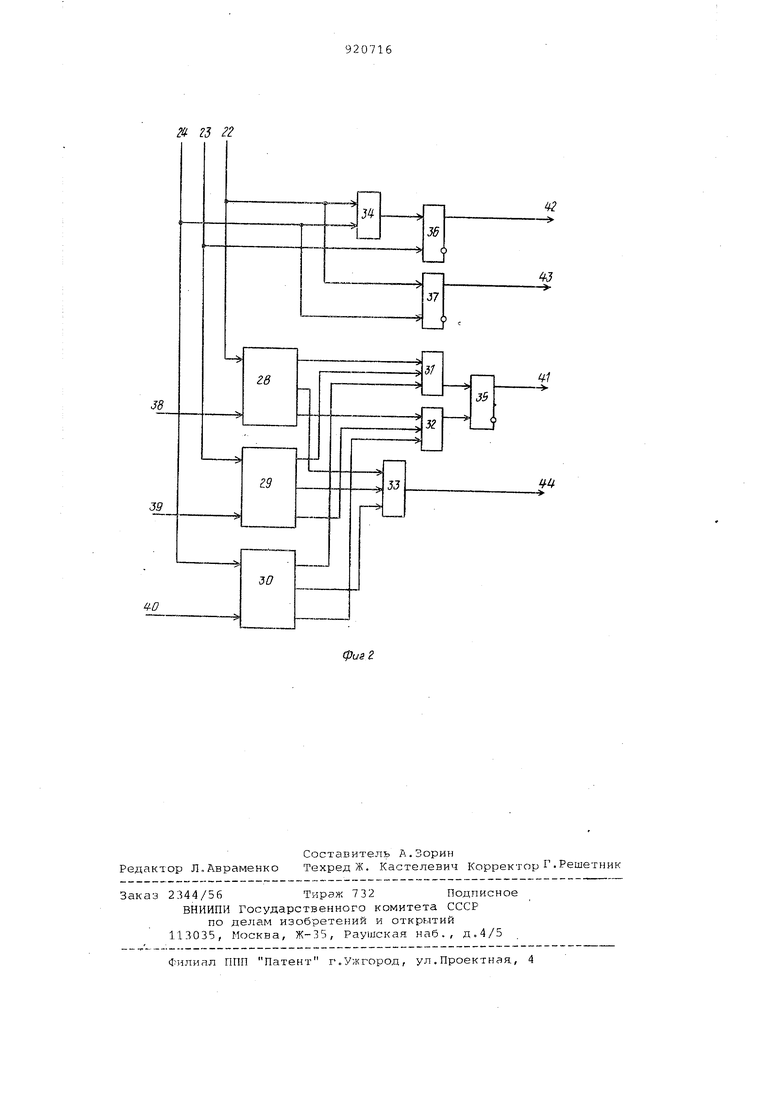

30 из п итераций П . Недостатком этого устройства яв ляетсл ограниченный класс вычисляемых функций, а также постоянное чис ло итераций для всех значений аргумента, что понижает быстродействие устройства. Цель изобретения - расширение класса решаемых задач за счет допол нительного вычисления куба аргумента кубического корня из аргумента и его квадрата и повышение быстродействия. Поставленная цель достигается тем что в известное устройство дополнительно введены три сумматора-вычита теля, четвертый регистр и второй бло сдвига, выход которого соединен с первым входом пятого сумматора-вы читателя, второй вход которого cos динен с третьим выходом блока памяти, второй выход первого блока сдви га соединен с первым входом шестого сумматора-вычитателя, второй вход которого подключен к выходу пятого :сумматора-вычитателя, первый выход четвертого регистра соединен с первым входом седьмого сумматора-вычитателя, второй вход которого соединен с выходом шестого сумматора-вычитателя, выход седьмого сумматоравычитателя соединен с входом четвер того регистра, второй виход которого соединен с третьим информационным входом блока анализа, первый вы ход которого соединен с управляющим входом шестого сумматора-вычитателя управляющий вход седьмого сумматора вычитателя соединен с третьим выходом блока анализа, четвертый выход которого соединен с входом бло1ка синхронизации, первый и второй выходы которого соединены с управляющими входами четвертого регистра и второго блока сдвига, вход которого соединен с третьим выходом третьего регистра, блок анализа содержит три схемы сравнения, четыре элемента ИЛИ и три триггера, управляющие входы блока анализа соединены с первыми входами соответствующих схем сравнения, вторые входы которых подключены к соответствующи информационны входам блока анализа первые выходы схем сравнения соединены с входами первого элемента ИЛИ вторые выходы схем сравнения соеди.йены с входами второго элемента ИЛИ третьи выходы схем сравнения соединены с входами третьего элемента ИЛ выходы первого и второго элементов ИЛИ соединены с входами установки первого триггера, первый и третий управляющие входы блока анализа сое динены со уходами четвертого элемен та ИЛИ, выход которого соединен с первым входом второго триггера,, второй вход которого соединен со вт рым управляющим входом блока анаиза, первый и третий управляющие ходы которого соединены с первым вторым входами третьего триггера, ыходы первого, второго, третьего риггеров и третьего элемента ИЛИ вляются соответственно первым,втоым, третьим и четвертым выходами лока анализа. На фиг. 1 представлена блок-схеа устройства; на фиг. 2 - блок-схеа блока анализа. Устройство содержит сумматорывычитатели 1-7, регистры 8-11,блоки сдвига 12-13, блок 14 памяти, блок 15 анализа, блок 16 управления, вхоы 17-24 устройства и выходы 25-27 устройства. Блок анализа содержит схемы 28-30 сравнения, элемента 3134 ИЛИ, триггеры 35-37, входы 38-40. выходы 41-44. Вычисление квадрата и куба аргумента X осуществля€ тся следующим об разом. Процесс вычисления основан на одновременном решении в итерационном процессе системы ргазностных рекуррентных соотношений i.. ° r -lnPwlj/O . Г-5Ч з--и„,,, K-., V- V-V r3- Первоначально все регистры устанавливаются в нулевое состояние. По входу 22 подается сигнал, определяющий вычисление функций х и х, который обеспечивает определение оператора q. , от значения в регистре 8. На регистр 8 подается значение кода аргумента х. С входа 21 подается стартовый импульс и устройство начинает работать. Цикл вычисления состоит из итераций, каждая из которых выполняется последовательно. Причем все рекурр;-н тные соотношения алгоритма вычисляются параллельно. Выражение z,- вычисляется в сумматоре-вычитателе 1. Логическое значение для оператора qопределяется в блоке анализа 15, где по сигналу с входа 22 формируются и выд:5аются на сумматоры-вычитатели 4 и 7 сигналы, определяющие режим сложения. Значение xj вычисляется в сумматоре-вычита,теле 2. Значение YJ вычисляется в сумматорах-вычитателях 3-4.. Значения xj 2 2 и XJ .3 2 формируются в блоке сдвига , Значение YjJ-l формируется в блоке сдвига 13. Значение U ., вычисляется в суьадаторах-вычитателях 5-7. В любой J-ой итерации выдается из блока управлеМя 16 на входы блоков сдвига 12-13 импульс сдвига который сдвигает предыдущее содержа ние на соответствующее число разрядов. Затем на входы регистров 8-11 блоков сдвига 12-13 и блок памяти 1 выдаются тактовые импульсы для продвижения их содержаний на сумматоры вычитатели 1-7. Режим их работы определяется значением оператора q.. При q- + 1 в сумматоре-вычитателе 1 выполняется вычитание, а в сум маторах-вычитателях 2-7 выполняется сложение, причем аg + 1. Пpиq.режим работы сумматоров-вычитателей 1, 2, 3 и б меняется на обратный,В конце каждой итерации производитсяопределение очередной цифры операто ра qj , а также проверка условия Zj 0. В последнем случае на блок управления выдается сигнал останова и устройство прекращает работу. При этом в регистре 10 (на выходе 26) находится значение х , а в регистре 11 (на выходе 27) находится значение X . В случае, когда сигнал оста нова с блока анализа 15 не поступает, этот сигнал вырабатывается в блоке управления 16 при выполнении п итераций. Для большинства значени аргумента х требуемое количество ит раций меньше значения п. Вычисление квадратного корня из аргумента осуществляется следующим образом и основано на одновременном решении в итерационном процессе системы разностных рекурректных соотно шений V JH- i Hj-l x.VJ. o- d.,-- r j j- - -l - n-0. f + i,)J i J Ijl при ,1,4,..,. Первоначально все регистры устанавливаются в нулевое состояние.По I входу 23 подается сигнал, определяю щий вычисление функции Ух, который обеспечивает определение оператора q, от значения в регистре 10. На регистр 10 подается значение кода аргумента х. С входа 21 подается стартовый импульс и процесс вычисле ния начинается. Цикл вычисления про текает совершенно аналогично описанному, за исключением того, что по сигналу с входа 23 на сумматорвычитатель 4 выдается сигнал, определяющий вычитание, а сумматоры-вычитатели 1 и,5-7 в. процессе вычисления не принимают участия. После выполнения п итераций или равенстве Y О блок управления 16 перестает выдавать тактовые импульсы и процесс вычисления закончен. В регистре 9 (на выходе 25) находится значение функции fj(. Вычисление кубического корня из аргумента и его квадрата осутдествляеся.следующим образом и основано на одновременном решении в итерационном процессе систег й разностных рекуррентных соотношений VO . . ., . iJh-o .u.P i°L- РИ ,1,l,..,ft Первоначально все регистры устанавливаются в нулевое состояние. По входу 24 подается сигнал, определяющий вычисление функций7 , который обеспечивает определение оператора с. от значения в регистре 11, На регистр 11 подается значение кода аргумента , С выхода 21 подается стартовый импульс и процесс вычисления начинается. Цикл вычисления протекает совершенно аналогично вычислению jc и X , за исключением , того, что по сигналу с выхода 24 на cyм 5aтop-вычитaтeль 7 выдается сигнал определяющий вьтчитание, а сумматор-вычитатель 1 не принимает участия в процессе вычисления. После выполнения п итераций или при равенстве U,j О блок управления 16 перес- тает выдавать тактовые импульсы и процесс вычисления закончен. В регистре 9 (на выходе 25) находится значение функции , а в регистре 10 (на выходе 26) находится значение, функции CL . Время вычисления любых из указанных функций в тактах равно Т niax г (п + т + 2} , Точность вычисления определяется длиной разрядной сетки устройства и всегда меньше единицы последнего разряда п. По сравнению с устройством по основному авт, св. № 553-612, дополнительное изобретение позволяет расширить функциональные зозможности путем расширения класса вычисляемых функций, Расширение функциональных возможностей достигается путем минимальных дополнительных аппаратурных затрат, поскольку добавлены только три одноразрядные сумматоры-выч-итатели, блок сдвига (включающий регистр сдвига) и регистр. Использование совместно с устройством, по основному авт, св. № 553612 других известных устройств для вычисления указанных, функций экономически {по стоимости и аппаратурным затратам) и технически (по быстродействию) нецелесообраз но. Основным достоинством данного устройства является также отсутствне перестройки структуры операционной части устройства в процессе работы при переходе от вычисления одних функций к другим, т.е. устройство характеризуется унифицированной структурой. Дополнительные аппаратурные затра ты не требуют новых схемных решений по сравнению с основным изобретением. Все схемотехнические решения устройства являются стандартными в ,цифровой вычислительной технике и выпускаются промышленностью в интегральном исполнении. Данное устройство может быть изготовлено в виде одной БИС. Формула изобретения 1. Устройство для вычисления элементарных функций по авт. св. №553612, отличающееся тем, что, с целью расширения клас са решаемых задач за счет дополнительного вычисления куба аргу MeHlra, кубического корня из аргумен та и его квадрата, в него введены три сумматора-вычитателя,четвертый регистр и второй блок сдвига, выход которого соединен с первым входом пятого сумматора-вычитателя, второй вход которого соединен с третьим выходом блока памяти, второй выход первого блока сдвига соединен с пер вым входом шестого сумматора-вычита теля, второй вход которого подключе к выходу пятого сумматора-вычитател первый выход четвертого регистра со динен с первым входом седьмого сумматора-вычитателя, второй вход кото рого соединен с выходом шестого сум матора-вычитателя, выход седьмого сумматора-вычитателя соединен с вхо дом четвертого регистра, второй выход которого соединен с третьим информационным входом блока анализа, первый выход которого соединен с управляющим входом шестого сумматора-вычитателя, управляющий вход седьмого сумматора-вычитателя соединен с третьим выходом блока анализа, четвертый выход которого соединен с входом блока синхронизации,; первый и второй выходы которого coejдинены с управляющими входами четвертого регистра и второго блока сдвига, вход которого соединен с третьим выходом третьего регистра. 2. Устройство по п. 1, о т л и ч а ю щ .е е с я/тем, что блок анализа содержит три схемы сравнения, четыре элемента ИЛИ и три триггера, управляющие входы блока анализа соединены с первыми входами соответствующих схем сравнения, вторые входы которых подключены к соответствующим информационным входам блока анализа, первые выходы схем сравнения соединены с входами первого элемента ИЛИ, вторые выходы схем сравнения соединены с входс1ми второго элемента ИЛИ, третьи выходы схем сравнения соединены с входами третьего элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены с входами установки первого триггера, первый и третий управляющие входы блока анализа соединены с входами четвертого элемента ИЛИ, выход котор&го соединен с первым входом второго триггера, второй вход которого соединен с втоpы 5 управляющим входом блока анализа, первый и третий управляющие входы которого соединены с первым и вторым входами третьего триггера, вь,ходы первого, второго, третьего триггеров и третьего элемента ИЛИ являются соответственно первым, вторым и третьим и четвертым выходами блока анализа. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 553612, кл.С 06 F 7/38, 1975 (прототип) .

f 5 г2

Авторы

Даты

1982-04-15—Публикация

1980-04-04—Подача