(54) МИКРОПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

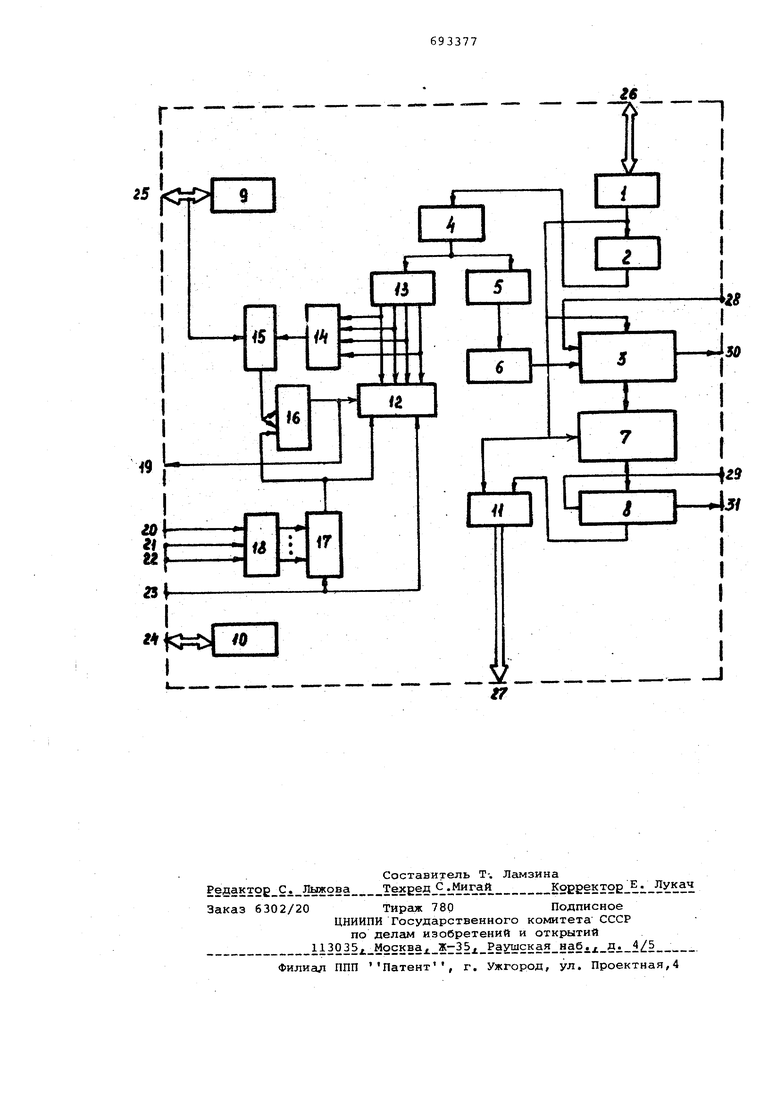

Изобретение относится к области вычислительной техники и может быть использовано при создании больших интегральных схем (БИС), предназначенных ДЛЯ построения вычислительны и управляющих систем. Известны микропроцессоры, содерж щие арифметическо-логическое устрой ство, 6.ПОК регистров, устройство управления, соединенные между собой а также входные и выходные шины пер носа, и предназначенные для построе ния многоразрядных вычислительных систем (1. Недостаток подобного микропроцес сора - имеющаяся избыточность при построении вычислительных систем, возникающая из-за функциональной незаконченности микропроцессора,, а именно: устройство управления вычис лительной системой на основе такого микропроцессора реализуется или на основе специальных БИС, или на основе малых интегральных схем. Наиболее близким к изобретению по технической сущности и достигаемым результатам является микропроце сор, содержащий блок управления вводом-выводом данных,-регистр команд, арифметическо-логическое устройство, дешифратор и шифратор команд, регистр управления, блок регистров, формирователь приращений, устройство синхронизации и устройство управления ЦИКЛОМ памяти, адресный регистр, выход которого является выходной шиной адреса, а первый вход адресного регистра соединен с первым выходом формирователя приращений, причем ввод-вывод блока управления вводом-выводом данных соединен с шиной данных, а его вьрсод соединен со вторым входом адресного, регистра, первым входом арифметико-логического устройства, входом блока регистров и входом регистра команд, выход которого соединен через дешифратор и шифратор команд со входом регистра управления, соединенным своим выходом со вторым входом арифметическо-логического устройства, вход-выход которого соединен с входом-выходом блока регистров , вход-выход которого соединен с входом-выходом фюрмироватёля приращений, третий вход арифметическологического устройства является первым входом переносов микрюпроцессора, вход формирователя приращений является вторым входом переносов Микропроцессора,выход арифметическологического устройсгаайвляется перйым выходом переносов микропроцессора, а второй выход формирователя при ращений является вторым выходом ггереносов микропроцессора, выход дешиф ритора команд соединен со входом шйф ратора групп команд 2. Недостатки этого микропроцессора потеря быстродействия при обработке слов больше двойной длины и сложност создания вычислительных систем при аппаЬатнрм наращиваний разрядности. Все это приводит к ограниче1ншо функциональных возможностей, микропро Цесйора иснижению его быстродействи ; Целью изобретения является расширение функциональных возМожнЬстей мйкропроцессора засчет введёнйя дОполнитёльного блока и соответствующи с1вя,зей в тактирующее устройст:во, а .также повыщение быстродействия.микро njsoiteccopa на этой основе. Поставленная цель достгигается тем чтотактирующее устройство выдолнепо в виде распределителя длительност ;тактоб, введены элементь И и ИЛИ, ;Грйггёр, кОДбпреобразооватёль, счетчи фориированйя длительности тактов, группа входов которсзго соединена С группой выходов кодопреобразователя дополнительный вход счетчика соедине с вйещним входом упр,авлений микропрЬцёсборй и первым входом распрёде лйтеля длитель.ности. тактов, а его выход подключей ко второму входу рас пределитедя длительности тактов и к одному из C4eTHiEix входОв тЕ йггера, другой вход триггера соединен с выходом; элемента И, первый вход которо го соединен с выходом элемента ИЛИ, а вт6{)ой вхОд соединен с выходом уст ройства синхронизации, группа BtiScOдов шифратора групп команд соёйине. на с rpiynno входов элемента ИЛИ и с грУпйой входов распределителя длительности тактов, дополнительный , вход распределителя длительности тактов соединен с выходом триггера и выходом микропроцессора, являюгцимся выходом управления синхрониза цией, гоуппа -входов кодопреобразова теля яш1Яётся группой входов микропроцессора, на которые принимается код длительности такта, На чертеже представлена блок-схе ма Микропроцессора. Микропроцессор содержит блок 1 управления вводом-выводом данных, : регист:р 2 команд, арифметическо-логическое устройство 3, дешифратор 4 и шифратор 5 команд, регистр б управления, блок 7 регистров, формирователь 8 приращений, устройство 9 синхронизации, устройство 10 управления циклом памяти, адресный регистр 11, тактирующее устройство 12, выполненное в виде распред лйтеля длительности тактов, шифратор 13 групп команд, элем.ент ИЛИ 14, элемент И 15, триггер 16, счетчик 17 формирования длительности тактов, кодопреобразователь 18, выход 19 управления синхронизацией, группа входоэ 20-22 кодопреобразователя, внешний йход 23 управления микропроцессором, шины 24, 25 управления микр6про14ео.сором,шину 26/данных, шину 27 адреса г входы 28,29 и выходы 30,31 переносов арифметическо-логического устройства 3 и формирователя приращёйий 8, .,/ -..;. / . .;... Шина 26 данйых подключена к блоку i управления вводом-выводом данных, соедйненному пр/вЫхОду с регистром 2 командны, арифмётическо-логическим устройством 3, блоком 7 регистров и адресньЦрегистром 11,другОй вход которого соёдййен с формирователем 8 приращений, а выход подключен к шине 27 адреса. Регистр 2 команда соединён через дешифратор 4 команды с шифратором 13 групп команд и шиф-ратором 5 команды, выход которого Через регистр 6 yttpaiflrteHHH соединён с арифМетическо-логйгескИм устройстйомЗ, выхойОв шифратора 13 . групп комайД соединена;с группой входов- тйктйрующёго устройства 12 и ЬЪ входами элемента ИЛИ 14, вьЬсод которого соёдййен с первым входом элемента И 15,второй вход которого соедин ен с выходом устройств а 9 СийхрОнйзаций, вых;0д Элемента И. 15 соединен со счетным входом триггера 16, выход кОторого соединён с вы- . ходом 19 микропроцессора, являющимся вЕЕйодоМ управлейия синхронизацией, и дЬ;йойнительным управляющим входом тактирующего устройства 12, вТорой вход которого соединен с установочйыМ входом триггера 16 и с выходом счётчика 17 формирования длительности тактОв. К установочным входам счетчика 17 подключены выходы кодопреобразователя 18, группа входов 20-22 которого является входами микропроцессора. Внешний вход 23 управления микропроцессором соединен со счетными входами тактирующего устройства 12 и с доцолйительным входом счетчика 17 формирования длительности тактов, при этом входы и выходы переносов арифметичёско-логического устройства 3. и формирователя 8 прираЩёйий соединены соответственно со входами 28, 29 и выходами 30, 31 переносов микропроцессора. Устройство работает следующим образом. Коды операций. Выполняемых в микропроцессоре, сгруппированы таким образом, что каждой группе соответствует один такт, в котором формируется сигнал переноса, а команды, в которых не формируется сигнал переноса, вообще не вырабатьшают управляющих сигналов на выходе шифратора 13 групп команд. Достигается это тем, что сортветствующие ЭТИМ операциям выходы дегцифратора 4 не подсоединены ко входам шифратора 13 При наращиваний разрядности вычи лительногр устройства аппаратным сц собом на оснрве БИС возникают задерж ки в формировании с|1Гналов переноса ведйчина которых зависит от местрна 1хрждения йрйста ша БИС, от начала их формирр;вания, В изобретение длиазлькостьтактй формирующего: сигнала переноса :йзме-: нягётс ч в зависимости от велйчйнтй этих задерясек аппаратным стюсрбЬм. :. Длительность такта зависит ;от ко да, прстоянно подаваемого на rpyftWy вхрдрь 20-22 кодопреобразователя 18 выход которого 6пределяет код дрпол нения, йнрри;мого в счетчик 17, ПРИ для устррйств, оёрабатываодих старшие разряды сяов, этот код :р-авен 00. .,0 (максимальная дйительнрсть такта) , а для 4ладвй1х раз рядрв - KOR 11... 11 (минЙ1малб нач длйтеЛьнбРть) . промё5кутЪЧ11Ь1х поЛРЯсе.ний микропроцессора вёяичин а длительности такта рпределяётся кодами от ОО...0 11...11 формиррвание дайтельйрсти ripOHSfВРДйтс СйедуюЦйм обра:зом. - ; При прступл энйи на вход устройства по шине 26 ДЙ.ННЫХ кода крмайды 4fepfe3 блок 1 в цикле команды в регистр 2 команд записывается коД командй, подлежащей исполнению, который поступает на вход дешифратора 4 команды, йа вйходе которрго в:бзбужда1ется одйа из шин. Сигйал по этой шине прступаёт на вход шиф аторрв 13 и 5. Выходной код шифратора 5 поступает на {Регистр б управления, выходы которого ; управля от работой устройства 3, блока 7 и фррмйррвателя 8 прираидений, а также формируют или принимают сигналы управления Памятью и шинами в , устройстйах 9 и 10, Если же наУ вход микропроцессора поступает команда, выпрлнёййе которой предполагает формирование сигналов перейоса и рдном из faKToie, то на соответствующем выходе шифратора 13 вырабатывается сигнал, который поступает на вход тактирующего устройства 12 и через элемент ИЛИ 14 на один из входов элемента И 15, на другой вход которого поступает сигнал признака выборки кода операции команды из шины 25 управления. По заднему фронту сигнала признака цикла триггер 16 устанавливается в единичное состояние, переключая выходным сигналом тактирующее устройство 1.2 в режим формирования удлиненного такта, опре деляющего перенос в данной операции При этом выходной сигнал триггера 16 сформируется также на выходе 19 управления синхронизацией. Этот сигнал может быть использован микропроцес-, сором (его секциями) при обработке младших разрядов слов, как сигнал Запррс шины , переводяишй адресные йины и тины денных в вькгокбймпеданснЬе состояние,а указанные секции микропроцессора в состРяйиержй);ания. Длительность такта переноса Рпределя1ется выхрдйым сигналом перенрса сЧетчика 17, который пр установ|Ьчному входу устанавливает триггер 16 в нулевое состояние и переводит .т ктирующее устройство.12 в режим формирования тактов йЬмийаЛ1 ной длйтельнрсти. .Нулевой сигнал на выхРде 19 переводит младшие секции микропроцессора /в режим сйнхррннЪгр выбора следующего кода операций. При поступлении йа вход устройства кода , выполнение которрй не предйрлагает формирование сигналов tiejpeHdca, на выходе шифратора 13 не врзбуждается ни один из управляющих сЙгйЖлов и переключение режима тйктирутощегб устройства 12 йе происхрдит. V;.,. ...-.. ; , ; Изменение тйктоврй сетки не пройзврйится также в 11йкле выбора ко- : маиды, т.е. случаяхпроизводится обработка Информации параллельНР и. ояйрврем енйо, каадбй секцией микропроцессрр ;- . ,.. Суммарнрё время выполйения команды и Йндгр эазрядйрм микропроцессоре, синтезиррваннРм на известных устройствах; равйо. . .у;:.;-, - т;+:(п-1)т, .... -. а визобретении:. ... ... Т,е. быстродействие вычислительной сйстемы, использующей изобретение, пРв1Ь1ш4ет ся в К раз, где равно ТЧСп-Ш 4-h . где п - числр секций микропроцессрора, используемых для: наращивания разрядности; т - цикл микропроцессора. . Таким образом, предаоженное изобретение позволяет, повысить быстродействие вычислительной системы, синтезированной на основе данного микропроцессора, за счет врзмРжности аппаратно регулировать длительнРсть тактов, в которых возникают сигналы пееноса, а также расширить функциональные возможности за счет аппаратого наращивания разрядности. Формула изобретения Микропроцессор, содержащий блок правления вводом-выводом данных. регистр команд, арифметическо-логическое устройство, дешифратор и шифiSatbp команд, регистр управления, блок регистров, формирователь при- ращений, устройство синхронизации и устройство управления циклом памя,ти, адресный регистр, выход которого является выходной шиной адреса, а первый вход адресного регистра соёди нён с: первым выходом формирователя приращений,причем ввод-вывод блока управления вводом-выводом данных соединен с шиной данных, а его вы }Гс й сЪёдйнен со вторым входом адресного регистра, первым входом арифметйЧёеКо-логического устройства, входом блока регистров и входом регистр ШМанд, выход которого соединен через дешифратор И шифратор команд со входом регистра управления,соединенн свЬйМйыходом со вторым входом арифм тическо-логического устройства,входвыход которго соединен с входом-выхо дом бЛока регистров, вход-выход коtropdro соединен с входом-выходом форйирователя приращений, третий вход арифметическо-логического устройства является первым входом переносов микропроцессора, вход формирователя приращ ий является вторым входом переносов микропроцессора, выход арифметическо-логического устройства .является первым выходом пере носов микропроцессора, а второй выход формирователя приращений являетс вторым выходом переносов микропроцессора, выход дешифратора команд со динен со входом шифратора групп команд, о т л и ч а ,ю Щ и и с я тем что, с целью повышения быстродействия, в микропроцессоре тактирующее устройство выполнено в виде распределитёЛя-дЛитёлШостй тактов, введены элем нты И и ИЛИ, триггер, кодопреобразователь , счетчик формирования дпитёльноЬтИ тагктов, группа входов которого соединена с группой выходов кодопреобразователя, дополнительный вход счётчика соединен с внешним входом управления микропроцессора и первым входом распределителя длительности тактов, а его выход подключен ко второму входу распределителя длительности тактов и к одному из счетных входов триггера, другой вход триггера соединен с выходом элемента И,первый вход которого соединен с выходом элемента ИЛИ, а второй вход соединен с выходом устройства синхронизации, группа выхЪдов шифратора гРУПп команд роединена с: группой входов элемента ИЛИ и с группой входов распределителя длительности тактов, дополнительный вход распределителя длительности тактотв соединен с выходом триггера и выходом микропроцессора, являющимся выходом управления синхронизацией, группа входом кодопреобразователя является группой входов микропроцессора, на которые принимается код длительности такта. Источники информации, принятые во внимание при экспертизе 1.Э,дёктроника, 1975, № 3, с. 33-35. 2.Электроника, 1976, № 17, С. 33-40 (прототип).

гд(

15

. .т

LJ.

. JC 77

Авторы

Даты

1979-10-25—Публикация

1977-04-04—Подача