(54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

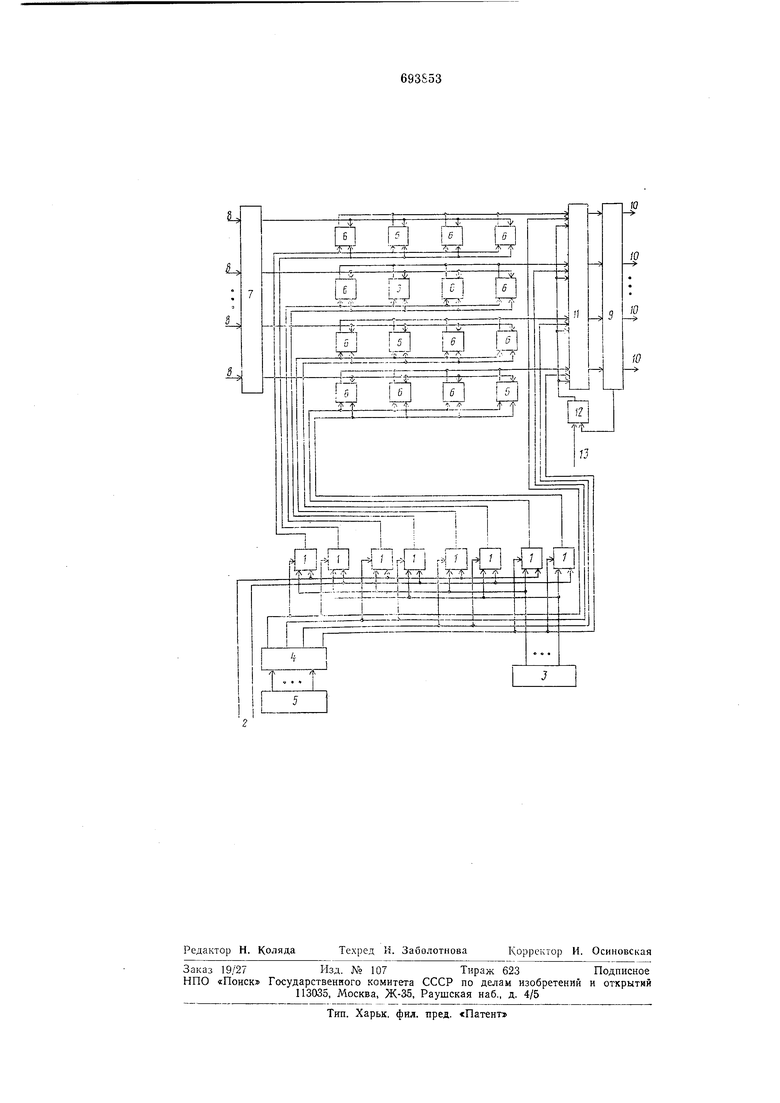

с выходов второго счетчика 5, нозбуждаст третьи входы двухканальных переключателей 1, в результате чего на первые входы соответствующих элементов 6 памяти, образующих один из разрядов запоминающего устройства, поступает код адреса регенерации, а на первые входы остальных элементов 6 памяти поступает код адреса обращения. В режиме записи код числа, поступающий по одним числовым щинам 8, преобразуется шифратором 7 в избыточный код числа, позволяющий исправить однократные и обнаруживать двойные ощибки (например, код Хэмминга). Поскольку во время цикла регенерации в элементы 6 памяти, в которых в данный момент времени осуществляется регенерация, занись инфоомации не происходит, то поступающий с выходов шифратора 7 избыточный код числа записывается только в те элементы 6 памяти, которые не участвуют в данный момент времени в регенерации, т. е. в элементы ( памяти, на первые входы которых поступает код адреса обрап ення. В результате п элемент 6 памяти по адресу обращения записывается избыточный код числа, в котором может быть один ошибочный разряд (это эквивалентно появлению однократной ошибки в записанном коде числа).

В режиме чтения избыточный код числа считывается из элементов 6 памяти на регистр И информации. При этом элементы 6 памяти, образующие один из разрядов заноминающего устройства, в котором при чтении происходит регенерация информации, могут либо совпасть, либо не совпасть с элементами 6 памяти, в которых регенерация информации происходила нри записи кода числа. В первом случае считанный избыточный код числа может содержать не более одного ошибочного разряда, а во втором случае - не более двух ошибочных разрядов. Дсщифратор 9 определяет количество ошибочных разрядов в считанном избыточном коде числа. Если код числа не содержит ошибочных позиций, то он выдается на другие числовые шины 10 без изменения. В этом случае, если считанный код числа содержит однократную ошибку, он корректируется дешифратором 9 и выдается далее на другие числовые шины 10. Если считанный код числа содержит двухкратную ошибку, то дешифратор 9 выдает сигнал двойной ошибки на первый вход элемента И. Стробирующий сигнал, поступающий на второй вход элемента И, разрещает прохождение сигнала двойной ошибки на третий вход регистра 11 информации, выполненного, например, на триггерах со счетным входом. При этом, поскольку на вторые входы регистра 11 информации с выходов первого дешифратора 4 поступает расшифрованный код адреса разряда регенерации запоминающего устройства при чтении, прохождение еигнала двойной ошибки на третьи входы регистра И информации приводит к инвертированию ошибочного разряда считанного кода числа по адресу, указанному дешифратором 4, т. е. происходит исправление одной ошибки и, следовательно, кратность ошибки уменьшается на единицу и становится равной единице. Далее избыточный

код числа с однократной ошибкой корректируется дешифратором 9 и выдается на вторые числовые шины 10, т. е. на выход запоминающего устройства.

Таким образом, по сравнению с известпым устройством, в котором иснользуются избыточный код, исправляющий минимум две ощибки, в нредлагаемом устройстве используются избыточный код, исправляющий одну и обнаруживающий две ошибки. Это

дает возможность при длине информационного слова, равной 64, уменьшить на 100% избыточность оборудования и потребляемую мощность и повышает надежноеть работы устройства, позволяя в то же время совмещать во времени циклы регенерации и обращения.

Формула изобретения

Динамическое запоминающее устройство, содержащее двухканальные переключатели, первые входы которых соединены с адресными шинами, вторые входы - с соответетвующими выходами первого счетчика, третьи входы через первый дешифратор, подключены к соответствующим выходам второго счетчика, выходы двухканальных переключателей соединены с нервыми входами элементов памяти, вторые входы которых через шифратор подключены к одним числовым шинам, второй дешифратор, выходы которого подключены к другим числовым шинам, отличающееся тем, что,

е целью повыщения надежности работы устройства, оно содержит регистр информации, элемент И и шину управления, первые входы регистра информации соединены с соответствующими выходами элементов

памяти, вторые входы - с выходами первого дешифратора, третьи входы через элемент И соединены с выходом второго дешифратора и шиной управления, а выходы подключены к соответствующим входам

второго дешифратора.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3760379, кл. 340-173, 1970.

2.Авторское свидетельство СССР по заявке № 2337573/18-24, кл. G И С 21/00, 24.03.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU705901A1 |

| Запоминающее устройство | 1979 |

|

SU873276A1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU701354A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

Авторы

Даты

1982-01-07—Публикация

1977-01-03—Подача