(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство | 1977 |

|

SU693853A1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU701354A1 |

| Запоминающее устройство | 1979 |

|

SU873276A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Запоминающее устройство | 1975 |

|

SU530351A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для регенерации информации в динамической памяти | 1979 |

|

SU771728A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

Изобретение относится к области вычислительной техники.

Известно запоминающее устройство (ЗУ) на динамических элементах IJ, недостатками которого являются наличие запретов по обращениям во время регенерации информации в элементах Памяти, низкая производительность работь и невысокое быстродействие.

Наиболее близким к предлагаемому устройству техническим решением является ЗУ, содержащее элементы памяти на динамических триггерах, первый счетчик, адресные шины, первые и вторые числовые шины 2.

Недостатками ЗУ являются наличие прерываний по обращениям для регенерации информации в элементах памяти, низкая производительность работы и невысокое быстродействие. Необходимость проведения циклов регенерации, во время которых запрещено обращение к элементам памяти, сильно сужает область применения устройства. В частности, затруднено использование устройства в вычислительных системах, работающих в реальном м.асштабе времени, хотя применение его в этих системах дало бы существенный выигрыш по ряду параметров, таких как быстродействие, мощность, надежность и габариты.

Цель изобретения - повысить быстродействие устройства.

Это достигается тем, что устройство содержит второй счетчик, дешифраторы, шифратор и двухканальные переключатели, первые входы которых соединены с адресными шинами, вторые входы - с выходами первого счетчика, третьи входы - через один дешифратор с выходами второго счетчика, выходы двухканальных переключателей соединены с первыми входами соответствующих элементов памяти, вторые входы которых через шифратор, а выходы через другой дешифратор подключены соответственно к первым и вторым числовым шинам. .

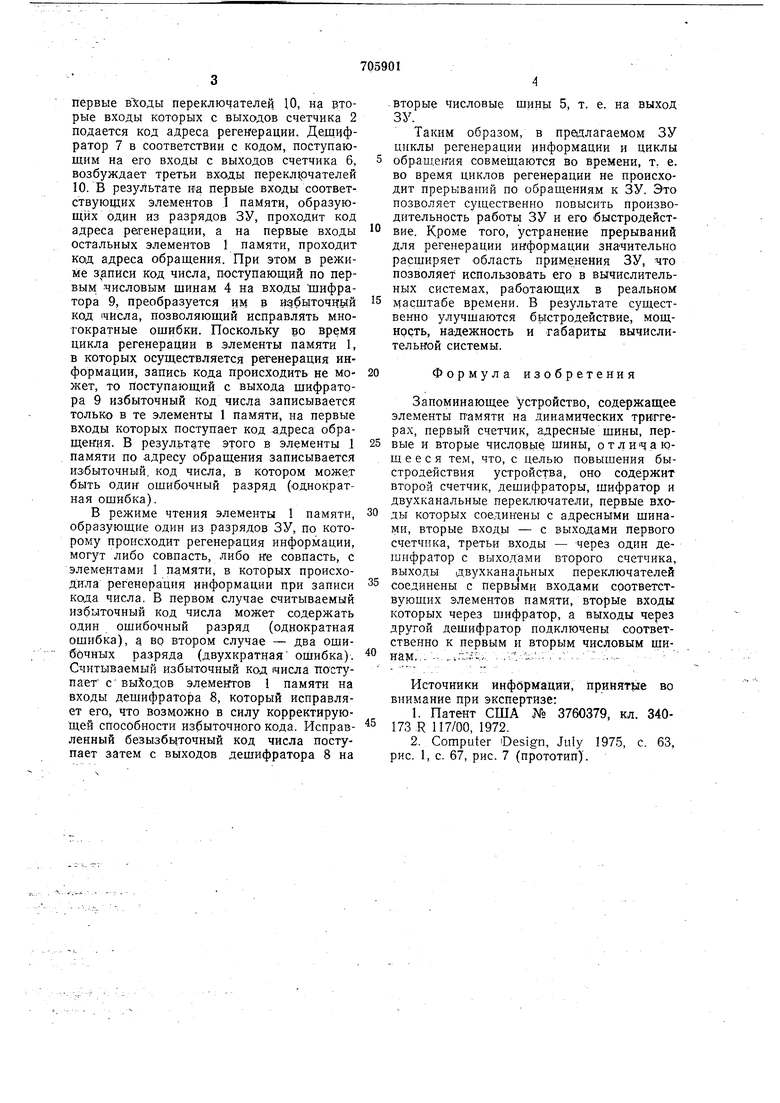

На чертеже приведена стрз ктурная схема устройства.

Устройство содержит элементы 1 памяти, первый счетчик 2, адресные шины 3, первые числовые шины 4, вторые числовые шины 5, второй счетчик 6, дешифраторы 7 и 8, шифратор 9 и двухканальные переключатели 10.

Устройство работает следующим образом.

Код адреса обращения (чтения или записи) поступает по адресным шинам 3 на первые в)соды переключателей Ш, на вторые входы которых с выходов счетчика 2 подается код адреса регенерации. Дешифратор 7 в соответствии с кодом, поступающим на его входы с выходов счетчика 6, возбуждает третьи входы перекл рчателей 10. В резу.льт:ате а первые входы соответствующих элементов I памяти, образующих один из разрядов ЗУ, проходит код адреса регенерации, а на первые входы остальных элементов 1 памяти, проходит код адреса обращения. При этом в режи1ле з,аписи код числа, поступающий по первым -числовым щинам 4 па входы шифратора 9, преобразуется им в избыточный код числа, позволяющий исправлять многократные ощибки. Поскольку во время цпкла регенерации в элементы памяти 1, в которых осуществляется регенерация информации, запись кода происходить не может, то Поступающий с выхода шифратора 9 избыточный код числа записывается только в те элементы 1 памяти, на первые входы которых поступает код адреса обращения. В результате этого в элементы 1 памяти по адресу обращения записывается избыточный, код числа, в котором может быть один ошибочный разряд (однократная ошибка). В режиме чтения элементы 1 памяти, образующие один из разрядов ЗУ, по которому происходит регенер ация информации, могут либо совпасть, либо не совпасть, с элементами I памяти, в которых происходила регенерация информации при записи кода числа. В первом случае считываемый избыточный код числа может содержать один ошибочный разряд (однократная ошибка), а BQ втором случае - два ошибочных разряда (двухкратная ошибка). Считываемый избыточный код числа тгаступает с выходов элементов 1 памяти на входы дешифратора 8, который исправляет его, что возможно в силу корректирующей способности избыточного кода. Исправленный безызбщточный код числа поступает затем с выходов дешифратора 8 на вторые числовые шинь 5, т. е. на выход ЗУ. Таким образом, в предлагаемом ЗУ циклы регенерации информации и циклы обращения совмещаются во времени, т. е. во время циклов регенерации не происходит прерываний по обращениям к ЗУ. Это позволяет существенно повысить производительность pa6oTbii ЗУ и его быстродействие. Кроме того, устранение прерываний для регенерации информации значительно расширяет область применения ЗУ, -что позволяет использовать его в вычислительных системах, работающих в реальном масщтабе времени. В результате существенно улучщаются бьтстродействие, мощность, надежность и габариты вычислительной системы. Формула изобретения Запоминающее устройство, содержащее элементы памяти на динамических триггерах, первый счетчик, адресные щины, первые и вторые числовые щипы, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит второй счетчик, дешифраторы, шифратор и двухканальные переключатели, первые входы которых соединены с адресными шинами, вторые входы - с выходами первого счетчика, третьи входы - через один де1иифратор с выходами второго счетчика, выходы двухканальных переключателей соединены с первыми входами соответствующих элементов памяти, вторые входы которых через шифратор, а выходы через другой дешифратор подключены соответственно к первым и вторым числовым шинам...-... ,v:----:;...v,-.:,.:-;.-.- Источники информации, принятые во внимание прн экспертизе: 1.Патент США №. 3760379, кл. 340173 R 117/00, 1972. 2.Computer Design, July 1975, с. 63, рис. 1, с. 67, рис. 7 (прототип).

Авторы

Даты

1982-01-07—Публикация

1976-03-23—Подача