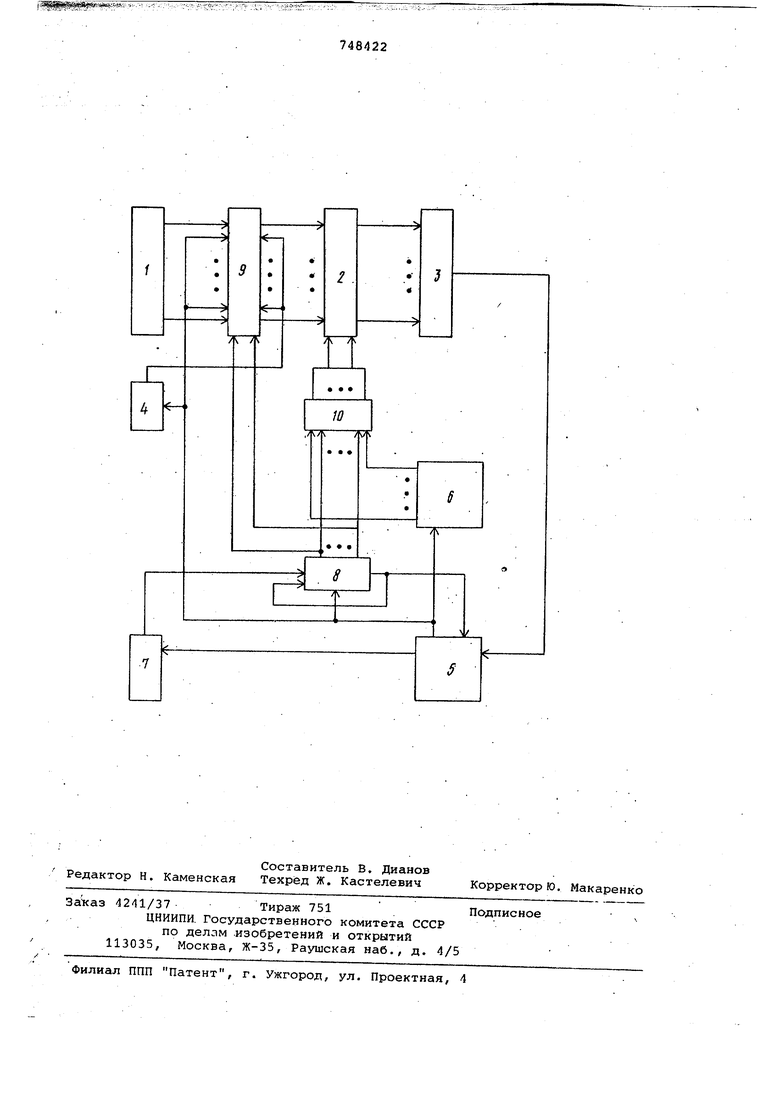

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ 1 I . Изобретение относится к области вычислительной техники и может быть применено для контроля интегральных схем (ис). Известно устройство для контроля интегральных схем 1 , которое обеспечивает контроль интегральной схемы (ис) с проверкой наличия контакта зондов-щупов и ИС при контроле на пластинах. Недостатком такого устройства является отсутствие возможности проверить наличие замыкания двух соседних зондов и отсутствие автоматического контроля порогов амплитудных дискриминаторов, с помощью .которых осуществляетёя разбраковка интегральных схем. Известно также устройство для к троля интегральных схем 2, которое осуществляет контроль замыкани двух соседних выводов ИС или зондо шупов при контроле на пластинах, но вэтом устройстве необходимо по давать напряжение, противоположное по полярности напряжению питания интегральной схемы, что приводит к ,применению электромагнитных реле и увеличивает емкость измерительной цепи. Недостатком данного устройства является отсутствие возможности автоматического самоконтроля измерительных цепей. Наиболее близким по технической сущности к данному изобретению является устройство для контроля , содержащее два электронных ключа, два триггера, многоканальный амплитудный дискриминатор, элемент ИЛИ, два элемента И, блок управления. Недостатком этого устройства является отсутствие возможности контролй порогов амплитудных дискриминаторов и проверки замыкания двух соседних зондов, что не дает достаточной достоверности контроля. Целью изобретения является повышение достоверности контроля интегральных схем. Поставленная цель достигается тем, что в устройство для контроля интегральных схем, содержащее последовательно соединенные многоканальный амплитудный дискриминатор, первый элемент ИЛИ, блок управления и генератор тактовых импульсов, причем второй выход блока управления подключей ко входам блока памяти и про грамиируемого источника питания, вв дены блок ключей и последовательно сЬёдйненные кольцевой регистр сдвиг и блок вторых элементов ИЛИ, выходы которого подключены к задающим входам многоканального амплитудного дискриминатора, а вторые входы к выходам блока памяти, выходы блока ключей соединены с измерительными входами многоканального амплитудного дискриминатора, задающие входы - с выходом программируемого исто ника питания, первые управляющие входы - с выходами кольцевого .регистра сдвига, а вторые управляющ входы - со вторым выходе блока упр ления и со входом записи кольцевого регистра сдвига, соединенного такто вым входом с выходом генератора так товых импульсов, а выходом старшего разряда - со вторым входом блока управления. На чертеже представлена блок-схе ма устройства. На чертеже изображена интегральная схема 1, многоканальный амплитудный дискриминатор 2, первый элемент ИЛИ 3, программируемый источни питания 4, блок управления 5, блок памяти 6, генератор тактовых импуль сов 7, регистр сдвига 8, блок ключе 9 и блок вторых элементов ИЛИ 10. Устройство работает в четырех режимах. Первый режим - поиск возможных замыканий зондов-щупов при контроле на пластинах. Второй режим - раэбра кова ИС, третий режим - контроль ко тактирования, а четвертый - проверка порогов многоканального амплитуд ного дискриминатора. При поиске возможных замыканий зондов ЙС 1 не подключена и устройство работает следующим образом. Блок управления 5 записывает в п вый разряд регистра 8 единицу, в остальные - нули. При этом на вход блока 9 подается сигнал включения с блока управления 5. На других входах блока 9 только на одном будет сигнал включения, на других будет запрет. Через задающий вхоД блока 9 с источн 1ка 4 поступает выс кий потенциал только на один вход, дискриминатора 2, если нет корочени с соседним зондом. В этом случае в тот же канал дискриминатора 2 пос 1 Упает сигнал ожидания единица с выхода регистра 8 через блок 10. На выходе дискриминатора 2 не поя)вится сигнала брак. В случае корочения двух зондов (даже не соседних) или большего количества с этим зондом на выходе дискриминатора 2 появится брак на выходе тех каналов, зонды которых замыкают с выбранным зондом, номер которого фиксируется

748422 регистром 8. На блок 5 поступает сигнал сбой с выхода элемента ИЛИ 3. Оператор исправляет корочение и осуществляет повторный запуск данного режима. С генератора 7 сигнал поступит на вход регистра 8, в котором произойдет перемещение бди- ницы из первого разряда во второй. При этом произойдет проверка на замыкание второго зонда с остальными зондами и т. д. до последнего зонда. Перенос единицы из старшего разряда регистра 8 в. первый фиксирует окончание первого режима и отсутствие замыканий между зондами. При контроле на функционирование блок управления 5 записывает в регистр сдвига 8 нули во все разряды, источник 4 отключается от измерительных цепей. Ожидаемые комбинации поступают из блока памяти 6 через блок 10 на задающий вход дискриминатора 2. Выходы ИС 1 через блок ключей 9 подключены ко входам дискриминатора 2. Функциональный контроль ИС произ водится следующим образом. Выход с ИС 1 поступает на дискриминатор 2, где происходит сравнение с ожидаемыми комбинациями, поступающими с блока 10. Сигнал несравнепия, если он возникает, с выхода дискриминатора 2 через элемент ИЛИ 3 поступит на вход блока 5, фиксируя брак по данной ИС. При контроле контактирования зондов к контактным площадкам ИС 1 в регистр 8 записывается единица из блока 5 в разряд, соответствующий подложке ИС 1. В этом случае на площадку ИС 1 с источника 4 поступает напряжение через блок 9. Если контактирование не осуществлено всеми зондами, то на выходах дискриминатора 2 появится сигнал несравнения, который зафиксируется блоком 5 через элемент ИЛИ 3. Если же контактирование есть, то контроль контактирования заканчивается. При проверке порогов дискриминатора 2 источник 4 подключается через блок ключей 9 последовательно один за другим ко входам дискриминатора 2 за счет перемещения единицы в регистре сдвига 8 от тактовых импульсов, поступающих с генератора 7. Такой перебор каналов осуществляется четыре раза, каждый раз изменяя напряжение на источнике 4. Вначале напря ПОРОГЛ (О) жение выставляется U л , где Unopora (о), -порог нуля дискриминатора 2, л -максимально допустимая погрешность измерения сигнала при и„орогс«(о)Затем выставляется напряже.ние порога (о) + . В первом случае ни один из каналов дискриминатора 2 не должен браковаться. Во втором случае ни один из каналов дискриминатора 2 не должен показать сигнала годен. Сигналы брак и годен фиксируются каждый раз раздельно . по каждому каналу, поэтому неисправ ность идентифицируется автоматически. Аналогично проверяется порог единицы на напряжениях УЗ Uпорога( i и U, «rUnoporaUyb Д При и J блок управления 5 не должен Зафиксироват сигнала годен, а приу. -сигнала брак. Если в четвертом режиме выполняются правильно все четыре случая, то пороги дискриминатора 2 выставлены верно. В противном случае фиксируется неисправность для оператор который принимает меры для устранения выявленной неисправности. Таким образом применение данного устройства обеспечит расширение фун циональных возможностей (возможность обнаружения замыкания любых зондов), повысит достоверность кон троля (автоматический контроль поро гов многоканального амплитудного дискриминатора), что позволит увеличить процент выхода годных- схем, увеличить производительность устрой ства контроля интегральных схем. Формула изобретения Устройство для контроля интеграл ных схем, содержащее последовательно соединенные многоканальный амплитудный дискриминатор, первый эле мент ИЛИ, блок управления и генератор тактовых импульсов, причем второй выход блока управления подключен ко входам блока памяти и программируемого источника питания, от л ичающееся тем, что, с целью повышения достоверности контроля, в него введены блок ключей и последовательно соединенные кольцевой регистр сдвига и блок вторых элеfkieHTOB ИЛИ, выходы которого подключены к задающим входам многоканального амплитудного дискриминатора, а вторые входы - к выходам блока памяти, выходы блока ключей соединены с измерительными входами многоканального амплитудного дискриминатора, задающие входы - с выходом программируемого источника питания, первые управляющие входы - с выходами кольцевого регистра сдвига, а вторые управляющие входы - со вторым выходом блока управления и со входом записи кольцевого регистра сдвига, соединенного тактовым входом с выходом генератора тактовых импульсов, а йыходом старшего разряда - со вторым входом блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 472346, кл. G Об F 11/00, 1972. 2.Авторское свидетельство СССР 531104, кл. G 01 R 31/02, 1975. 3.Авторское свидетельство СССР по заявке № 2428043/18-24, кл. G Об F 11/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

| Устройство контроля интегральных схем | 1982 |

|

SU1049838A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Устройство контроля интегральных схем | 1975 |

|

SU532830A1 |

| Устройство контроля интегральных схем | 1987 |

|

SU1430914A1 |

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

| Устройство параметрического контроля интегральных схем | 1985 |

|

SU1287060A1 |

Авторы

Даты

1980-07-15—Публикация

1978-05-17—Подача