1

Изобретение относится к связи и может использоваться для синхронизации и фазирования местных генераторов приемников систем связи.

Известно устройство синхронизации, содержащее опорный генератор, формирователь импульсов, элементы И и И-НЕ и последовательно соединенные делитель частоты и дискриминатор знака рассогласования .

Однако известное устройство имеет недостаточную точность синхронизации.

Целью изобретения является повышение точности синхронизации.

Для этого в устройство синхронизации, содержащее опорный генератор, формирователь импульсов, элементы И и И-НЕ и последовательно соединенные делитель частоты и дискриминатор знака рассогласования, введены блок управления и (и+1) разрядный регистр сдвига, при этом выходы трех последних разрядов («+) разрядного регистра сдвига через блок управления подключены к первому входу первого разряда, к второму входу которого подключен выход второго разряда («+1) разрядного регистра сдвига, а выходы первого разряда () разрядного регистра сдвига подключены соответственно к входу делителя частоты и к первому входу

формирователя импульсов, второй вход которого объединен с соответствующим входом дискриминатора знака рассогласования, выходы которого подключены соответственно к первым входам элементов И и И-НЕ, два других входа которых объединены между собой попарно и подключены к соответствующим выходам формирователя импульсов, выход элемента И подключен к соответствующему входу блока управления и к соответствующему входу (п+1) разряда (л+1) разрядного регистра сдвига, а выход элемента И-НЕ подключен к соответствующим входам блока управления и «п разряда (л+1) разрядного регистра сдвига, к тактовым входам (л+1) разрядов которого подключены выход опорного генератора.

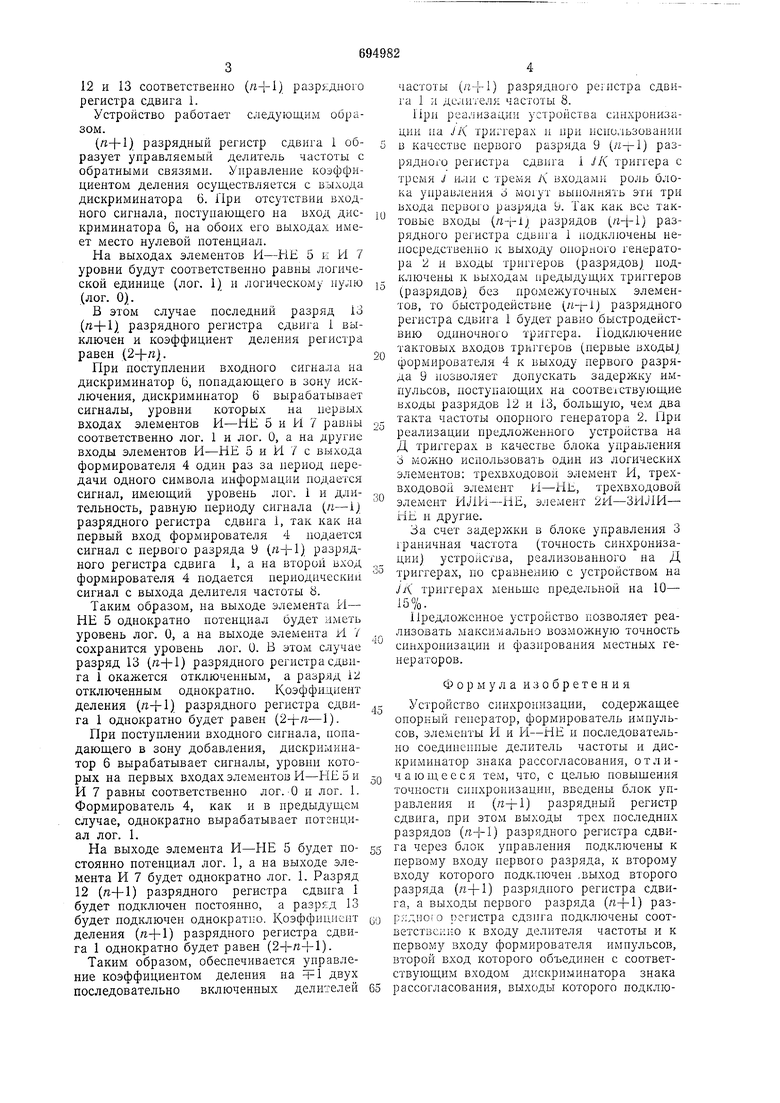

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство синхронизации содержит («+) разрядный регистр сдвига 1, опорный генератор 2, блок управления 3, формирователь 4 импульсов, элемент 5, дискриминатор 6 знака рассогласования, элемент И 7 и делитель частоты 8.

На чертеже показаны также первый и второй разряды 9 и 10 соответственно и три последних разряда («-1) и («-f 1) И, 12 и 13 соответственно (n+l) разрядного регистра сдвига 1. Устройство работает следующим образом. (л+1) разрядный регистр сдвига 1 образует управляемый делитель частоты с обратными связями. Управление коэффициентом деления осуществляется с выхода дискриминатора 6. При отсутствии входного сигнала, поступающего на вход дискриминатора 6, на обоих его выходах имеет место нулевой потенциал. На выходах элементов И-НЕ 5 и И 7 уровни будут соответственно равны логической единице (лог. 1) и логическому нулю (лог, OJ. В этом случае последний разряд 13 (n+l) разрядного регистра сдвига 1 выключен и коэффициент деления регистра равен .(2-fn}. При посту-плении входного сигнала на дискриминатор 6, попадающего в зону исключения, дискриминатор 6 вырабатывает сигналы, уровни которых на первых входах элементов И-НЕ 5 и И 7 равны соответственно лог. 1 и лог. О, а на другие входы элементов И-НЕ 5 и И 7 с выхода формирователя 4 один раз за период передачи одного символа информации подается сигнал, имеющий уровень лог. 1 и длительность, равную периоду сигнала (п-1} разрядного регистра сдвига 1, так как на первый вход формирователя 4 подается сигнал с первого разряда 9 (rt+l) разрядного регистра сдвига 1, а на второй вход формирователя 4 подается периодический сигнал с выхода делителя частоты 8. Таким образом, на выходе элемента И- НЕ 5 однократно потенциал будет иметь уровень лог. О, а на выходе элемента И 7 сохранится уровень лог. 0. В этом случае разряд 13 (д+1) разрядного регистра сдвига 1 окажется отключенным, а разряд 12 отключенным однократно. Коэффициент деления («+). разрядного регистра сдвига 1 однократно будет равен (2-f-n-1). При поступлении входного сигнала, попадающего в зону добавления, дискриминатор 6 вырабатывает сигналы, уровни которых на первых входах элементов И-НЕ 5 и И 7 равны соответственно лог. О и лог. 1. Формирователь 4, как и в предыдущем случае, однократно вырабатывает потенциал лог. 1. На выходе элемента И-НЕ 5 будет постоянно потенциал лог. 1, а на выходе элемента И 7 будет однократно лог. 1. Разряд 12 (л+1) разрядного регистра сдвига 1 будет подключен постоянно, а разряд 13 будет подключен однократно. Коэффициент деления () разрядного регистра сдвига 1 однократно будет равен ()Таким образом, обеспечивается управление коэффициентом деления на +1 двух последовательно включенных делителей частоты {я-f 1) разрядного регистра сдвига 1 и делителя частоты 8. При реализации устройства синхронизации на У/С триггерах и при использовании в качестве первого разряда 9 («+) разрядного регистра сдвига 1 JK. триггера с тремя / или с тремя /С входами роль блока управления 6 могут выполнять эти три входа первого разряда 9. Так как все тактовые входы (п+1) разрядов («+) разрядного регистра сдвига 1 подключены непосредственно к выходу опорного генератора 2 и входы триггеров (разрядов) подключены к выходам предыдущих триггеров (разрядов) без промежуточных элементов, то быстродействие (.n+l) разрядного регистра сдвига 1 будет равно быстродействию одиночного триггера. Подключение тактовых входов триггеров (первые входы) формирователя 4 к выходу первого разряда 9 позволяет допускать задержку импульсов, поступающих на соответствующие входы разрядов 12 и 13, большую, чем два такта частоты опорного генератора 2. При реализации предложенного устройства на Д триггерах в качестве блока управления 3 можно использовать один из логических элементов: трехвходовой элемент И, трехвходовой элемент И-НЕ, трехвходовой элемент ИЛИ-НЕ, элемент 2И-ЗИЛИ- НЕ и другие. За счет задержки в блоке управления 3 граничная частота (точность синхронизации) устройства, реализованного на Д триггерах, по сравнению с устройством на JK триггерах меньше предельной на 10- 15%. Предложенное устройство позволяет реализовать максимально возможную точность синхронизации и фазирования местных генераторов. Фор мул а изобретения Устройство синхронизации, содержащее опорный генератор, формирователь импульсов, элементы И и И-НЕ и последовательно соединенные делитель частоты и дискриминатор знака рассогласования, отличающееся тем, что, с целью повышения очности синхронизации, введены блок управления и (tt+1) разрядный регистр двига, при этом выходы трех последних азрядов (п+1) разрядного регистра сдвиа через блок управления подключены к ервому входу первого разряда, к второму ходу которого подключен .выход второго азряда (п+1) разрядного регистра сдвиа, а выходы первого разряда (и-fl) разядного регистра сдвига подключены соотетственно к входу делителя частоты и к ервому входу формирователя импульсов, торой вход которого объединен с соответтвующим входом дискриминатора знака ассогласования, выходы которого подключены соответственно к первым входам элементов И и И-НЕ, два других входа которых объединены между собой попарно и подключены к соответствующим выходам формирователя импульсов, выход элемента И подключен к соответствующему входу блока управления и к соответствующему входу (п+1) разряда (n+l) разрядного регистра сдвига, а выход элемента И-НЕ

подключен к соответствующим входам блока управления и п разряда («+) разрядного регистра сдвига, к тактовым входам (л+1) разрядов которого подключен выход опорного генератора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 478451, кл. Н 04L /02, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1979 |

|

SU873440A1 |

| Устройство синхронизации | 1981 |

|

SU1125759A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1338094A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1099403A1 |

Авторы

Даты

1979-10-30—Публикация

1977-09-28—Подача