(54) СУММИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования одноразрядных приращений | 1985 |

|

SU1251072A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Суммирующее устройство | 1977 |

|

SU708349A1 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Сумматор в избыточной двоичной системе счисления | 1982 |

|

SU1042011A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

I

Предпопагаемое изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах и устройствах.

Известны вычислительные устройства для суммирования чисел в тернарных кодах 1.

Однако в этих устройствах используется большое количество оборудования.

Наиболее близким по технической сущности к предложенному является суммирующее устройство, содержащее два элемента И и два триггера, прямые выходы которых соединены с первыми входами соответственно первого и второго элементов И 2,

Однако эти устройства требуют также больщого количества оборудования,

Пель изобретения - упрощение устройства.

Это достигается тем, что устройство содержит два одноразрядных двоичных сумматора, входы первого из которых

подключены к щинам положительных приращений входных аргументов устройства и выходу первого элемента И, а входы второго - к шинам отрицательных приращений входных аргументов устройства и выходу второго элемента И. Выходы сумм первого и второго одноразрядных двоичных сумматоров подключены ко входам соответственно первого и второго триггеров, инверсные-ВЫХОДЫ которых подключены ко вторым входам соответственно второго и первого элементов И, Выходы переносов одноразрядных двоичных сумматоров соединены с выходными щинами устройства.

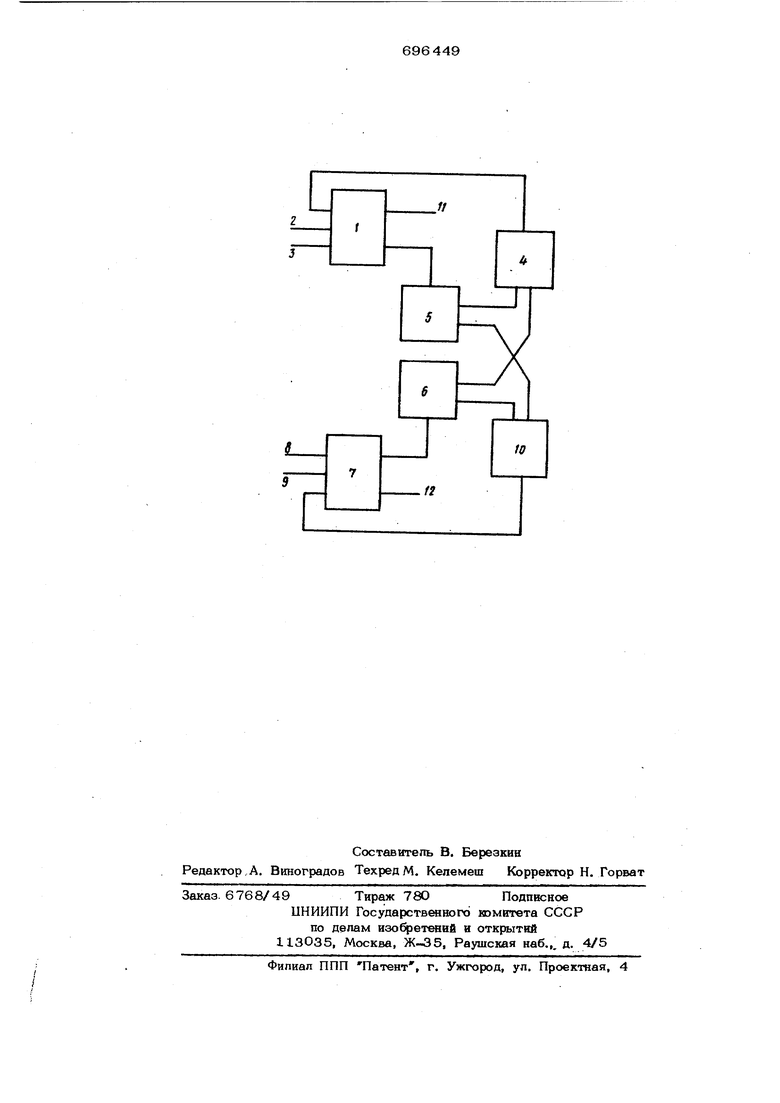

Функциональная схема суммирующего устройства приведена на чертеже,

Суммируклцее устройство содержит одноразрядный двоичный сумматор I, шины положительных приращений входных аргументов 2 и 3, элемент И 4, Д-триггеры 5 и 6$ одноразрядный двоичный сумматор 7, шины отрицательных приращений входных аргументов 8 и 9,

элемент И 10, выходные шины устройатва II и 12. Входы сумматора 1 соединены с шинами 2 и 3 положительных приращений входных аргументов и выходом элемента И 4, входы которого подг ключены к прямому выходу триггера 5 и инверсному выходу триггера 6, Входы сумматора 7 соединены с шинами 8 и 9 отрицательных приращений входных аргументов и выходом элемента И 10, входы которого подключены к прямому выходу триггера 6 и инверсному выходу триггера 5. Выходы сумм сумматоров 1 и 7 подключены ко входу соответственно триггеров 5 и 6, а выходы переносов - к выходным шинам tl и 12 устройства.

Устройство работает следуйшим образом.

По шинам 2 и 3, 8 и 9 поступают суммируемые величины (приращения). Для кодирования приращений используется тернарный способ, т.е. -приращение передается по двум каналам. Один канал для передачи положительных приращений, второй - отрицательных. Одновременное появление сигналов в обоих каналах исключено. По шинам 2 и 3 подаются положительные приращения первого (а) и второго (в) входных аргументов, а по щинам 8 и 9 -отрицательные приращения этих же аргзгментов. Если на входы устройства поступаю положительные приращения обоих слагаемых (т.е. возникают сигналы на щинах 2 и 3), то сумматор I выдает сигнал переноса, который подается на выходную щину 11 устройства. Если на входы устройства поступают положительные приращения одного из слагаемых, а приращения второго слагаемого равны нулю (т.е. сигналы возникают или на шине 2,. или ва шине 3), то сумматор 1 выдает сигнал суммы, который заносится в триггер 5. На щину II устройства приходит только каждое второе положительное приращение. Если на входы устройства приходят отрицательные приращения обоих слагаемых (т.е. сигналы возникают на щинах 8 и 9), сумматор 7 выдает сигнал переноса, который поступает на выходную щину 12 устройства. Если же отрицательные приращения поступают только на один вход устройства (по щине 8 или по шине 9), а на других входах приращения отсутствуют, то на шину 12 проходит каждое второе отрицательное приращение. Если

же на один вход устройства поступает положительное приращение, а на другой отрицательное (сигнал возникает на шинах 2 и 9 или на щинах 3 и 8), или же

поступают одиночные положительные и отрицательные приращения последовательно друг за другом, то на щинах II и 12 сигнал равен нулю, так как одиночные отрицательные и положительные

приращения взаимно компенсируются

элементами И 4 и 10. На выходных щинах 11 и 12 устройства будет сформирована полусумма двух входных аргументов, и т.е. повышена разрядность суммы

входных аргументов. Количество оборудования в предложенном устройстве сокращено по сравнению с известными суммируклпими устройствами и одновременно повышено быстродействие устройства,

0 так как задержка сигнала tTi, в устройстве определяется задержкой только одного элемента ZT (сумматора), в то время как в известных суммирующих устройствах задержка сигнала определяется задержкой не менее трех элементов, т.е. СдФормулаизобретенияСуммирующее устройство, содержащее два элемента И и два триггера, прямые выходы которых соединены с первыми входами соответственно первого и второго элементов И, о т л и чающееся тем, что, с целью упрощения устройства, оно содержит два одноразрядных двоичных сумматора, вхо, ды первого из которых подключены к щинам положительных приращений входных аргументов устройства и выходу д первого.элемента И, а входы второго к щинам отрицательных приращений входньк аргументов устройства и выходу второго элемента И, выходы сумм первого и второго одноразрядных двоичных - сумматоров подключены ко входам соот- ветственно перво Р и второго триггеров, инверсные выходы которьк подключены ко вторым входам соответственно второго и первого элементов И,а выходы пеP реносов одноразрядных двоичных сумматоров соединены с выходными шинами Згстройства.

Источники информации, принятые во внимание при экспертизе

f2

Авторы

Даты

1979-11-05—Публикация

1977-09-12—Подача