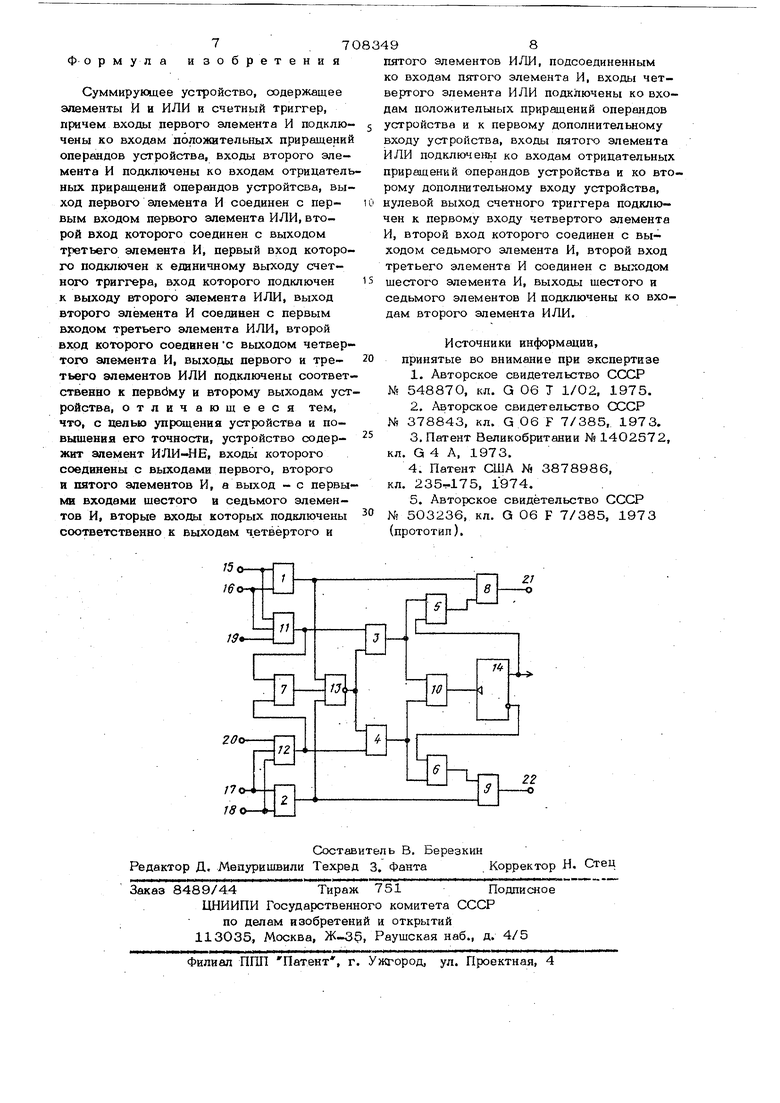

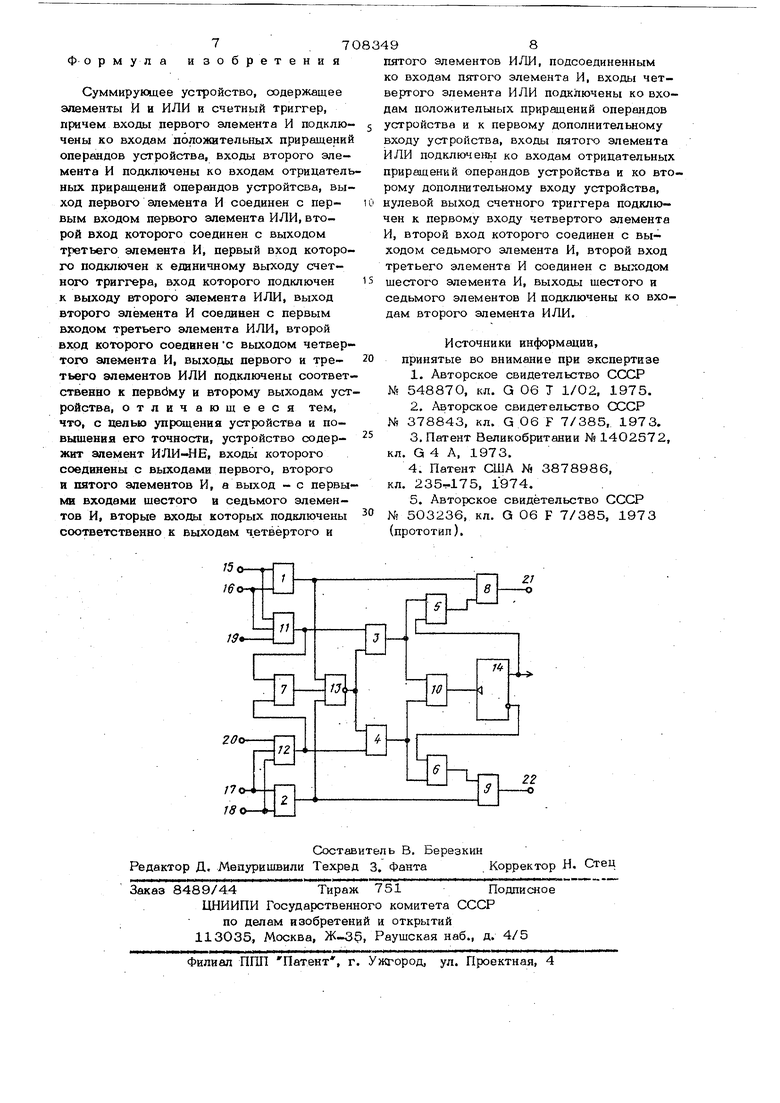

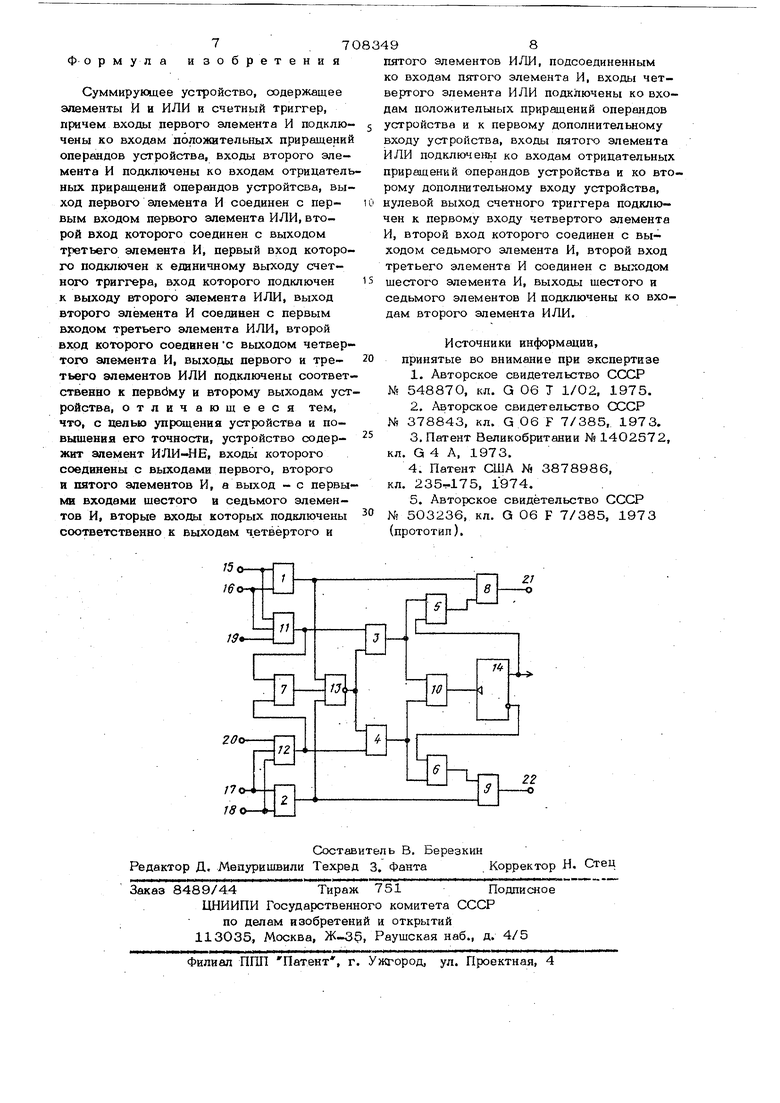

Изобретение относится к вычислительной технике, в частности к суммирующим устройствам, и может быть использовано для построения вычислитель{ ых устройств работа которых основана на принципах Циф рового интегрирования. Оуммирующие устройства широко из вестны. Однако известные устройства либ сложны, либо работают по параллельным или последовательным кодам чисел, что препятствует их использованию в устройствах цифрового интегрирования, в которых операнды вырабатываются в число им пульсных (унитарных) кодах l,2|, . Из известных устройств наиболее близким по технической сущности к данному изобретению является суммирующее устро clTBO, содержащее элементы И и ИЛИ и счетный триггер, причем входы первого элемента И подключены ко входам положительных приращений операндов устройства, входы второго элемента И подключены ко входам отрицательных приращений операндов устройства, выход первого эле- ента И соединен с первым входом первого эпе мента ИЛИ, второйвход которого соединен с выходом третьего элемента И, первый вход которого подключен к единичному выходу счетного триггера, вход которого подключен к выходу второго элемента И ЛИ, выход второго элемента И сояпинвн с пер&ым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, выходы первого и третьего элементов ИЛИ подключены соответственно к первому и второму выходам устройств а б. Это устройство по потоку приращений первого слагаемого а и потоку приращений второго-слагаемого Ь формирует поток приращений, соответствующий величине. ). Однако указанное устройство является довольно сложным, так как при его построении не достаточно полно использованы принципы суперпозиции логических функций, что, в частности, привело к наличию в устройстве трех логических каналов, уп равляющих работой четырех трехвходовых элементов И и двух триггеров, которые являются источниками дополнительной информации о младшем двоичном разряде суммы О+Ъ , использовать которую в рамках данного устройства трудно, потому - что для этого потребовался бы источник импульса конуса потоков приращений слагаемых о и Ь, поступаюцих через суммирующее устройство на входы реверсивного счетчика, а также дешифратор состояний триггеров суммирующего устройства и знакового разряда реверсивного счетчика.. Целью изобретения является упрощение устройства и повышение его точности. Для достижения поставленной цели, уст ройство содержит элемент ИЛИ-НБ, входы которого соединены с выходами перво го,второго в пятого элементов И, а выход - с первыми входами шестого и седь мого элементов И, вторые входы которых подключены соответственно к выходам че вертого в пятого элементов. ИЛИ, подсоединенным ко входам пятого элемента И, входы четвертого элемента ИЛИ подключен ко входам положительных приращений операндов устройства и к первому дополнительному входу устройства, входы пято го элема1та ИЛИ подключены ко входам отрицательных приращений операндов устройства и ко второму дополнительному входу устройства, нулевой выход счетного триггера подключен к первому входу четвертого элемента И, второй вход кото рого соединен с выходом седьмого элеме та И, второй вход третьего элемента И соединен с выходом шестого элемента И, выходы шестого и седьмого элементов И подключены ко входам второго элемента ИЛИ. Для пояснения сущности изобретения на чертеже приведена схема суммирующего устройства, содержащая семь двухвходовых элементов И 1, 2, 3, 4, 5, 6 и 7, три двухвходовых 8, ЭиЮидва трехвходоБых 11 и 12 элементов ИЛИ, трехвходовый элемент ИЛИ-НЕ 13, счетный триггер 14, входы 15 и 16 полоаштельных приращений первого и второго слагаемых, соеданенные соответственно с первыми и вторыми входами элементов 1 и 11, входы 17 и 18 отрицательных приращений первого и второго слагаемых, соответственно соединенные с первыми и вторыми входами элементов 2 и 12, дополнительные входы 19 и 20, характериз кхцие смену знака суммы соответственно с - на + и с + на - (выходы задержанных импульсов переполнения реверсивного счетчика суммы первого и второго слагаемых) и подключенные соответственно к третьему входу элемента 11 и третьему входу элемента 12, при этом выход элемента 1 соединен с первыми входами элементов 8 и 13, выход элемента 2 соединен с первым входом элемента 9 и третьим входом элемента 13, второй вход которого через элемент 7 связан с выходом элемента 11, подключенным к первому входу элемента 3, и с выходом элемента 12, подключенным к первому входу элемента 4, второй вход которого соединен со вторым входом элемента 3 и подключен к выходу элемента 13, выход элемента 3 соединен с первым входом элемента 5 и одним из входов элемента 10, другой вход которого соединен свыходом элемента 4, подключенным к первому входу элемента б, второй вход элемента 5 соединен с прямым выходом, а второй вход элемента .6 с инверсным выходом триггера 14, счетный вход которого подключен к выходу элемента 10, причем выход элемента 6 подключен ко второму входу элемента 8, а выход элемента 6 - ко второму входу элемента 9, выход элемента 8 соединен с выходом 21 положительных приращений, а выход элемента 9 - с выходом 22 отрицательных приращений суммы слагаемых. Устройство работает следующим образом. На входы 15-fl8 поступают суммируемые величины (приращения). Для кодирования приращений используется тернарный способ, т.е. приращение передается по двум каналам. Один канал служит для передачи положительных приращений, второй - отрицательных. На вход 15 и вход 17 поступают соответственно положительное и отрицательное приращения первого слагаемого а а на вход 16 и вход 18 - положительное и отрицательное приращения второго слагаемого Ь. Приращения слагаемых на входах устройства представлены в виде последовательностей импульсов. Причем одновременное появление приращеНИИ (импульсов) на входах 15 и 17 или входах 16 и 18 невозможно. Так как описываемое устройство обычно работает на реверсивный счетчик, то на вход 19 (20) устройства поступает задержанный импульс переполнения реверсивного счетчика, характеризующий смену знака суммы, соответствующей переходу его состояния -О в +0 С+О в -О).При отсутствии на входах 15-18 устройства импульсов приршцений с выходов элементов I7l2 снимаются сигналы логи- ческих нулей, а с выхода элемента 13 - сигнал логической единицы, активизирующий по вторым входам элементы И 3 и 4. При этом триггер 14 активизирует по второму входу элемент И 5 и запрещает по одноименному входу элемент И 6, если он находится в единичном состоянии, и наоборот - если находится в нулевом состоянии. Пусть на входы устройства одновременно поступают положительное приращение одного из слагаемых и отрицательное приращение другого слагаемого, т.е. на входах 15 и 18 или входах 16 и 17 одновременно возникают импульсы. Тогда эти импульсы одновременно 1ЮЯВЯТСЯ на выходах элементов ИЛИ 11 и 12, подклю ченных ко входам элемента И 7. На выходе элемента И 7 вырабатывается импульс, который через элемент ИЛИ-НЕ 13 запретит по вторым входам работу элемен та И 3 и 4. Поэтому на выходах 21 и 22 импульсы не вырабатываются. Пусть на входы 15 и 16 (17 и 18) одновременно поступают положительные (отрицательные) приращения слагаемых а и Ъ. Тогда на выходах элементов .И 1 и ИЛИ 11 (И 2 и ИЛИ 12) одновре менно будут выработаны импульсы. Импульс с выхода элемента И 1 (И 2) через элемент ИЛИ-НЕ 13 запретит по вто рымвходам элементы И 3 и 4 и поступит через элемент ИЛИ 8 (ИЛИ 9) с выхода 21 положительного (22 отрицательного), приращения суммы на суммирующий (вычитающий) вход реверсивного счетчика, на которь1й работает описываемое устройство. При этом, если реверсивный счетчик в этот момент находится в состоянии -О (+0), то на его выходе, подключенном к входу 19 (20), будет вьфаботан задержанный импульс переполнения импульса на вход 19 (2О) устройства. на его других входах импульсы будут отсутствовать и реверсивный счетчик уста- носится в состояние +0 (-О). Импульс со входа 19 (2О) поступает, через элемент ИЛИ 11 (ИЛИ 12) на пер вый вход элемента И 3 (И 4). Так как по вторым входам элементы И 3 и 4 раз решены сигналом логической единицы,- вы рабатываемым элементом ИЛИ-НЕ, то на выходе элемента ИЗ (И 4) появится им- пульс, поступающий через элемент ИЛИ 10 на счетный вход триггера 14, При этом, если триггер 14 находится в единичи (нулевом) состоянии, то он разреша- ет по второму входу элемента И 5 (И б), на первый вход которого с выхода элемента И 3 (И 4) поступает импульс, который поступит через элемент ИЛИ 8 (ИЛИ 9) с выхода 21 положительного (22 отрицательного) приращения суммы на суммиру ющий (вычитающий) вход реверсивного счетчика. После окончания этого импуль- с.а реверсивный счетчик перейдет в состоние (-1), а-триггер 14 устаноится в О (1), А если триггер 14 находится в нулевом (единичном) состоянии, то реверсивный счетчик остается в состоянии О (-О) в триггер 14 усггановится в состояние 1 (О). Таким образом на выходе 21 устройства формируется поток положительных, а на выходе 22 - поток отрицательных приращений величины 1/2 (а +Ь). Кроме того, при поступлении потоков прироце- НИИ слагаемых О и b через предлагаемое устройство на реверсивный счетчик, триггер 14 вырабатывает младший двоичный разряд суммы (Qvb ). Причем легко показать, что если на входы 19 и 20 устройства не подавать импульсы обратных связей, то оно (как и прототип) будет вырабатывать величину 1/2-(а+Ъ) с методической погрешностью в 1 квант (соответствующий одному импульсу положительного или отрицателького приращения слагаемого). Технико-экономическая эффективность изобретения заключается в том, что предложенное суммирующее устройство проще прототипа (действительно, если прототип содержит 18 комбинационных логических элементов и два триггера, то предлагаемое устройство содержит 13 комбинационных элементов и один триггер) и имеет повышенную точность, так как кроме тернарного кода суммы двух слагаемых оно вырабатывает младщий даoичный разряд суммы этих слагаемых, поступающих на устройство тернарных кодов. При этом учитывая, что вес импульса выходного тернарного кода суммы в два раза больше веса младщего двоичного разряда суммы, то использование, изобретения позволит повысить в два раза точность вычисления суммы и, следовательно, точность устройств, в. котором оно будет использоваться.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Дифференцирующее устройство | 1984 |

|

SU1304020A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 2002 |

|

RU2207529C1 |

| Суммирующее устройство | 1977 |

|

SU696449A1 |

| Квадратор | 1983 |

|

SU1092501A1 |

| Арифметическое устройство | 1977 |

|

SU682894A1 |

| Линейный интерполятор | 1986 |

|

SU1383302A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

Авторы

Даты

1980-01-05—Публикация

1977-08-26—Подача