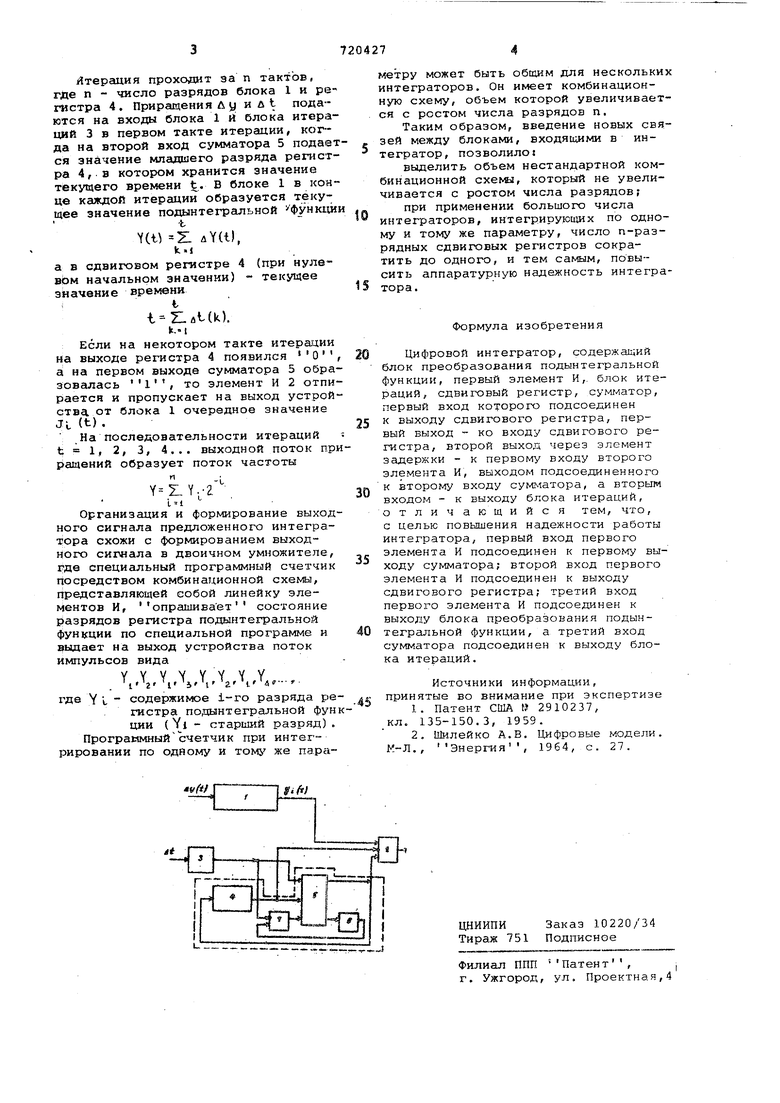

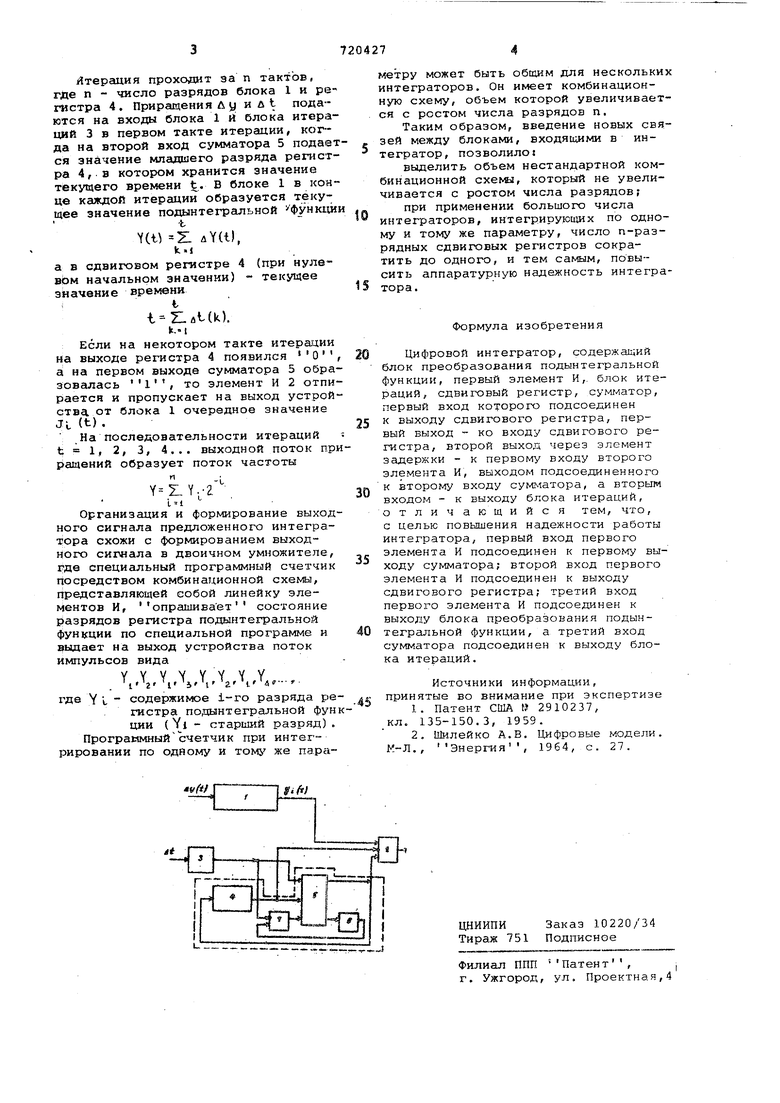

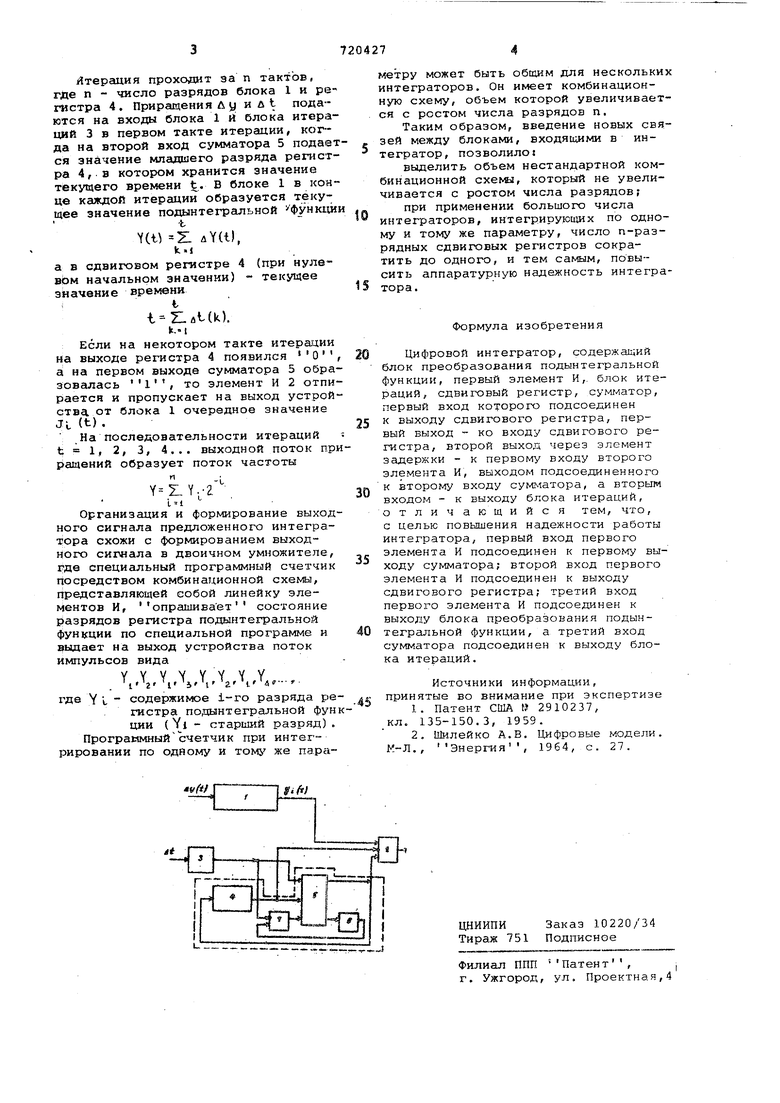

Устройство относится к вычислительным устройствам систем управле и может быть использовано в систем численного программного управления различным технологическим оборудованием. Известен интегратор 1, содерж счетчик подынтегральной yнкции, счетчик тактовых импульсов и комбинационный блок, состоящий из зле ментов И-ИЛИ. Недостатком устройства является то, что объем комбинационного блока увеличивается пропорционально числу его разрядов. Наиболее близким техническим решением к изобретению является интегратор цифрового д1- фференциально анализатора 2, содержащий блок преобразования подынтегральной функ ции, первый элемент И, блок итераций, сдвиговый регистр, сумматор, первый вход которого подсоединен к выходу сдвигового регистра, первый выход - ко входу сдвигового регистра, второй выход - ч«рез элемен задержки к первому входу второго элемента И, подсоединенного выходом к второму входу су№-;зтора, а орым входом к выходу блока итераDTCгздостатком данного устройства является то, что объем блока преобразования подынтегральной функции увеличивается пропорционально числу его разрядов, что снижает надежность работы всего устройства. Цель изобретения - повышение . надежности работы интегратора. Поставленная цель достигается тем, что в предложенном устройстве первый вход первого элемента И подсоединен к первому выходу сумматора. Второй вход первого элемента И подсоединен к выходу сдвигового регистра. Третий вход первого элемента И подсоединен к выходу блока преобразования подынтегральной функции, а третий вход cyNiMaTopa подсоединен к выходу блока итераций. На чертеже представлена структурная схема интегратора. Он содержит блок преобразования подынтегральной функции 1, элемент И 2, блок итераций 3, сдвиговый регистр 4, суьчзчатор 5, элемент задер лки 6 и элемент И 7. .Интегратор работает следующим образом.

итерация проходит за п тактов, где п - число разрядов блока 1 и регистра 4, Приращени я Л у Hut подаются на входы блока 1 и блока итераций 3 в первом такте итерации, когда на второй вход сумматора 5 подается значение младшего разряда регистра 4, в котором хранится значение текущего времени t. В блоке 1 в конце каждой итерации образуется текущее значение подынтегральной функ1ш

YW 2: дУа), fc.i

а в сдвиговом регистре 4 (при нулевом начальном значении) - текущее значение времени

t Z:flt(k).

К-м

Если на некотором такте итера ции на выходе регистра 4 появился О а на первом выходе сумматора 5 образовалась , то элемент И 2 отпирается и пропускает на выход устройства от блока 1 очередное значение

JL (t).

На последовательности итераций , 2, 3, 4... выходной поток приращений образует поток частоты

Ч

.Y.-Z

bt

Организация и формирование выходного сигнала предложенного интегратора схожи с формированием выходного сигнала в двоичном умножителе, где специальный программный счетчик посредством комбинационной схек«, представляющей собой линейку элементов И, опрашивает состояние разрядов регистра подынтегральной функции по специальной программе и выдает на выход устройства поток импульсов вида

YYYXYYYY

I 2 I Ч I г. Ч 4-- где Y I - содержимое i-ro разряда регистра подынтегральной функции ( YI - старший разряд) , Програ1ямный счетчик при интегрировании по одному и TOMi же параметру может быть общим для нескольких интеграторов. Он имеет комбинационную схему, объем которой увеличивается с ростом числа разрядов п.

Таким образом, введение новых связей между блоками, входящими в интегратор, ПОЗВОЛИЛО

выделить объем нестандартной комбинационной cxeNSJ, который не увеличивается с ростом числа разрядов;

при применении большого числа интеграторов, интегрирующих по одному и тому же параметру, число п-разрядных сдвиговых регистров сократить до одного, и тем самым, повысить аппаратурную надежность интегратора.

Формула изобретения

Цифровой интегратор, содержащий блок преобразования подынтегральной функции, первый элемент И,, блок итераций, сдвизговый регистр, , первый вход которого подсоединен к выходу сдвигового регистра, первый выход - ко входу сдвигового регистра, второй выход через элемент задержки - к первому входу второго элемента И, выходом подсоединенного к второму входу сум1чатора, а вторым входом - к выходу блока итераций, отличающийся тем, что, с целью повышения надежности работы интегратора, первый вход первого элемента И подсоединен к первому выходу сумматора,- второй вход первого элемента И подсоединен к выходу сдвигового регистра; третий вход первого элемента И подсоединен к выходу блока преобразования подынтегральной функции, а третий вход сумматора подсоединен к выходу блока итераций.

Источники информации, принятые во внимание при экспертизе

1.Патент США 2910237, кл. 135-150.3, 1959.

2.Шилейко А.В. Цифровые модели. К-Л., Энергия, 1964, с. 27.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Цифровой интегратор | 1978 |

|

SU698017A1 |

| Цифровой интегратор | 1978 |

|

SU739566A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1977 |

|

SU734745A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

Авторы

Даты

1980-03-05—Публикация

1976-02-26—Подача