(54) ПОСТОЯННОЕ ЗАПОМИНА ЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037350A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1981 |

|

SU1010652A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

.- . : I

Изобретение относится к области вычислительной техники.

Известны постоянные запоминающие устройства (ПЗУ) с коррекцией ошибок 2.

Одно из известных ЗУ с блокировкой Неисправных запоминающих элементов

|ll содержит регистр адреса, соединенный со входом дешифратора, выход которого соединен с накопителем, выход которого подключен к блоку контроля на четность...,

Недостатками устройства является избыточность оборудования и возможность исправления только одиночных ошибок.

Наиболее близким техническим решением к изобретению является ЗУ с блокировкой неисправных элементов , содер жашее регистр адреса, вход которого соединен с входными адресными шинами устройства, а выход - со входом дешифратора адреса, первые выходы которого соединены со входами накопителя, ре-

гистр считываемой информации, вход которого соединен с выходами накопителя и коммутатора неисправных разрядов, а выход - с выходнымиинформационными шинам устройства, и блок хранения кодов неисправных разрядов.

Недостатком устройства является избыточность оборудования йз-ва наличия блока хранения кодов неисправных разрядов (дополнительного накопителя).

0

изобретения является повышение надежности путем сокращения количества оборудования.

Поставленная цель достигается тем, что в предложенном ПЗУ другие выходы

5 дешифратора соединенв с соответствующими входами коммутатора неисправных разрядов накопителя;

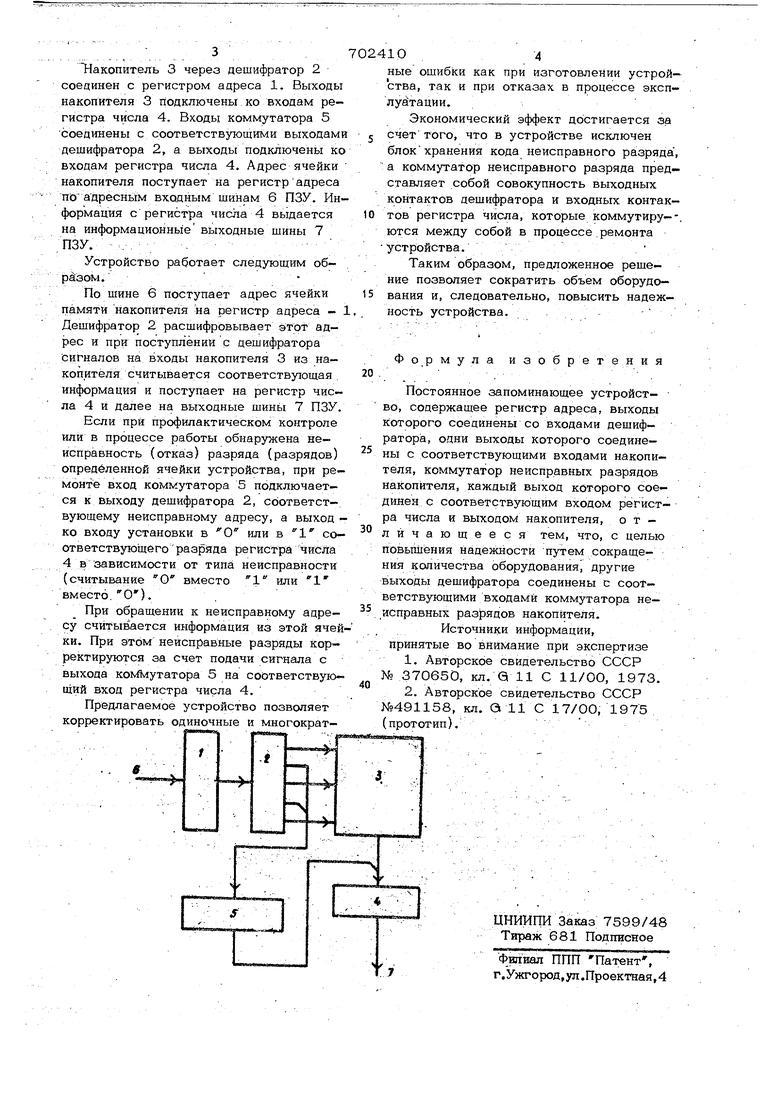

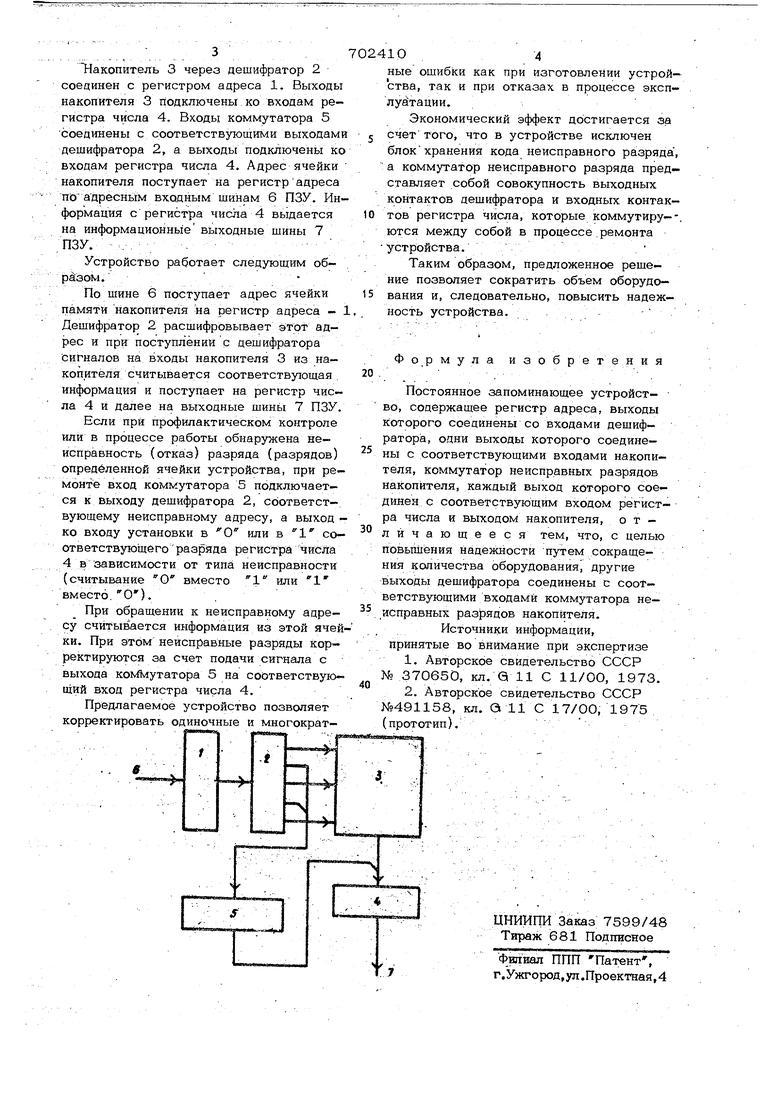

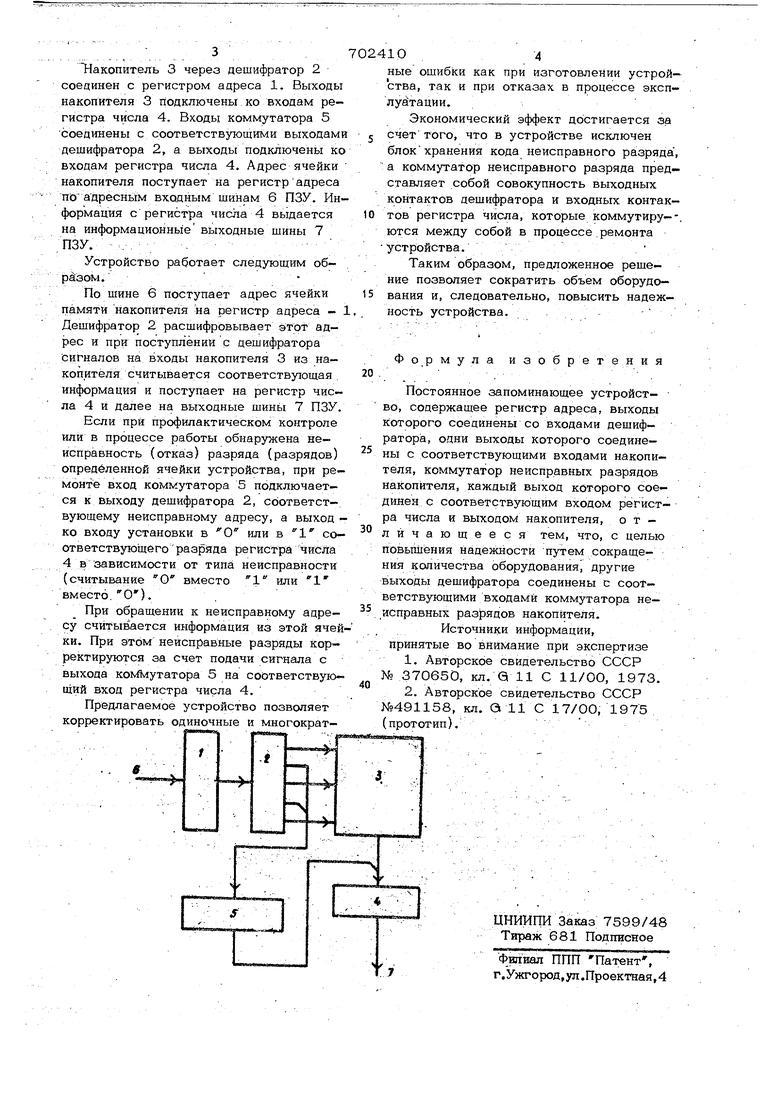

На чертеже представлена структурная схема ПЗУ с коррекцией ошибок.

Устройство содержит регистр адреса 1, дешифратор 2, накопитель 3, регистр числа 4 и коммутатор 5 неисправных разрядов накопителя.

Накопитель 3 через дешифратор 2 соединен с регистром адреса 1. Выходы накопителя 3 подключены ко входам регистра числа 4. Входы коммутатора 5 Соединены с соответствующими выходами дешифратора 2, а выходы подключены ко входам регистра числа 4. Адрес ячейки накопителя поступает на регистрадреса по адресным входным шинам б ПЗУ. Информация с регистра числа 4 выдается на информационные выходные шины 7 ПЗУ. .,

Устройство работает следующим обpstisoM.

По шине 6 поступает адрес ячейки памяти накопителя -на регистр адреса Дешифратор 2 расшифровывает этот адрес и при поступлении с дешифратора сигналов на входы накопителя 3 из накопителя считывается соответствующая информация и поступает на регистр числа 4 и далее на выходные шкнь 7 ПЗУ.

Если при профилактическом контроле или в процессе работы обнаружена неисправность (отказ) разряда (разрядов) определенной ячейки устройства, при ремонте вход коммутатора 5 подключается к выходу дешифратора 2, соответствующему неисправному адресу, а выход ко входу установки в О или в I соответствующегоразряда регистра числа 4 в зависимости от типа неисправности (считывание О вместо 1 или I вместо. О ).

При обращении к неисправному адресу считывается информация из этой ячейки. При этом неисправные разряды Корректируются за счет подачи сигнала с выхода KoivfMyTaTopa 5 на соответствующий вход регистра числа 4.

Предлагаемое устройство позволяет корректировать одиночные и многократные ошибки как при изготовлении устройства, так и при отказах в процессе эксплуйтации.

Экономический эффект достигается за счет того, что в устройстве исключен блокхранения кода неисправного разряда

: а коммутатор неисправного разряда представляет собой совокупность выходных контактов дешифратора и входных контактов регистра числа, которые коммутиру- ются между собой в процессе .ремонта

устройства.

Таким образом, предложенное решение позволяет сократить объем оборудования и, следовательно, повысить надежность устройства.Формула изобретения

Постоянное запоминающее устройство, содержащее регистр адреса, выходы которого соединены со входами дешифpaTopia, одни выходы которого соединены с соответствующими входами накопителя, коммутатор неисправных разрядов накопителя, каждый выход которого соединен с соответствующим входом регистра числа и выходом накопителя, отличающееся тем, что, с целью повьпнёния надежности путем сокращения количества оборудованияj другие выходы дешифратора соединены с соответствующими входами коммутатора неисправных разрядов накопителя. Источники информации, принятые во внимание при экспертизе

№ 370650, кл. Q 11 С 11/00, 1973.

Авторы

Даты

1979-12-05—Публикация

1978-05-10—Подача