(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU692400A1 |

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Буферное запоминающее устройство | 1991 |

|

SU1824651A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU409291A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

I

Изобретение относится к области вычислительной техники, Б частности, к запоминающим устройствам ЭВМ.

Известно запоминающее устройство, содержащее блок запоминания, регистр числа, регистр адреса, дешифратор адреса сообщения, постоянный запоминающий блок, счетчик приоритетов, элементы ИЛИ, дешифратор конца сообщений, блок управления, блок распределения ячеек запоминающего блока, регистры обмена, дешифратор числа страниц, счетчик страниц, преобразователь, реверсивный счетчик, причем выходы счетчика страниц подключены к дешифратору числа страниц, выходы которого подсоедицены ко входу блока управления 1.

Наиболее близким техническим (ёшени: ем к данному изобретению является постоянное запоминающее устройство (ПЗУ), содержащее накопитель, подключенный .К выходам дешифратора адреса, входы которого связаны с выходами регистра адреса, выходы накопителя подключены ко входам выходного регистра 2. ,

Недостатком известного устройства является невозможность выполнения с его

ПОМОЩЬЮ режима приоритетного управления иерархией памяти, осуществляемого в соответствии с вь1бранным алгоритмом удаления страниц.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства путем реализации режима приоритетного управления.

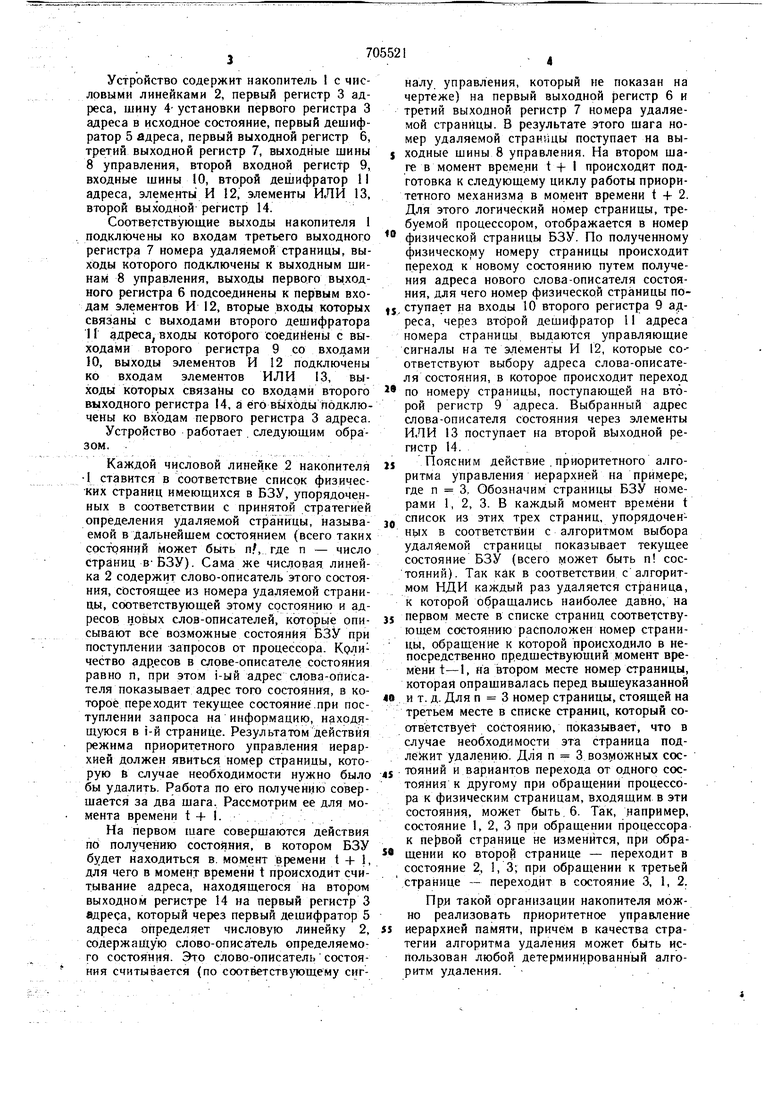

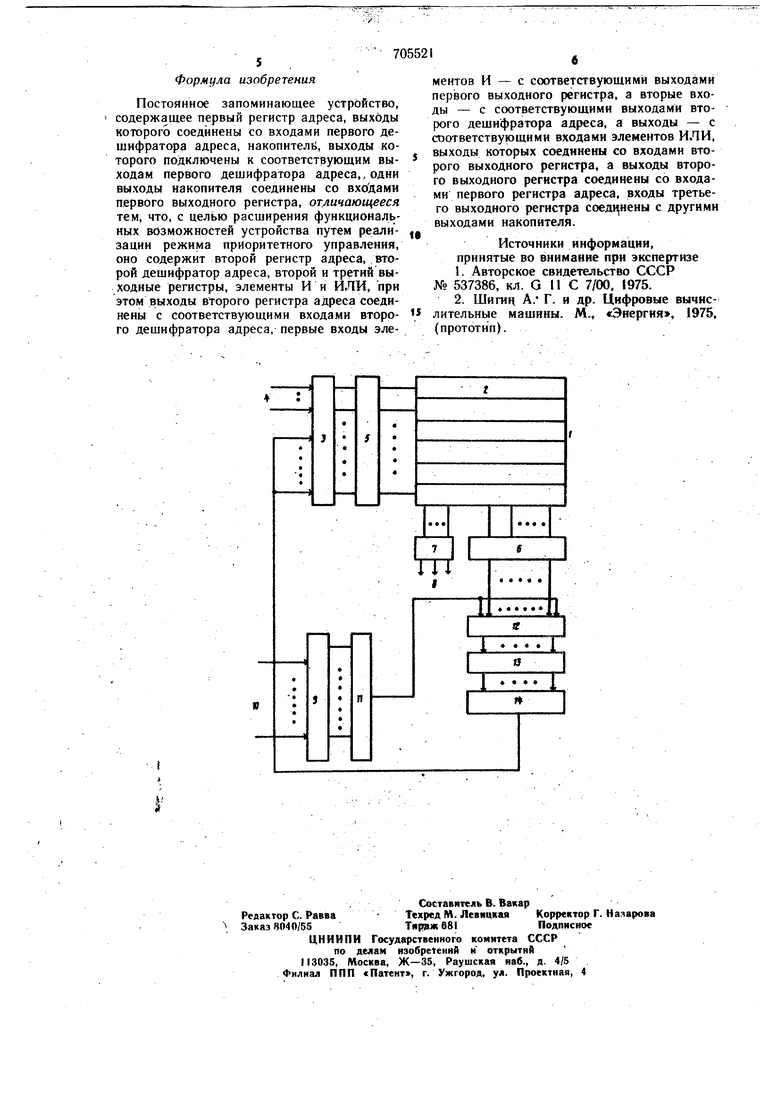

Для этого устройство содержит второй регистр адреса, второй дешифратор адреса, второй и третий выходные регистры, элементы И и ИЛИ, при этом выходы второго

9 регистра адреса соединены с соответствующими входами второго дешифратора адреса, первые входы элементов И - с соответствующими выходами первого выходного регистра, а вторые входы - с соответствующими выходами второго дешифратора адреса, а выходы с соответствующими входами элементов ИЛИ, ВЫХО.ДЫ которых соединены со входами второго выхЬдного регистра, а выходы второго выходного регистра соединены со вхо дами первого регистра адреса, входы тре тьего выходного регистра соединены с дру гими выходами накопителя.

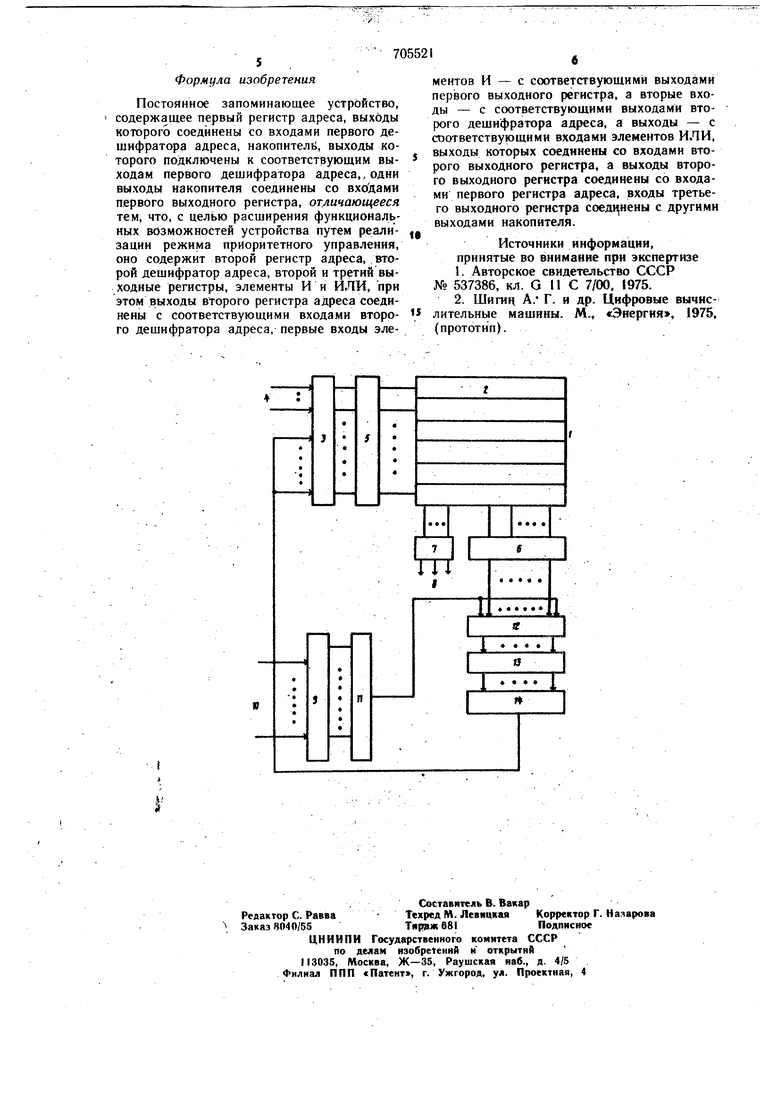

На чертеже приведена схема предлагав мого постоянного запоминающего устрой ства.

Устройство содержит накопитель I с числовыми линейками 2, первый регистр 3 адреса, шииу 4- установки первого регистра 3 адреса в исходное состояние, первый дешифратор 5 адреса, первый выходной регистр 6, третий выходной регистр 7, выходные шины 8 управления, второй входной регистр 9, входные шины 10, второй дешифратор 11 адреса, элементы И 12, элементы ИЛИ 13, второй выходной регистр 14.

Соответствуюшие выходы накопителя 1 подключены ко входам третьего выходного регистра 7 номера удаляемой страницы, выходы которого подключены к выходным шинам 8 управления, выходы первого выходного регистра 6 подсоединены к первым входам элементов И 12, вторые входы которых связаны с выходами второго дешифратора И адреса, входы которого соеднйены с выходами второго регистра 9 со входами 10, выходы элементов И 12 подключены ко входам элементов ИЛИ 13, выходы которых связаны со входами второго выходного регистра 14, а его выходы подключены ко входам первого регистра 3 адреса.

Устройство работает . следующим образом.

Каждой числовой линейке 2 накопителя I ставится в соответствие список физических страниц имеющихся в БЗУ, упорядоченных в соответствии с принятой стратегией определения удаляемой страницы, называемой в Дальнейшем состоянием (всего таких состояний может быть п., где п - число страниц в-БЗУ). Сама же числовая линейка 2 содержит слово-описатель этого состояния, сьстоящее из номера удаляемой страницы, соответствующей этому состоянию и адресов новых слов-описателей, которь1е описывают все возможные состояния БЗУ при поступлении запросов от процессора. Количество адресов в слове-описателе состояния равно п, при этом i-ый адрес слова-описателя показывает адрес того состояния, в которое переходит текущее состояние.при поступлении запроса на информацию, находящуюся в i-й странице. Результатом действия режима приоритетного управления иерархией должен явиться номер страницы, которую в случае необходимости нужно было бы удалить. Работа по его получению совершается за два шага. Рассмотрим ее для момента времени t 4- I. .

На первом шаге совершаются действия п6 получению состояния, в котором БЗУ будет находиться в. момент времени t -ь 1, для чего в момент времени t происходит считывание адреса, находящегося на втором выходном регистре 14 на первый регистр 3 адреса, который через первый дешифратор 5 адреса определяет числовую линейку 2, содержащую слово-описатель определяемого состояния. Это слово-описатель состояния считывается (по соответств тощему сигналу управления, который не показан на чертеже) на первый выходной регистр 6 и третий выходной регистр 7 номера удаляемой страницы. В результате этого шага номер удаляемой страницы поступает на вы$ ходные шины 8 управления. На втором шаге в момент времени t + 1 происходит подготовка к следующему циклу работы приоритетного механизма в момент времени t -f 2. Для этого логический номер страницы, требуемой процессором, отображается в номер

физической страницы БЗУ. По полученному физическому номеру страницы происходит переход к новому состоянию путем получения адреса нового слова-описателя состояния, для чего номер физической страницы поJ ступает на входы 10 второго регистра 9 адреса, через втброй дешифратор 11 адреса номера страницы выдаются управляющие сигналы на те элементы И 12, которые со-ответствуют выбору адреса слова-описателя состояния, в которое происходит переход

по номеру страницы, поступающей на второй регистр 9 адреса. Выбранный адрес слова-описателя состояния через элементы ИЛИ 13 поступает на второй выходной регистр 14.

J Поясним действие . приоритетного алгоритма управления иерархией на примере, где п 3, Обозначим страницы БЗУ номерами 1, 2, 3. В каждый момент времени t список из этих трех страниц, упорядоченнь1х в соответствии с алгоритмом выбора удаляемой страницы показывает текущее состояние БЗУ (всего может быть п состояний). Так как в соответствии с алгоритмом НДИ каждый раз удаляется страница, к которой обращались наиболее давно, на

5 первом месте в списке страниц соответствующем состоянию расположен номер страницы, обращение к которой происходило в непосредственно предществующий момент времени t- 1, на втором месте номер страницы, которая опрашивалась перед выщеуказанной

в и т. д. Для п 3 номер страницы, стоящей на третьем месте в списке страниц, который соответствует состоянию, показывает, что в случае необходимости эта страница подлежит удалению. Для п 3 возможных состояний и вариантов перехода от одного состояния к другому при обращении процессора к физическим страницам, входящим в эти состояния, может быть. 6. Так, например, состояние 1, 2, 3 при обращении процессора к пе{)вой странице не изменится, при обра щении ко второй странице - переходит в

состояние 2, 1,3; при обращении к третьей

странице - переходит в состояние 3, 1, 2.

При такой организации накопителя можно реализовать приоритетное упраааение S иерархией памяти, причем в качества стратегии алгоритма удаления может быть использован любой детерминированный алгоритм удаления.

Формула изобретения

Постоянное запоминающее устройство, содержащее первый регистр адреса, выходы которого соединены со входами первого дешифратора адреса, накопители, выходы которого подключены к соответствующим выходам первого дешифратора адреса,, одни выходы накопителя соединены со первого выходного регистра, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем реализации режима приоритетного управления, оно содержит второй регистр адреса, второй дешифратор адреса, второй и третий выходные регистры, элементы И и ИЛИ, при этом выходы второго регистра адреса соединены с соответствующими входами второго дешифратора адреса, первые входы элементов И - с соответствующими выходами первого выходного регистра, а вторые входы - с соответствующими выходами второго дешифратора адреса, а выходы - с соответствующими входами элементов ИЛИ, выходы которых соединены со входами второго выходного регистра, а выходы второго выходного регистра соединены со входами первого регистра адреса, входы третьего выходного регистра соед1 нены с другими выходами накопителя.

Источники информацни, принятые во внимание при экспертизе

5 (прототип).

Авторы

Даты

1979-12-25—Публикация

1977-06-14—Подача