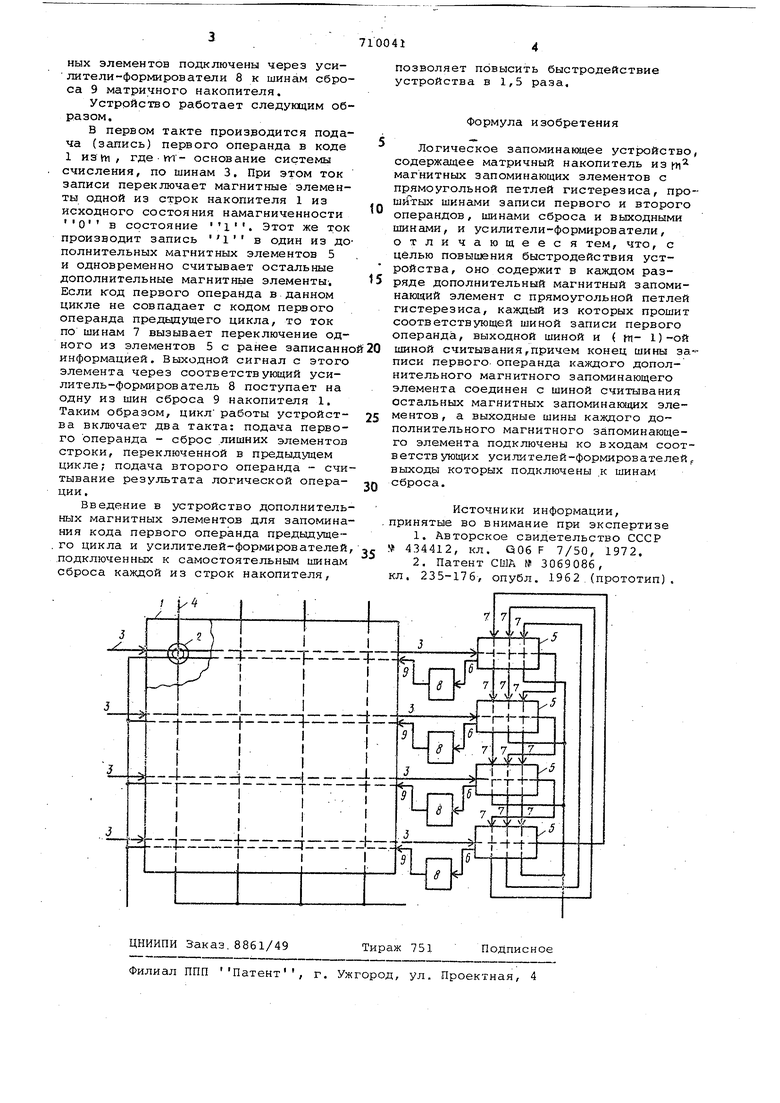

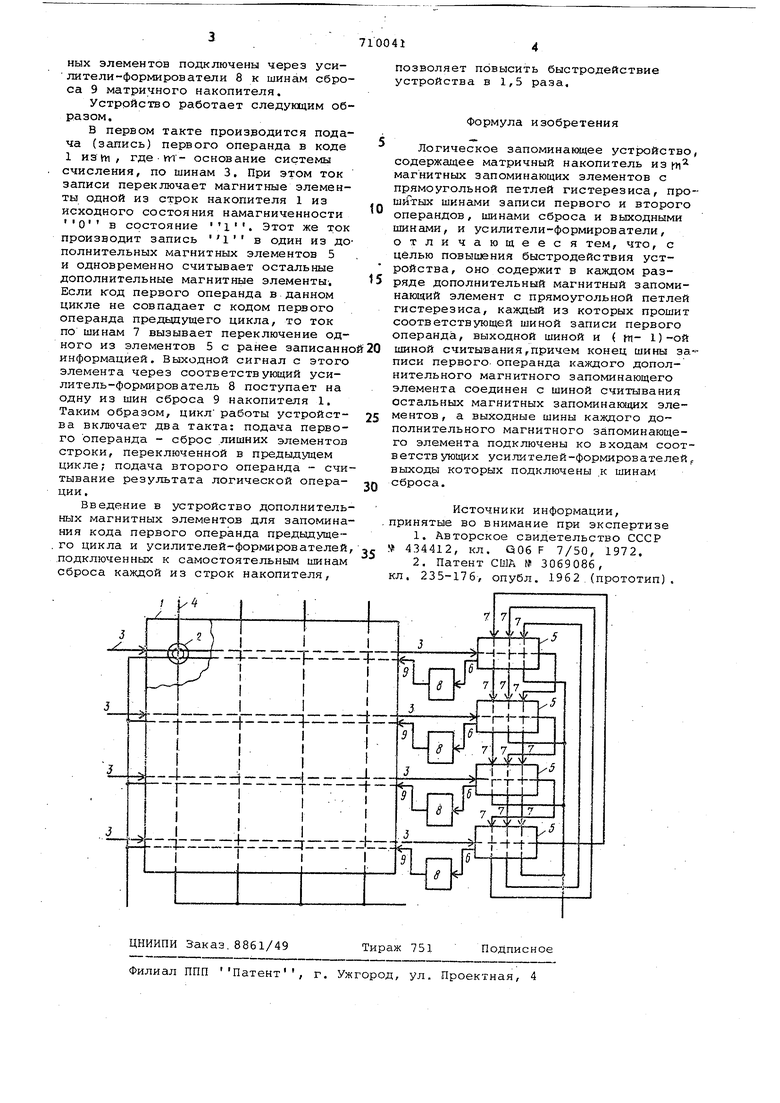

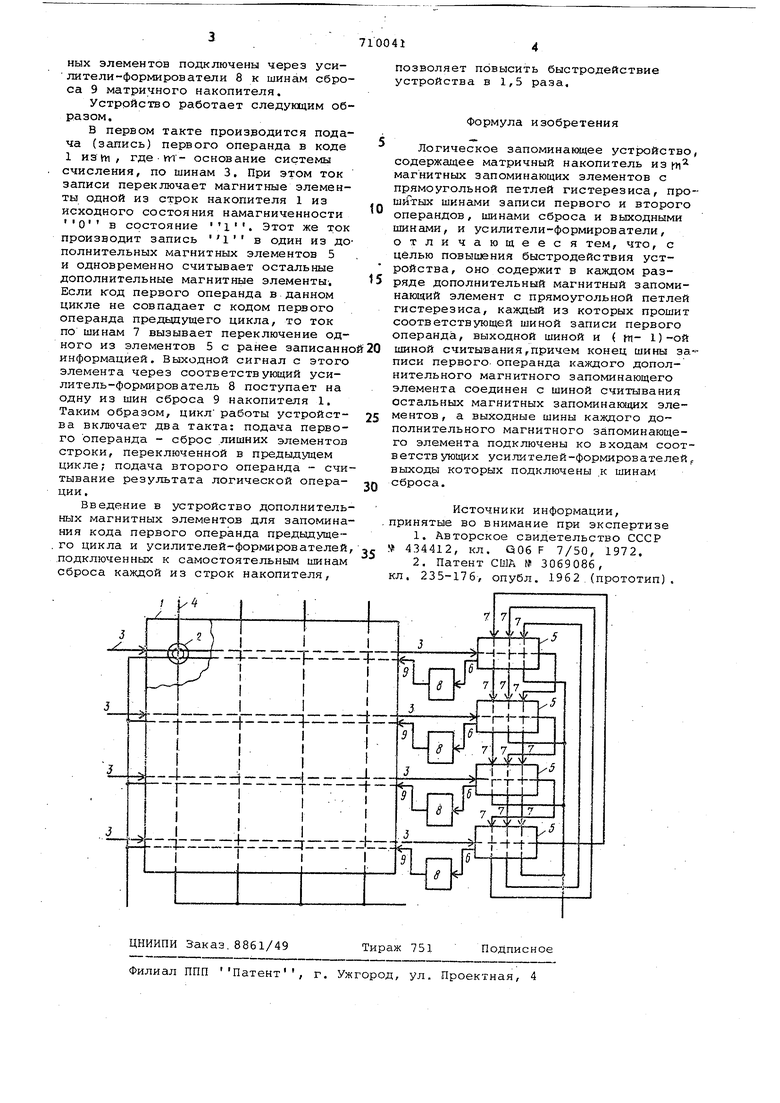

Изобретение относится к области вычислительной техники и может быть использовано в процессорах специализированных высоконадежных иэм. Известны логические запоминагацие устройства, содержащие магнитные сердечники, прошитые шинами записи, считБшания и выходными шинами в соответствии с таблицами выполнения логических операций 1. йедостатком их является низкое быстродействие. Известно также логическое запоминающее устройство, содержащее матричный накопитель из rti магнитных запоминающих элементов с прямоуголь ной петлей гистерезиса, прошитых шинами записи первого и второго опера дов , шинами сброса и выходными шинами, и усилители-формирователи 21, Недостатком такого устройства яв ляется низкое быстродействие. Цель изобретения - повышение быс родействия. Это достигается тем, что предлагаемое устройство содержит в каждом разряде дополнительный магнитный запоминающий элемент с прямоугольной петлей гистерезиса, каждый из которых прошит соответстгвующей шиной за писи первого операнда, выходной шиной и ( т 1)-6й шиной считывания, причем конец шины записи первого операнда каждого дополнительного магнитного запоминающего элемента соединен с шиной считывания остальных магнитных запоминакхдих элементов , а выходные шины каждого дополнительного магнитного запоминающего элемента подключены ко входам соответствующих усилителей-формировате.пей, выходы которых подключены к шинам сброса. На чертеже показана блок-схема предлагаемого логического запоминакзцего устройства (для примера ), где магнитные элементы показаны успов но. Устройство содержит матричный накопитель 1, состоящий из т магнитных элементов 2, прошитых шинами 3 записи.первого операнда и шинами 4 записи второго операнда. Кроме того, устройство содержит HI дополнительных .магнитных элементов 5, прошитых шинаг и записи первого операнда 3, выходными шинами ,6 и (т- 1)-ой шиной считывания 7. Конец шины записи каждого дополнительного элемента подключен к шинам считывания других элементов. Выходные шины дополнительных элементов подключены через усилители-формирователи 8 к шинам сброса 9 матричного накопителя. Устройство работает следующим образом. В первом такте производится подача (запись) первого операнда в коде 1 изчи, где т- основание системы счисления, по шинам 3, При этом ток записи переключает магнитные элементы одной из строк накопителя 1 из исходного состояния намагниченности О в состояние Ч. Этот же ток производит запись в один из до полнительных магнитных элементов 5 и одновременно считывает остальные дополнительные магнитные элементы-. Если к-од первого операнда в данном цикле не совпадает с кодом первого операнда предьщущего цикла, то ток по шинам 7 вызывает переключение одного из элементов 5 с ранее записанно информацией. Выходной сигнал с этого элемента через соответствующий усилитель-формирователь 8 поступает на одну из шин сброса 9 накопителя 1. Таким образом, цикл работы устройства включает два такта: подача первого операнда - сброс лишних элементов строки, переключенной в предыдущем цикле; подача второго операнда - счи тывание результата логической операции. Введение в устройство дополнитель ных магнитных элементов для запомина ния кода первого операнда предыдуще.го цикла и усилителей-формирователей подключенных к самостоятельным шинам сброса каждой из строк накопителя. позволяет повысить быстродействие устройства в 1,5 раза. Формула изобретения Логическое запоминающее устройство, содержащее матричный накопитель из | магнитных запоминающих элементов с прямоугольной петлей гистерезиса, прошйЪых шинами записи первого и второго операндов, шинами сброса и выходными шинами, и усилители-формирователи, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит в каждом разряде дополнительный магнитный запоминающий элемент с прямоугольной петлей гистерезиса, каждый из которых прошит соответствующей шиной записи первого операнда, выходной шиной и ( nt- 1)-ой шиной считывания,причем конец шины за--писи первого, операнда каждого дополнительного магнитного запоминающего элемента соединен с шиной считывания остальных магнитных запоминаквдих элементов, а выходные шины каждого дополнительного магнитного запоминающего элемента подключены ко входам соответствующих усилителей-формирователей,: выходы которых подключены .к шинам сброса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 434412, кл. Q06 F 7/50, 1972. 2.Патент США № 3069086, кл. 235-176, опубл. 1962 . (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Блок переноса для матричного сумматора | 1982 |

|

SU1061135A1 |

| НАКОПИТЕЛЬНАЯ ЛОГИЧЕСКАЯ МАТРИЦА | 1972 |

|

SU354470A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Запоминающее устройство | 1973 |

|

SU481938A1 |

| Запоминающее устройство | 1980 |

|

SU928409A1 |

Авторы

Даты

1980-01-15—Публикация

1977-10-17—Подача