со ел

2. Блок no п. 1, отличающийся , что узел коммутации содержит восемь транзисторов и четыре магнитных сердечника с прямоугольной петлей гистерезиса, прошитых шинами старшей цифры, поразрядного переноса, инверсии старшей цифры и инверсии поразрядного, переноса, соединенными соответственно с .третьим, четвертым, пятым и шестым входами узла, каждый сердечник прошит также шиной установки и двумя выходными шинами, причем первые выходные шины соединены соответствейно с..базами и эмиттерами рервого второго,, третьего и четвертого транзисторов, а вторые выходные шины - с базами и эмиттерами пяуого, шестого, седьмого и восьмого транзисторов, кол.екторы первого и второго транзисторов соединены с первым входом узла, а коллекторы третьего и четвертого транзисторов - с вторым входом узла, коллекторы пятого и шестого транзисторов соединены с седьмым входом узла, а коллекторы седьмого и восьмого транзисторов соединены с восьмым входом узла, эмиттеры первого и третьего транзисторов соединены с первым выходом узла, эмиттеры второго и четвертого транзисторов соединены с вторым выходом узла, эмиттеры пятого и седьмого транзисторов соединены с третьим выходом, а эмиттеры шестого к восьмого транзисторов - с четвертым выходом узла, коммутации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок переноса для матричного сумматора | 1976 |

|

SU624229A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1991 |

|

RU2030792C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

1. БЛОК ПЕРЕНОСА ДЛЯ МАТРИЧНОГО СУММАТОРА, содержащий в каждом т-ичном разряде первый и второй т-разрядные регистры на магнитных сердечниках с прямоугольной петлей гистерезиса, прошитые входными и выходными шинами считывания и установки, входные шины соединены с входами разрядов блока, а выходные шины - с выходами разрядов блока, и узел коммутации, первый и второй входы которого соединены с концами шин считывания соответственно первого и второго т-разрядных регистров того же т-ичного разряда, третий вход узла коммутации соединен с входом старшей цифры, а четвертый вход - с входом поразрядного переноса т-ичного разряда блока, первый и второй выходы узла коммутации соединены с началами шин считывания соответственно первого и второго т-ичных регистров следуюш,его т-ичного разряда, отличающийся тем, что, с целью повышения быстродействия блока, пятый вход узла коммутации соединен с входом инверсии старшей цифры, а шестой вход - с входом инверсии поразрядного переноса ш-ичного разряда блока, седьмой и, восьмой входы узла коммутации-соединень соответственно с третьим и четвертым выхо- дами узле коммутации предыдущего т-ичного разряда, ш-ичные разряды разбиты на группы, причем третий и четвертый выходы узла коммутации старшего разряда группы соединены соответственно с седьмым и восьi (Л мым входами узла коммутации младшего разряда следующей группы и входами щин установки первого и второго межгрупповых элементов памяти на магнитных сердечниках, прошитых также шинами считывания, причем выходы первого и второго межгрупповых элементов памяти соединены соответственно с первым и вторым входами узла коммутации младшего разряда следуюи1ей О5 группы.

1

Изобретение относится к вычислительной технике и может найти применение в процессорах специализированных ЭВМ.

Известен матричный параллельный сумматор на магнитных сердечниках с прямоугольной петлей гистерезиса, имеющий блоки последовательного межкаскадного переноса 1 .

Недостатком этого сумматора является низкое быстродействие.

Наиболее близким техническим решение.м к изобретению является блок переноса для матричного сумматора, содержаший в каждом т-ичном разряде первый и второй ш-разрядные регистры на магнитных сердечниках с прямоугольной петлей гистерезиса, прошитые входными и выходными шинами считывания и установки, входные шины соединены .с входами разрядов блока, а выходные шины - с выходами разрядов блока, и узел коммутации, первый и второй входы которого соединены с концами шин считывания соответственно первого и второго тразрядных регистров того же т-ичного разряда, третий вход соединен с входом старшей цифры, а четверый вход - с входом поразрядного переноса т-ичйого разряда блока, первый и второй выходы узла коммутации соединены с началами шин считывания соответственно первого и второго т-ичных регистров следующего т-ичного разряда. Узел коммутации содержит четыре магнитных сердечника и четыре транзистора. Блок переноса работает совместно с многоразрядным матричным ш-ичным сумматором по трех тактному циклу 2.

Недостатком известного устройства является низкое быстродействие, обусловленное тем, что сигнал переноса проходит через все разряды блока переноса, считывая все тразрядные регистры. Из-за большой индуктивности цепи, образованной шинами считывания т-разрядных регистров, имеет место задержки сигнала переноса.

Цель изобретения - повышение быстродействия блока переноса для матричного сумматора.

Указанная цель достигается тем, что в блоке переноса для матричного сумматора, содержащем в каждом т-ичном разряде первый и второй т-разрядные регистры на магнитных сердечниках с прямоугольной петлей гистерезиса, прошитые входными и выходными шинами считывания и установки, входные шины соединены с входами разрядов блока, а выходные шины - с выходами разрядов блока, и узел коммутации, первый и второй входы которого соединены с концами шин считывания соответственно первого и второго т-разрядных регистров того же т-ичного разряда, третий вход узла коммутации соединен с входом старшей цифры, а четвертый вход - со входом поразрядного переноса т-ичного разряда блока, первый и второй выходы узла коммутации соединены с началами шин считывания соответственно первого и второго т-ичных регистров следующего т-ичного разряда, пятый вход узла коммутации соединен с входом инверсии старшей цифры, а шестой вход - с входом инверсии поразрядного переноса т-ичного разряда блока, седьмой и восьмой входы узла коммутации соединены соответственно с третьим и четвертым выходами узла коммутации прудыдущего т-ичного разряда, т-ичные разряды разбиты на группы, причем третий и четвертый выходы узла коммутации старшего разряда группы соединены соответственно с седьмым и восьмым входами }зла коммутации младшего разряда следующей группы и входами,шин установки первого и второго межгрупповых элементов памяти на магнитных сердечника.х. проинтых также шинами считывания, причем выходы первого и второго межгрупповых элементов памяти соединены соответственно с первым и вторым входами узла коммутации младшего разряда следующей группы.

Узел коммутации содержит восемь транзисторов и четыре магнитных сердечника с прямоугольной петлей гистерезиса, прошитых шинами старшей цифры, поразрядного переноса, инверсии старшей цифры и инверсии поразрядного переноса, соединенными соответственно с третьим, четвертым, пятым и шестым входами узла, каждый сердечник также прошит шиной установки, ее двумя выходными шинами, причем первые выходные шины соединены соответственно с базами и эмиттерами первого, второго, третьего и четвертого транзисторов, а вторые выходные шины - с базами и эмиттерами пятого, шестого, седьмого и восьмого транзисторов, коллекторы первого и второго транзисторов соединены с первым входом узла, а коллекторы третьего и четвертого транзисторов - с вторым входом узла, коллекторы пятого и шестого транзисторов соединены с седьмым входом узла, а коллекторы седьмого и восьмого транзисторов соединены с восьмым входом узла, эмиттеры первого и третьего транзисторов соединены с первым выходом узла, эмиттеры второго и четвертого транзисторов соединены с вторым выходом узла, эмиттеры пятого и седьмого транзисторов соединены с третьим выходом, а эмиттеры шестого и восьмого транзисторов - с четвертым выходом узла коммутации.

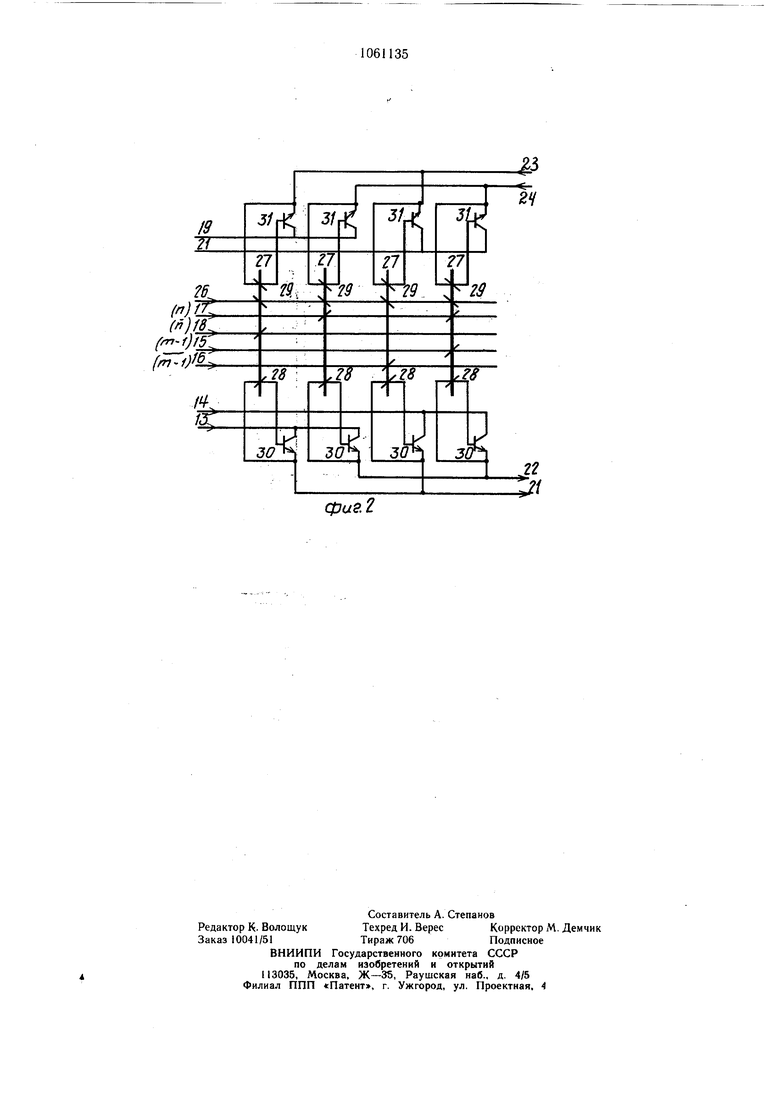

На фиг. 1 представлена структурная схема блока переноса для матричного сумматора; на фиг. 2 - принципиальная схема узла коммутации.

Блок переноса для матричного сумматора содержит группы 1 т-ичных разрядов. В каждом т-ичном разряде блок содержит ш-разрядные регистры 2 и 3 на магнитных сердечниках и узел 4 коммутации. Между группами включены межгрупповые элементы памяти 5 и 6, ш-разрядные регистры имеют входы переноса 7 и 8, соединенные с началами соответствующих шин считывания, входы для приема поразрядной суммы 9 и 10 и выходы цифры суммы 11 и 12, а также шину установки (на чертеже не показана). Узел коммутации содержит входы переноса 13 и 14, подключаемые к концам шин считывания регистров 2 и 3, входы 15 и 16 старшей цифры и инверсии старшей цифры, входы 17 и 18 поразрядного переноса и инверсии поразрядного переноса, входы 19 и 20 дополнительного переноса и выходы 21 и 22 переноса, подключаемые к входам 6 и 7 регистров 2 и 3, и выходы 23 и 24 дополнительного переноса. Межгрупповые элементы памяти имеют входы считывания, соединенные с шиной 25 считывания, а узел коммутации - вход установки 26. Узел коммутации состоит из магнитных сердечников 27, прошитых шинами 15-18 и 26, а также выходными шинами 28 и 29, а также тран зисторов 30 и 31.

Блок переноса для матричного сумматора работает следующим образом.

В первом такте на входные шины 9 и 10 с выходов матричного сумматора поступает

0 код поразрядной суммы в коде (1) из (ш). При этом в регистры 2 и 3 групп 1 разрядов блока переноса записывается код поразрядной суммы и суммы, увеличенной на единицу соответственно.

Одновременно на узел коммутации 4

5 подаются сигналы поразрядного переноса П и П, старшей цифры суммы (т-1) и (т-1) определяющие условия распространения переноса. В этом же такте происходит распространение сигнала по цепи дополнительного переноса внутри каждой группы 1 блока и запись его в один из двух межгрупповых элементов 5 или 6 памяти. Выбор конкретного элемента определяется условиями переноса в данной группе 1 разрядов, т. е. насыщением одного из транзисторов 31 в каж5 дом разряде группы 1. Таким образом происходит предварительное формирование условий переноса между группами 1 разрядов. Во втором такте происходит подача сигнала считывания элементов 5 и 6 по шине 25, сигнала считывания сердечников 27 узла

0 коммутации 4 по шине 26 и осуществляется распространение переноса и считывание по шинам 7 или 8 одного из регистров 2 или 3, в каждом разряде групп 1 разрядов. Номер считываемого регистра в следующем разряде внутри группы 1 определяется условиями

5 переноса в данном разряде, т. е. насыщением одного из транзисторов 30. Таким образом происходит быстрое распространение переноса во всех разрядах в каждой группе 1 разрядов. В третьем такте происходит уста новка блока переноса в исходное состояние. Работа блока переноса согласуется с работой трехтактного матричного сумматора, имеющего такты: прием первого операнда, прием второго операнда - выдача поразрядной суммы, возврат в исходное состояние.

5 Таким образом, за счет разбиения разрядов блока переноса на группы и введения межгрупповых элементов памяти, а также дополнительных входов и выходов переноса в узле коммутации и изменение его структуры удается повысить быстродействие блока

0 переноса для матричного сумматора не менее чем в 1,5 раза благодаря уменьшению длины цепи переноса, а следовательно, и уменьшению индуктивности шин считывания и задержки распространения переноса в блоке.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Блок переноса для матричного сумматора | 1976 |

|

SU624229A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-15—Публикация

1982-04-28—Подача