1

Система дискретното контроля временных закономерностей относится к области измерительной техники и контроля и может быть использована для контроля временных программно-командных приборов.

Известно устройство, содержащее регистр признаков канала и элемент ИЛИ, переключатель, запоминающее устройство, регистр адреса, формирователь адреса, генератор эталонной частоты, счетчик, элемент ИЛИ, цифровой индикатор, элемент совпадения, триггер разрещения, сумматор, регистр-накопитель, формирователь номера интервала, счетчик признаков канала 1.

Устройство имеет ограниченные функциональные возможности и не позволяет осуществлять контроль временных закономерностей большого числа временных сигналов одновременно с произвольным законом изменения длительностей каждого сигнала во времени.

Известно устройство, содержащее последовательно соединенные генератор опорной частоты и таймер, блок оперативной памяти, блок выработки команд и блок выдачи результата 2.

Недостатком устройства является то, что оно не позволяет осуществлять контроль временных закономерностей больщого числа временных сигналов одновременно с

произвольным законом изменения длительности каждого сигнала во времени.

Цель изобретения - расширение функциональных возможностей, а именно осуществление контроля множества временных сигналов с произвольным законом изменения длительностей каждого сигнала во времени.

Указанная цель достигается тем, что система дискретного контроля закономерностей дополнительно содержит регистр приема, регистр сравнения, схему поразрядного сравнения, элементы И, элемент ИЛИ, управляющие щииы, процессор, причем входы устройства через элементы И, вторые входы которых подключены к первой управляющей щине, соединены через последовательно включенные регистр приема, элемеиты И, вторые входы которых подключены к пятой управляющей шине, и элемент ИЛИ с процессором. Выходы регистра приема соединены также с входами схемы поразрядного сравнения и через элементы И, вторые входы которых подключеиы к второй управляющей шине, - с входами регистра сравиения. Процессор соединен с блоком оперативной памяти, блоком выработки команд и блоком выдачи результата. Выход таймера через элемент И, второй вход которого соединен с

третьей управляющей шиной, подключен к зход элемента ИЛИ, другие входы элемента ИЛИ через элементы И, вторые входы которых подключены к четвертой управляющей щине, соединены с соответствующи1 1и выходами схемы поразрядного сравнения.

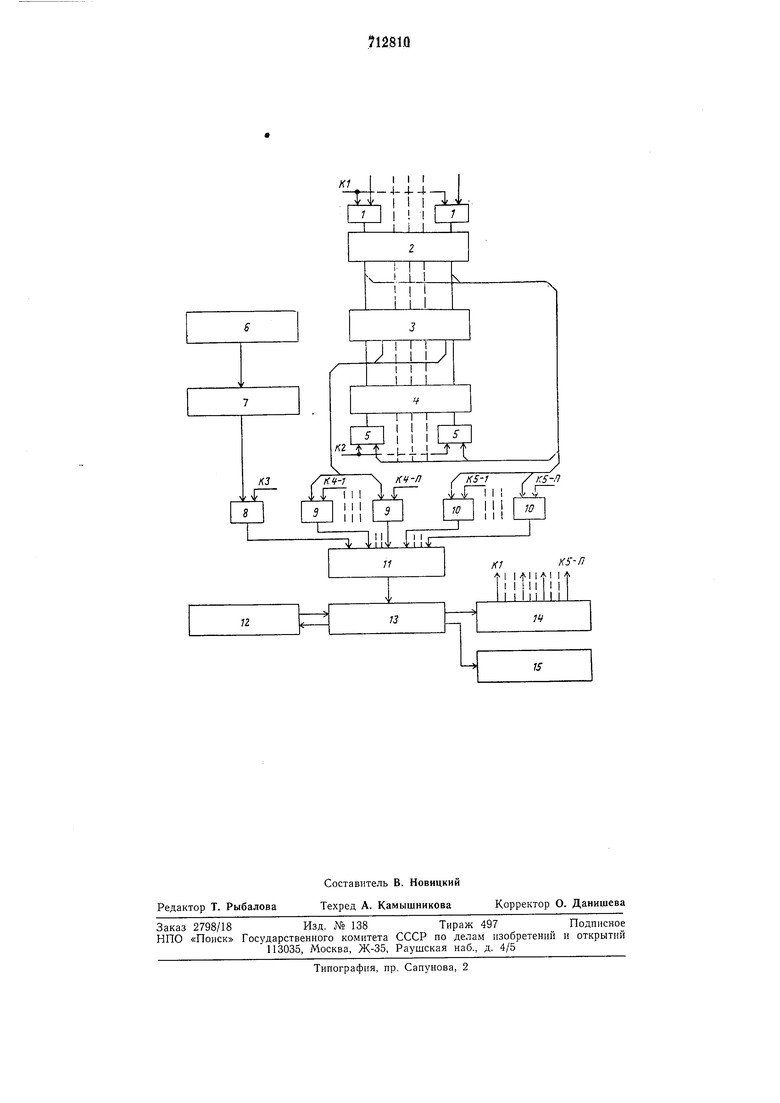

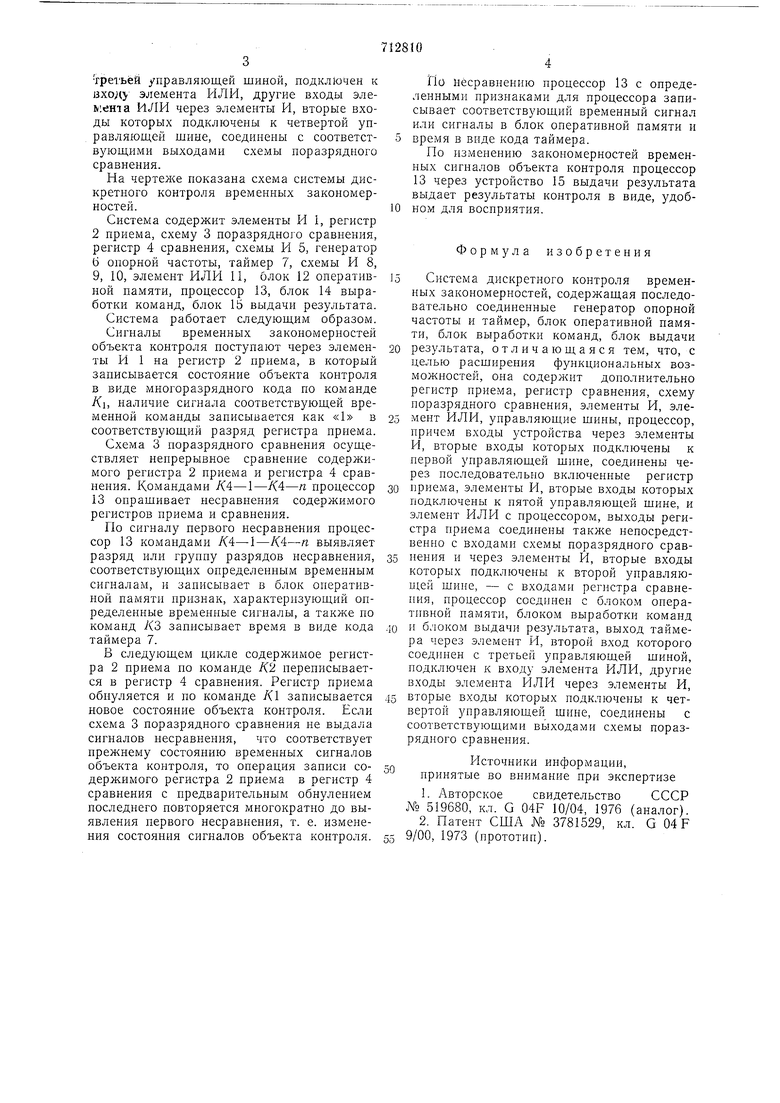

На чертеже показана схема системы дискретного контроля временных закономерностей.

Система содержит элементы И 1, регистр 2 приема, схему 3 поразрядного сравнения, регистр 4 сравнения, схемы И 5, генератор б опорной частоты, таймер 7, схемы И 8, 9, 10, элемент ИЛИ 11, блок 12 оперативной памяти, процессор 13, блок 14 выработки команд, блок 15 выдачи результата.

Система работает следующим образом.

Сигналы временных закономерностей объекта контроля ноступают через элементы И 1 на регистр 2 приема, в который записывается состояние объекта контроля в виде многоразрядного кода по команде KI, наличие сигнала соответствующей временной команды записывается как «1 в соответствующий разряд регистра приема.

Схема 3 поразрядного сравнения осуществляет непрерывное сравнение содержимого регистра 2 приема и регистра 4 сравнения. Командами К.4-1-/С4-п процессор 13 опрашивает несравнения содержимого регистров приема и сравнения.

По сигналу первого несравнения процессор 13 командами К4-1-/(4-п выявляет разряд или группу разрядов несравнения, соответствующих определенным временным сигналам, и записывает в блок оперативной памяти признак, характеризующий определенные временные сигналы, а также по команд КЗ заннсывает время в виде кода таймера 7.

В следующем цикле содержимое регистра 2 приема по команде К2 переписывается в регистр 4 сравнения. Регистр приема обнуляется и по команде /С1 записывается новое состояние объекта контроля. Если схема 3 поразрядного сравнения не выдала сигналов несравнения, что соответствует прежнему состоянию временных сигналов объекта контроля, то операция записи содержимого регистра 2 приема в регистр 4 сравнения с предварительным обнулением последнего повторяется многократно до выявления первого несравнения, т. е. изменения состояния сигналов объекта контроля.

По несравнению процессор 13 с определенными признаками для процессора записывает соответствующий временный сигнал или сигналы в блок оперативной памяти и время в виде кода таймера.

По измеиению закономерностей временных сигналов объекта контроля процессор 13 через устройство 15 выдачи результата выдает результаты контроля в виде, удобном для восприятия.

Формула изобретения

Система дискретного контроля временных закономерностей, содержащая последовательно соединенные генератор опорной частоты и таймер, блок оперативной памяти, блок выработки команд, блок выдачи

результата, отличающаяся тем, что, с целью расширения функциональных возможностей, она содержит дополнительно регистр приема, регистр сравнения, схему поразрядного сравнения, элементы И, элемент ИЛИ, управляющие щины, процессор, причем входы устройства через элементы И, вторые входы которых подключены к первой управляющей щине, соединены через последовательно включенные регистр

приема, элементы И, вторые входы которых подключены к пятой управляющей шине, и элемент ИЛИ с процессором, выходы регистра приема соединены также непосредственно с входами схемы поразрядного сравнения и через элементы И, вторые входы которых подключены к второй управляющей шине, - с входами регистра сравнения, процессор соединен с блоком оперативной памяти, блоком выработки команд

и блоком выдачи результата, выход таймера через элемент И, второй вход которого соединен с третьей управляющей шиной, подключен к входу эле.мента ИЛИ, другие входы элемента ИЛИ через элементы И,

вторые входы которых подключены к четвертой управляющей шине, соединены с соответствующими выходами схемы поразрядного сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 519680, кл. G 04F 10/04, 1976 (аналог).

2.Патент США № 3781529, кл. G 04 F 9/00, 1973 (прототип).

I II I I

{ Yf

/(V-fl

-v

I I ЧУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Устройство для программного управления технологическими процессами | 1979 |

|

SU877476A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

Авторы

Даты

1980-01-30—Публикация

1978-01-10—Подача