(54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНОДЕСЯТИЧНОГО КОДА 8-4-2-1 В ЧАСТОТУ

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

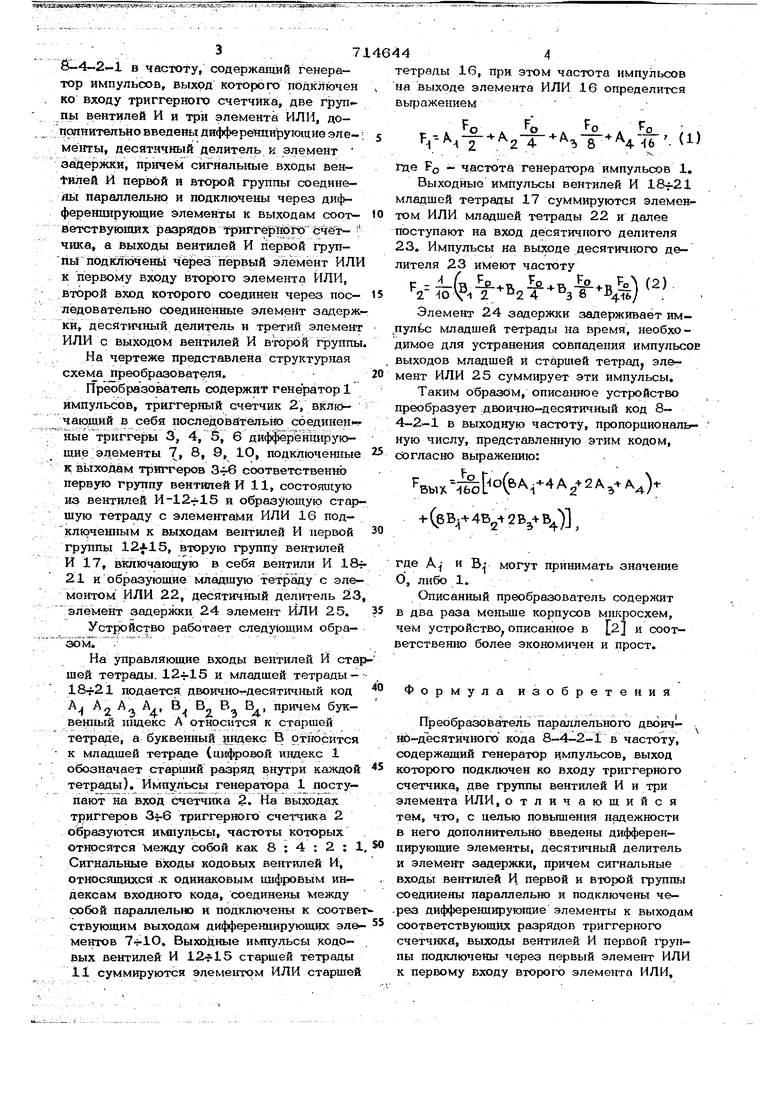

1 -;.. Иаобретейие касается вычислительной техники, в частности, оно может быть использовано в цифровых вычислитепьньк устройствах и цифровых генераторах низких частот. Извести) устройство для прео6разов(г кия параллельного кода в частоту следования импульсов, содержащее генератор импульсов, 1феобразователь код-время, кодовые вейтвлв, счетчик постоянной ёмkocTH и блок угравления l. Это устройство М|рактеризу«ется значительной слояьвостью из-за наличия промежуточвбзсх) преобразователя код-время. , Нанболее близким по технической, cymi вое-га к предлагаемому является гфеобразователь, описанный в 2, Это устройство содержит генератор импульсов, триргерный двоично-десятичный счетчик, рфс ботающих в коде , триггерный многоразрядный двоично-десятичшдй счетчик, работающий в воде 5-2-1-1, вектили И и ИЛИ. Это устройство преобразует число входных импульсов, поступающих на вход счетчика, работающего в коде 5-2-1-1, в пропорциональную частоту. Для преобразования параллельного двоичнодесятичного кода 8-4-2-1 в частоту счетчик, работающий в коде 5-2-1-1, должен быть исключен, однако в известное устройство должен быть введев дополнительный кодопреобразователь, осуществляющий преобразование входного параллельного кода 8-4-2-1 код 5-2-1-1. При построении многоразрядных преобразователей кода 8-4-2-1 в частоту требуется большое количество счетных триггеров. Кроме того, наличие дополнительного преобразователя пара 1лелыюго кода 8-4-2-1 увеличивает объем оборудования за счет вентилей И и ИЛИ, входящих в состав дополнительного кодопреобразователя. Цель предлагаемого изобретения - повышение надежности за счет сокращения количества элементов. Для этого в известный преобразователь 1 параллельного двоично-десятичного кода 8-4-2-1 в частоту, содержащий генератор импульсов, выход которого пЬдкйючен ко входу триггерного счетчика, две вентилей И и три элементй ИЛЯ, допшнительно введены дифференцирующие эле-; менты, десятичный делитель и элемент зейержки, причем сигнальные входы венtHheA И нервой и второй группы соединеяь1 параллельно и подключены через диф- ферендирующие элементы к выходам соот ветству щйх разрядов Tp«rrep®Wc«ieTчика, а выходы вентилей И первой irpynrtbi п6дкл16чёньг Через перрыЙ элемент ИЛИ к первому входу второго элемента ИЛИ, В1торой вход которого соединен через пос- лёдовательно соединенные элемент задержки, десятичный делитель и третий элемент ИЛИ с выходом вентилей И второй группы. На чертеже представлена структурная схема преобразователя. ГТреобразОватепь содержит генератор 1 импульсов, триггерный счетчик 2, вйлючак)щий в себя последовательно с6единен« . ные триггеры 3, 4, В, 6 диф рёнцирую щие элементы 7, 8, 9, 10, подключенные к выходам триггеров З-гб соответственно первую группу вентилей И 11, состоящую из вентилей И-12-г15 и образующую старшую тетраду с элементами ИЛИ 16 под- ключенным к выходам вентилей И первой группы , вторую группу вентилей И 17, включающую в себя вентили И 18т 21 и образующие младщую тетраду с элементом ИЛИ 22, десятичный делитель 23, элемент задержки 24 элемент ИЛИ 25. Устройство работает следующим обра... -...,,„.,...,.,..... . На управляющие входы вентилей И стар щей тетрады. 124-15 и младшей тетрады - 18т-21 подается двоичног-десятичный код А 2 4 2 3 4. бУ венный индекс А относится к старшей тетраде, а буквенный индекс В относится к младшей тетраде (цифровой индекс 1 обозначает старщий разряд внутри каждой тетрады). Импульсы генератора 1 посту- пают на вход счетчт а 2. На выходах триггеров триггерного счетчика 2 образуются икя1ульсы, частоты которых относятся между собой как 8 : 4 : 2 : 1 Сигнальные входы кодовых вентилей И, относящихся .к одинаковым цифровым индексам входного кода, соединены между собой параллельно и подключены к соответ ствующим выходам дифференцирующих элементов 7.--10. Выходные Hsmyflbcbi кодовых вентилей И тетрады 11 суммируются элементом ИЛИ старшей 71 44 тетрады 16, при этом частота импул1:юов на выходе элемента ИЛИ 16 определится выражением . (1) Где FO - частота генератора импульсов 1, Выходные импульсы вентилей И 187-21 младшей тетрады 17 суммируются элементом ИЛИ младшей тетрады 22 и далее поступают на вход десятичного делителя 23. Импульсы на выходе десятичного делителя 23 имеют частоту vU.) . , Элемент 24 задорж {;и задерживает импульс младшей тетрады на время, необходимое для устранения совпадения импульсов выходов младшей и старшей тетрад, эле- мент ИЛИ 25 суммирует эти импульсы. Таким образом, описанное устройство преобразует двоично-десятш ный код 84-2-1 в выходную частоту, пропорциональ ную числу, представленную этим кодом. согласно вьфажению: -dfeW A-4A2-2A.Aj. -hC6B -v4V2V), где и могут принимать значение О, либо 1. Описанный преобразователь содеришт в два раза меньше корпусов микросхем, чем устройство, описанное в 2 и соответственно более экономичен и прост. Формула изобретения Преобразователь параллельного двоичню-дЪсятичного кода 8-4-2-1 в частоту, содержащий генератор и.мпульсов, выход которого подключен ко входу триггерного счетчика, две группы вентилей И и три элемента ИЛИ, отличающийся тем, что, с целью повьпиения надежности в него дополнительно введены дифференцирующие элементы, десятичный делитель и элемеет задержки, причем сигнальные входы вентилей И первой и второй группы соединены параллельно и подключены че.рез дифференцирующие элементы к выходам соответствующих разрядов триггерного счетчика, выходы вентилей И первой группы подключены через первый элемент ИЛИ к первому входу второгх элемента ИЛИ,

Авторы

Даты

1980-02-05—Публикация

1977-06-22—Подача