(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

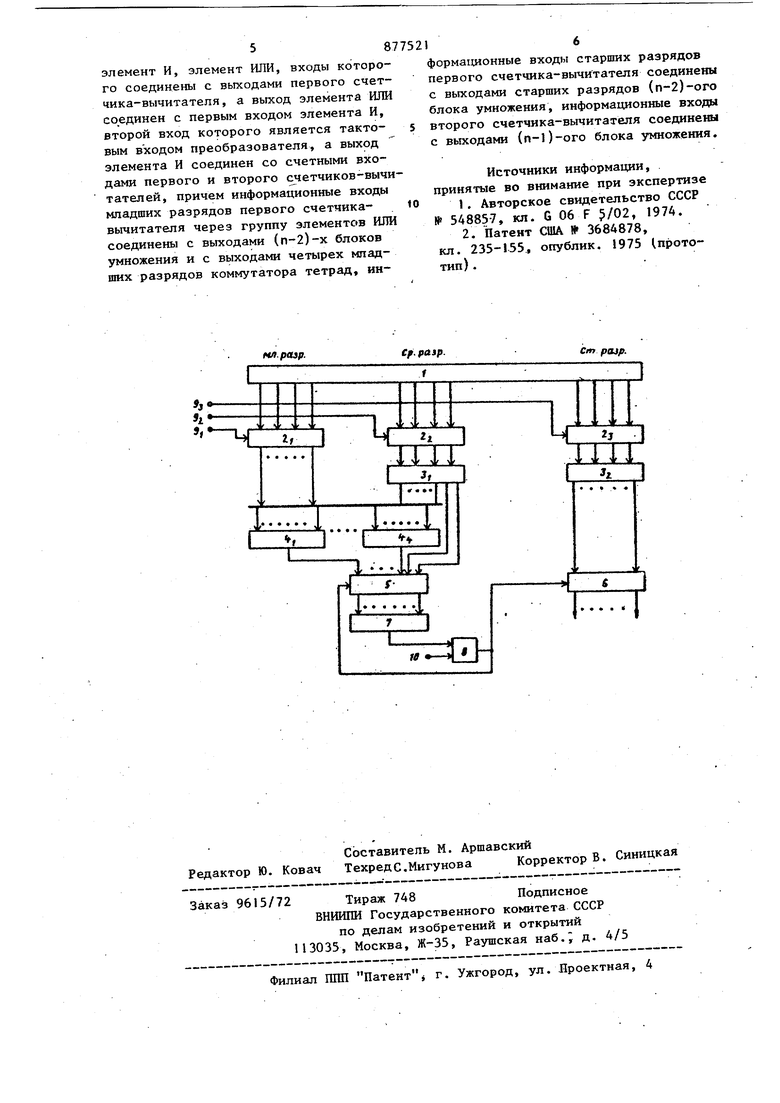

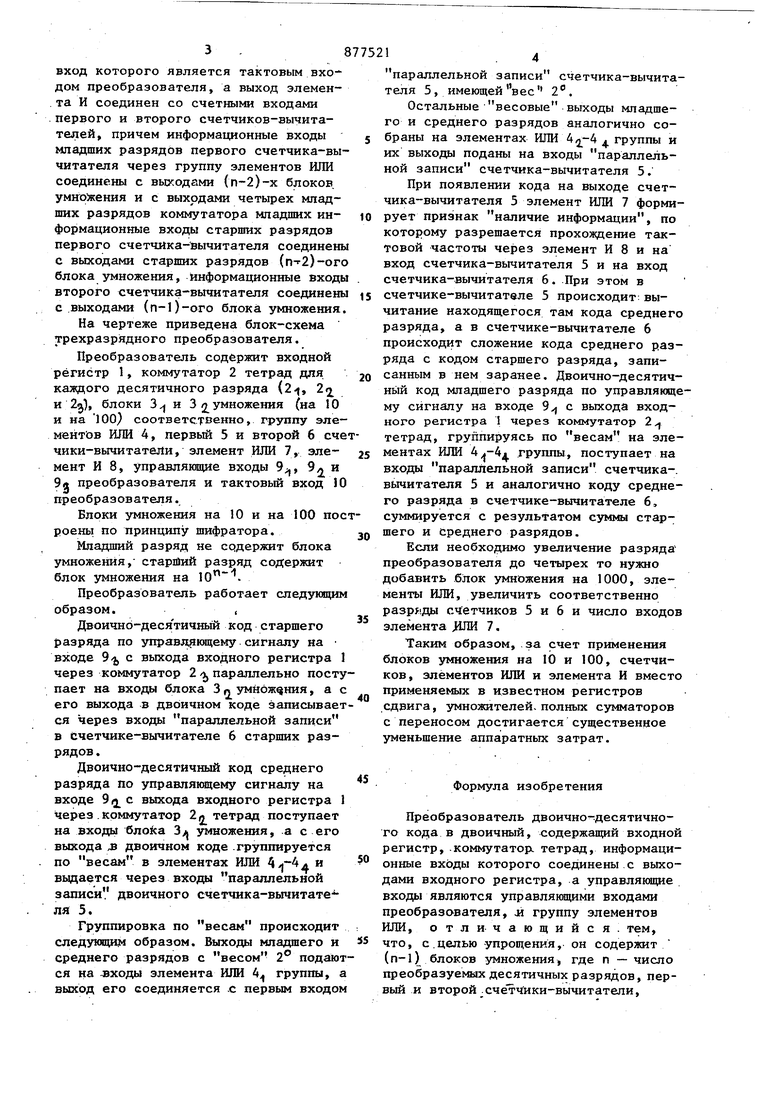

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоичнодесятичных преобразователей. Известен преобразователь двоичнодесятичного кода в двоичный, содержащий входной регистр, коммуд-атор тетрад, блок хранения эквивалентов и накопительный- сумматор ОНедостаток.данного преобразователя состоит в большом объеме аппаратуры, связанном с наличием полноразрядного сумматора.. Наиболее близким к предлагаемому п технической сущности является преобра зователь двоично-десятичного кода в двоичный, содержащий входной регистр, коммутатор тетрад, информационные вхо ды которого соединены с выходами входного.регистра, а управляющие входы являются управляющими входами преобразователя, и группу элементов ИЛИ. iKpoMe того, он содержит группу регистров сдвига и группу двоичных .сумматоров 12. Недостаток данного преобразователя состоит в большомОбъеме аппаратуры , связанном с наличием группы регистров сдвига и группы двоичных сумматоров. Цель изобретения -. упрощение преобразователя. Поставленная цель достигается тем, что Преобразователь Двоично-десятичного кода в;двоичный, содержащий входной .регистр, коммутатор тетрад, информационные входы которого соединены с выходами входного регистра, а управляющие входы являются управляющими входами преобразователя, и группу элементов ИЛИ, содержит (n-l) блоков умножения, где п - число преобразуемых десятичных разрядов, первый и второй счетчики-вычитатели, элемент И, элемент ИЛИ, входы которого соединены с выходами первого счетчика-вычитателя, а выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого является тактовым входом преобразователя, а выход элемен.та И соединен со счетными входами первого и второго счетчиков-зычитателей, причем информационные входы младших разрядов первого счетчика-вы читателя через группу элементов ИЛИ соединены с выходами (п-2)-х блоков, умножения и с выхрдг1МИ четырех младших разрядов коммутатора младших информационные входы старших разрядов первого счетчйка-вычитателя соединены с выходами старших разрядов (п-г2)-ого блока умножения, информационные входы второго счетчйка-вычитателя соединены с выходами (n-l)-oro блока умножения На чертеже приведена блок-схема трехразрядного преобразователя. Преобразователь содерлят входной регистр 1, коммутатор 2 тетрад для каждого десятичного разряда (2-), 2 и 2а), блоки 3 и Sj умножения (на 10 и на 100) соответственно, группу элементьв ИЛИ 4, первый 5 и второй 6 сче чики-вычитатеЛи, элемент ИЛИ 7, элемент И 8, управляющие входы 9;,, 9 и 9rt преобразователя и тактовый вход Ш преобразователя. Блоки умножения на 10 и на 100 пос роень по принципу шифратора. Младший разряд не содержит блока умножения,- старший разряд содержит блок умножения на . Преобразователь работает следующим образом.( Двоично-десятичный код старшего разряда по ущ)авл;якндему сигналу на входе 9 с выхода входного регистра через коммутатор 2 /jj параллельно посту пает на входа блока 3 п умножения, а его выхода в двоичном коде записывае ся через входы параллельной записи в счетчике-вычитателе 6 старших разрядов . Двоично-десятичный код среднего разряда по управляющему сигналу на входе выхода входного регистра через.коммутатор 2л тетрад поступает на входы блойа Зу| умножения, .а с его выхода л двоичном коде .группируется по весам в элементах ИЛИ и вьщается через входы параллельной записи двоичного счетчика-вычитателя 5. Группировка по весам происходит следукяцим образом. Выходы младшего и среднего разрядов с весом 2° подаю ся на Jзxoды элемента ШШ 4 группы, выход его соединяется .с первым входо параллельной записи счетчйка-вычитателя 5, имеющей вее 2. Остальные весовые выходы младшего и среднего разрядов аналогично собраны на элементах ИЛИ А -4 j группы и их выхода поданы на входы параллельной записи счетчйка-вычитателя 5. При появлении кода на выходе счетчйка-вычитателя 5 элемент ИЛИ 7 формирует признак наличие информации, по которому разрешается прохождение тактовой частоты через элемент И 8 и на вход счетчйка-вычитателя 5 и на вход счетчйка-вычитателя 6. При этом в счетчике-вычитателе 5 происходит: вычитание находящегося там кода среднего разряда, а в счетчике-вычитателе 6 происходит сложение кода среднего разряда с кодом старшего разряда, записанным в нем заранее. Двоично-десятичный код младшего разряда по управляющему сигналу на входе 9 с выхода входного регистра I через коммутатор 2 тетрад, группируясь по весам на элементах ШЖ 4 -4i группы, поступает на входы параллельной записи счетчика-, вычитателя 5 и аналогично коду среднего разряда в счетчике-вычитателе 6, суммируется с результатом суммы старшего и среднего разрядов. Если необходимо увеличение разряда преобразователя до четырех то нужно добавить блок умножения на 1000, элементы ИЛИ, увеличить соответственно разряды счетчиков 5 и 6 и число входов элемента ДЛИ 7. Таким образом, за счет применения блоков умножения на 10 и 100, счетчиков, элементов ИЛИ и элемента И вместо применяемых в известном регистров сдвига, умножителей, полных сумматоров с переносом достигается существенное уменьшение аппаратных затрат. Формула изобретения Преобразователь двоично-.десятичното кода в двоичный, содержащий входной регистр,.коммутатор1 тетрад, информационные входы которого соединены с выходами входного регистра, а управлякицие входы являются управляющими входами преобразователя, м группу элементов ИЛИ, отличающийся, тем, что, с.целью упрощения, он содержит (n-l) блоков умножения, где п - число преобразуе1«ях десятичных разрядов, первый и второй счетчики-вычитатели. элемент И, элемент ИЛИ, входы которого соединены с выходами первого счетчика-вычитателя, а выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого является тактовым входом преобразователя, а выход элемента И соединен со счетными входами первого и второго счетчиков-вычитателей, причем информационные входы младших разрядов первого счетчикавычитателя через группу элементов ИЛИ соединены с выходами (п-2)-х блоков умножения и с выходами четырех младших разрядов коммутатора тетрад, ин87форма1шонные входы старших разрядов первого счетчика-вычитателя соединены с выходами старших разрядов (п-2)-ого блока умножения, информационные входы второго счетчика-вычитателя соединены с выходами {n-l)-oro блока умножения. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 54885-7, кл. G 06 F /02, 1974. 2. Патент США 3684878, кл. 235-155, опублик. 1975 (прото тип) .

Авторы

Даты

1981-10-30—Публикация

1979-08-24—Подача