(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU721828A1 |

| Множительное устройство | 1976 |

|

SU616636A1 |

| Устройство для умножения | 1973 |

|

SU480086A1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| Множительно-делительное устройство | 1978 |

|

SU723596A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU886009A1 |

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

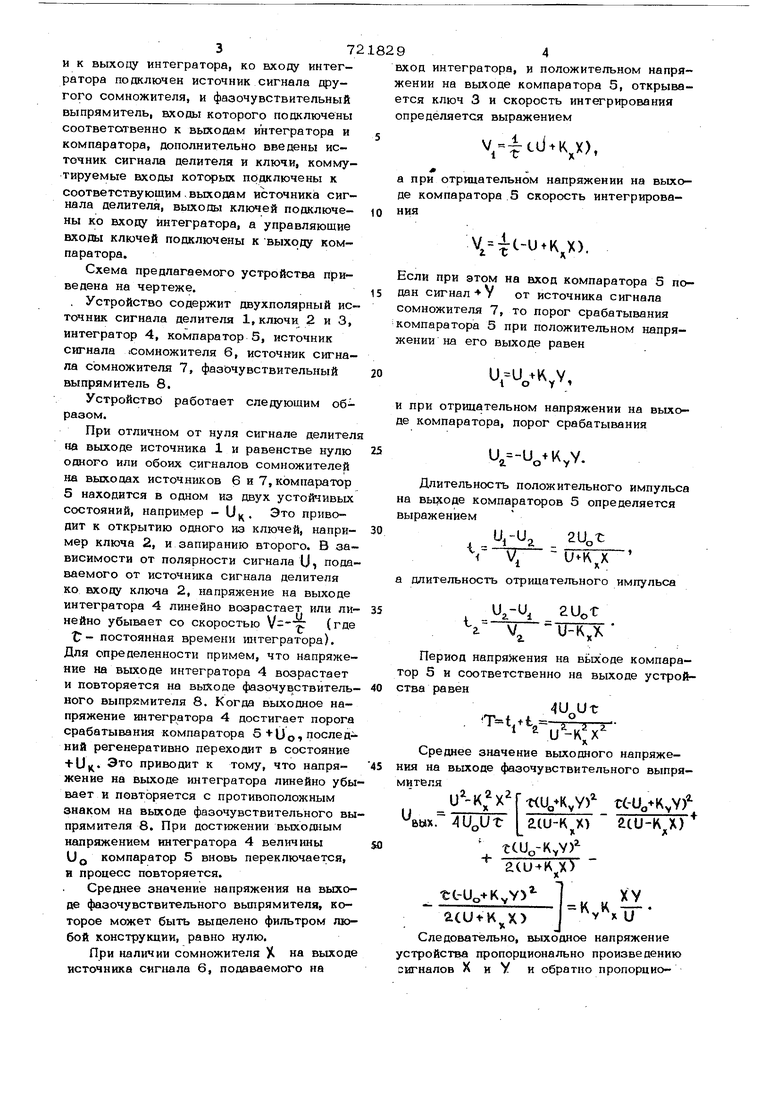

Изобретение относится к области вычислительной технуши и может быть испол зовано в аналоговых вычислительных машинах, устройствах автоматики и измерительной техники, а также в ряде других устройств, в которых необходимо проводить одибвременно операции умножения и деления. Известны устройства для одновременно го вьтолнения операций умножения и деления, содержащие широтно-импульсный и амплитудный модулятор Ql Однако этк устройства имеют существенные недостатки; при работе требуется введение гальванической развязки между цепями щиротно-импульсного и амплитудных модуляторов и повышенная мощность потребления от источника сигнала сомножителя, подключенного ко входу амплитуд ного мосулятора. Наиболее близким техническим решени ем является устрюйство для умножения 2, содержащее источники сигналов сомножителей, компаратор, интегратор и фазочувствительный выпрямитель, входы которого подключены к выходам интегратора и компаратора, входы компаратора подключены к выходам интегратора и источника сигнала одного из сомножителей, а выход источника сигнала фугого сомножителя подключен ко входу интегратора. Это устройство позволяет получать раздельно произведение входных сигналов и частное от деления при включении его в обратную связь операционного усилителя, но не позволяет одновременно выполнять операции умножения и деления. Это ограничивает его функциональные возможности и сужает область применения. Целью изобретения является расширение функциональных возможностей устройства за счет одновременного выполнения операций умножения и деления. Поставленная цель достигается тем, что в устройство, содержащее источники сигналов сомножителей, интегратор, компаратор, вход которого подключен к источнику сигнала одного из сомножителей и к выходу интегратора, ко входу интегратора подключен источник сигнала другого сомножителя, и фаэочувствительный выпрямитель, входь которого подключены соответатвенно к выходам интегратора и компаратора, дополнительно введены источник сигнала делителя и ключи, коммутируемые входы которых подключены к соответствующим .выходам источник/а сигнала делителя, выходы ключей подключены ко входу интегратора, а управляющие входы ключей подключены к выходу компаратора, Схема предлагаемого устройства приведена на чертеже. . Устройство содержит двухполярный источник сигнала делителя 1, ключи 2 и 3, интегратор 4, компаратор 5, источник сигнала сомножителя б, источник сигнала сомножителя 7, фаз&чувствительный выпрямитель 8. Устройство работает следующим образом. При отличном от нуля сигнале делител вд выходе источника 1 и равенстве нулю одного или обоих сигналов сомножителей на выходах источников 6 и 7, ком пара тор 5 находится в одном из двух устойчивых состояний, например - U . Это приводит к открытию одного из ключей, например ключа 2, и запиранию второго. В зависимости от полярности сигнала U пода ваемого от источника сигнала делителя ко входу ключа 2, напряжение на выходе интегратора 4 линейно возрастает или линейно убывает со скоростью V-f (где f- постоянная времени интегратора). Для определенности примем, что напряжение на выходе интегратора 4 возрастает и повторяется на выходе фазрчувствитель ного выпрямителя 8. Когда выходное напряжение интегратора 4 достигает порога срабатывания компаратора 5 U о Д НИИ регенеративно переходит в состояние hU. Это приводит к тому, что напряжение на выходе интегратора линейно убы вает и повторяется с противоположным знаком на выходе фазочувствительного вы прямителя 8. При достижении выходным напряжением интегратора 4 величины и о компаратор 5 вновь переключается, и процесс повторяется. Среднее значение напряжения на выхо де фазочувствительного выпрямителя, которое может быть выделено фильтром лю бой конструкции, равно нулю. При наличии сомножителя X на выход источника сигнала 6, подаваемого на д интегратора, и положительном напрянии на выходе компаратора 5, открывая ключ 3 и скорость интегрирования еделяется выражением .), при отрицательном напряжении на выхокомпаратора 5 скорость интегрироваяV %C-UtK X). ли при этом на вход компаратора 5 пон сигнал «V от источника сигнала множителя 7, то порог срабатывания мпаратора 5 при положительном напрянии на его выходе равен , при отрицательном напряжении на выхокомпаратора, порог срабатывания ,+ к,у. Длительность положительного импульса выходе компараторов 5 определяется ражением Ц-и,, длительность отрицательного импульса 2Uoi: и-к,х Период напря)кения на вьисоде компараор 5 и соответственно на выходе устройтва равен 4U и-с .Среднее значение выходного напряжеия на выходе фазочувствительного выпряителяtC-Up KyVr X I ьыхГ еси-к X) AU(Jt аш-к/) tCUo-K Y) trC-UpfKyV)2( Следовательно, выходное напряжение стройства пропорционально произведению игналов X и Y и обратно пропорцио

Авторы

Даты

1980-03-15—Публикация

1978-09-27—Подача